ECE 3450 Digital Electronics - Department of Electrical and

advertisement

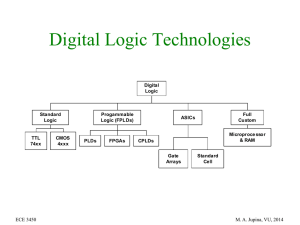

Villanova University Department of Electrical and Computer Engineering ECE 3450 Digital Electronics Spring 2016 Dr. Mark A. Jupina 430 Tolentine Hall (610) 519 – 7561 mark.jupina@villanova.edu Office Hours: T, Th 9 AM – Noon, or By Appointment ECE 3450 M. A. Jupina, VU, 2016 ECE 3450 Course Rationale Provide our students with additional experience in prototyping and troubleshooting digital board-level and on-chip applications. Students gain additional hardware experience before the implementation of their senior capstone project. ECE 3450 M. A. Jupina, VU, 2016 Entrepreneurship Exposure One set of exercises this semester will involve developing an entrepreneurial mindset. In this set of exercises, a group of students will identify a business opportunity, investigate the market, and create a preliminary business model for a digitally-based sensor technology. Rationale: Most graduates will become intrapreneurs, creating value through existing organizations. Thereby, the entrepreneurial mindset has value for every engineering grad. ECE 3450 M. A. Jupina, VU, 2016 Introduction • Syllabus • Practicums and Projects ECE 3450 M. A. Jupina, VU, 2016 Syllabus COURSE WEB SITE http://www.ece.vill.edu/~jupina/ece3450/index.htm COURSE OBJECTIVES To understand the properties of digital systems. To understand how to use computer aided simulation tools to design, analyze and synthesize digital circuits. To understand how to prototype and troubleshoot board-level and on-chip applications and designs involving timers, serial and parallel data circuits, analog/digital conversion circuits, and field programmable logic device circuits. TEXTBOOK Brown and Vranesic, Fundamentals of Digital Logic with VHDL Design, 2nd or 3rd ed., McGrawHill. ADDITIONAL REFERENCES 1. Tocci, Widmer, and Moss Digital Systems, Principles and Applications, Prentice Hall, 2007. 2. Hamblen, Hall, and Furman, Rapid Prototyping of Digital Systems, SOPC Edition, Springer, 2008. ECE 3450 M. A. Jupina, VU, 2016 Syllabus OFFICE HOURS Please do not hesitate to meet with me if you are having difficulty with any of the material in the course. Besides the posted office hours, I am more than willing to meet with you at another mutually convenient time. GRADING The final grade will be determined as follows. Assignments: Electronic Lab Notebook and Lab Performance: 1 Lab Report: Mid-Term Exam Lab Final Exam ECE 3450 20 % 20 % 20 % 20 % 20 % M. A. Jupina, VU, 2016 Syllabus EXAMS Two exams will be given during the semester. A mid-term exam and a final lab exam will be given. The exams will be based on projects throughout the semester and will include material from the lectures, assignments, textbook, and practicums. ATTENDANCE Attendance is required for all practicums and will be taken via an attendance sheet. Permission for an excused absence from a session will be granted only for the most serious personal emergency. It is solely your responsibility to schedule with the TA a time to make up work of any excused absence session. Most importantly, you are NOT permitted to use your partner's results should you miss a practicum session for any reason. For each unexcused practicum absence, your final grade will be lowered by 5 points. RULES OF CONDUCT Serious violations include late arrival; unsafe practices; eating food, drinking a beverage, or chewing gum in the laboratory; unauthorized or recreational use of computers or cell phones; and misuse or abuse of equipment. A serious violation or repeated minor violations of any rule will result in a deduction of 5 points from the final grade per offense. ECE 3450 M. A. Jupina, VU, 2016 Syllabus ASSIGNMENT DEADLINES The submission deadlines of assignments and lab reports will be announced by the instructor. Pre-lab assignments will be collected before the start of the practicum only and will not be accepted after this time period. These assignments are meant to prepare you for each lab session. A late submission of a lab report or non-pre-lab assignments will be assessed a 33% penalty per business week. ELECTRONIC NOTEBOOK You are required to maintain an electronic notebook for lab. All entries into the notebook are to be recorded as the measurements are performed. Various software tools, such as Microsoft Word, Excel, and PowerPoint, Matlab, and Quartus II, will be used to create the electronic work (Cntl-Print Screen can be used to capture the work). Each page of the notebook is to be dated and numbered, and an index at the beginning of the notebook should be created. Prelab assignments, calculations, simulations, circuit diagrams, data (tables and graphs), observations, and conclusions are to be recorded in this electronic notebook. The final version of the electronic notebook will be an Adobe PDF file (pdf only, no word doc files accepted) submitted via Blackboard Learn to the instructor by the due date given at the end of the semester. ECE 3450 M. A. Jupina, VU, 2016 Syllabus TOPICS 1. Properties of Digital Systems 2. MOS Digital Logic Circuits 3. Programmable Logic Technologies and VHDL 4. Clocks, Schmitt Triggers, 555 Timers, and One-Shots 5. A/D and D/A Conversion 6. State Machines 7. Memory 8. Data Buses and Data Paths Practicum projects will involve the application of the above topics. ECE 3450 M. A. Jupina, VU, 2016 Syllabus Digital Design Projects Buses, Clocks, Memory, and FSMs Properties of Digital Circuits Synthesis and Simulation Software Design ECE 3450 Simulation Prototyping Testing M. A. Jupina, VU, 2015 Syllabus ECE PROGRAM EDUCATIONAL OBJECTIVES IN THIS COURSE FOR ABET a) b) c) e) g) k) ECE 3450 an ability to apply knowledge of mathematics, science, and engineering. an ability to design and conduct experiments, as well as to analyze and interpret data. an ability to design a system, component, or process to meet desired needs. an ability to identify, formulate, and solve engineering problems. an ability to communicate effectively. an ability to use the techniques, skills, and modern engineering tools necessary for engineering practice. M. A. Jupina, VU, 2016 Syllabus It is the policy of Villanova to make reasonable academic accommodations for qualified individuals with disabilities. If you are a person with a disability (non-physical) please register with the Learning Support Office by contacting Learning.support.services@villanova.edu or 610-519-5176 as soon as possible. Registration is needed in order to receive accommodations. The Office of Disability Services collaborates with students, faculty, staff, and community members to create diverse learning environments that are usable, equitable, inclusive and sustainable. The ODS provides Villanova University students with physical disabilities the necessary support to successfully complete their education and participate in activities available to all students. If you have a diagnosed disability and plan to utilize academic accommodations, please contact Gregory Hannah, advisor to students with disabilities @ 610-519-3209 or visit the office on the second floor of the Connelly Center. ECE 3450 M. A. Jupina, VU, 2016 Syllabus As part of this course you are to complete the College of Engineering Professional Development (PD) requirements which are detailed here: http://www1.villanova.edu/villanova/engineering/undergrad/pr ofessionaldevelopment/juniorDetails.html ECE 3450 M. A. Jupina, VU, 2016 Some Examples of Practicums and Projects ECE 3450 M. A. Jupina, VU, 2016 Properties of Digital Circuits V DD 74LS04 and CD4069 Gnd ECE 3450 M. A. Jupina, VU, 2016 Properties of Digital Circuits PART I: Voltage Transfer Characteristics and Noise Margins chan 1 74LS04 ECE 3450 chan 2 CD4069 M. A. Jupina, VU, 2016 Properties of Digital Circuits PART II: Power Supply Current and Power Dissipation VDD ISUPPLY C Power (mW) 10 1 LSTTL CMOS 0.1 0.01 0.001 1.00E+03 1.00E+04 1.00E+05 1.00E+06 Frequency (Hz) ECE 3450 M. A. Jupina, VU, 2016 Properties of Digital Circuits PART III: Average Propagation Delay Time and Power-Delay Product channel 1 74LS04 ECE 3450 CD4069 M. A. Jupina, VU, 2016 Layout of a CMOS Circuit Microwind CAD Generated Drawing ECE 3450 “Stick” Drawing in Power Point M. A. Jupina, VU, 2016 The Altera DE2 Development Board Figure 1.2 The Altera DE2 FPGA Development board. ECE 3450 M. A. Jupina, VU, 2016 SignalTap II Embedded Logic Analyzer (Altera DE2 Board) ECE 3450 M. A. Jupina, VU, 2016 Required Installation of Quartus II on Laptops • Go to the studentpublic drive on the \\egrstorage network, find the altera folder, and download the executable file 91_quartus_free to your laptop’s hard drive. Install the Quartus II software. The Quartus software can also be found on the facultypublic-sa drive on the \\egrstorage network under the ece3450 folder. • Version 9.1 has a built-in simulation tool. Versions 10 and later require the use of a third party simulation tool, such as ModelSim. • After Installation, run the Quartus II software. Go to the menu Tools, License Setup, and in the box for License File put the following 5282@153.104.46.90 so that your laptop can find the license on the ECE server. ECE 3450 M. A. Jupina, VU, 2016 Design Process for Schematic or VHDL Entry ECE 3450 M. A. Jupina, VU, 2016 Quartus II Tutorial ECE 3450 M. A. Jupina, VU, 2016 Entrepreneurial Product Design Sensor Interface Digital Platform Wireless or Wired? I2C, SPI, RS-232C, or GPIO? Laptop, Tablet, Phone Transducer Mechanism? Android, Apple, Arduino, Specifications: BeagleBoard, PandaBoard, Analog or Digital Output FPGA (Altera or Xlinx), Data Rate Raspberry Pi, etc? Power Requirements Background on Digital Platforms: http://www.mathworks.com/hardware-support/home.html?s_tid=hp_mi_hwsupport_0913 ECE 3450 M. A. Jupina, VU, 2016 Capacitance Sensor Project Sports Applications Tank Application a 2 eff C H ln b a H d b A C r o d variable frequency or period OUTPUT 0 - 99 7-segment displays or Figure 1.2 The Altera DE2 FPGA Development board. 555 Timer ECE 3450 M. A. Jupina, VU, 2016 Sonar Sensor Project (Module Interfaced to a Simple Processor on the Altera Board) • Polaroid sensor range is six inches to 35 feet • 16 cycles at 49KHz • Listen for return pattern • Sound travels ~0.9 ms/ft • Timer and Decoder on DE2 determines distance • ALU determines speed ECE 3450 Sensor M. A. Jupina, VU, 2016 Block Diagram of Sonar Sensor Project SONAR SYSTEM PROCESSOR Data Request FSMs Data Bus Registers ALU ECE 3450 Data Ready Y-bits DATA Sonar Circuit M. A. Jupina, VU, 2016