Lecture Slides

advertisement

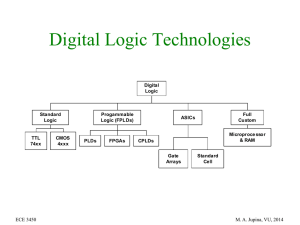

Altera DE2 Board and Quartus II Software ECE 3450 M. A. Jupina, VU, 2014 Lecture Objective An overview of the Altera DE2 board and the Quartus II software. Course projects will use the Altera FPLD boards as a platform to implement complicated digital systems. With the Quartus II software, you will use a system design approach to create your designs. References: 1. Fundamentals of Digital Logic, Sections 2.9, 2.10, 3.5 – 3.7, and Appendices A-E. 2. Document files at the course web site ECE 3450 M. A. Jupina, VU, 2012 The Altera DE2 Development Board Figure 1.2 The Altera DE2 FPGA Development board. ECE 3450 M. A. Jupina, VU, 2012 In-System Programming of the Altera Development Board ECE 3450 M. A. Jupina, VU, 2012 Connections Between the Pushbuttons, the LEDs, and the Altera FPGA Figure 1.6 FPGA I/O connections to Pushbuttons (PBx) and LED: Right of center, active LOW LED output (i.e., UP1 and UP2 boards) or on far right active HIGH LED output (i.e., DE1, DE2, and UP3 boards). Note that a depressed pushbutton input will be LOW. ECE 3450 M. A. Jupina, VU, 2012 9V DC Power Supply Connector USB Blaster Port USB Device Mic In USB Host Mic Out Line In 24-bit Audio CODEC Power ON/OFF Switch XSGA Video Port Video In Ethernet 10/100M Port RS-232 Port 27Mhz Oscillator XSGA 10-bit DAC USB Host/Slave Controller PS/2 Port Ethernet 10/100M Controller TV Decoder (NTSC/PAL) Altera EPCS 16 Configuration Device Altera USB Blaster Controller Chipset 50Mhz Oscillator RUN/PROG Switch for JTAG/AS Modes 90nm Cyclone II FPGA with 35K LEs LCD 16x2 Module 8MB SDRAM 7-SEG Display Module 88 88 512KB SRAM SD Card Connector 1MB Flash Memory (upgradable to 4MB) 88 88 18 Red LEDs 8 Green LEDs IrDA Transceiver SMA Ext Clk 18 Toggle Switches 4 Push-button Switches Figure 1.16 Altera DE2 board showing the Pushbutton and LED locations used in design (enclosed in dashed ellipses seen in bottom right). ECE 3450 M. A. Jupina, VU, 2012 Examples of Dedicated Pin-Outs on the DE2 Cyclone II Chip Table 1.2 Hardwired I/O connections on the various FPGA boards in the design example. I/O Device DE1 Pin DE2 Pin UP3 Pin UP2 & 1 Pin PB1 R21 (Key1) N23 (Key1) 62 (SW7) 28 (FLEX PB1) PB2 T22 (Key2) P23 (Key2) 48 (SW4) 29 (FLEX PB2) LED R20(LEDR0) AE23(LEDR0) 56 (D3) 14 (7Seg Dec. pt.) ECE 3450 M. A. Jupina, VU, 2012 Required Installation of Quartus II on Laptops • Go to the studentpublic drive on the \\egrstorage network, find the altera folder, and download the executable file 91_quartus_free to your laptop’s hard drive. Install the Quartus II software. The Quartus software can also be found on the facultypublic-sa drive on the \\egrstorage network under the ece3450 folder. • Version 9.1 has a built-in simulation tool. Versions 10 and later require the use of a third party simulation tool, such as ModelSim. • After Installation, run the Quartus II software. Go to the menu Tools, License Setup, and in the box for License File put the following 5282@153.104.46.90 so that your laptop can find the license on the ECE server. ECE 3450 M. A. Jupina, VU, 2016 Design Process for Schematic or VHDL Entry Figure 1.2 The Altera DE2 FPGA Development board. ECE 3450 M. A. Jupina, VU, 2014 Design Implementation Methodology Create/Edit Schematic/VHDL Compiler repeat until no errors Create Simulation Waveforms Simulator Run simulation until functionally correct Timing Analysis? Modify design until timing specs are met Program Device ECE 3450 M. A. Jupina, VU, 2014 Creating a New Quartus II Project ECE 3450 M. A. Jupina, VU, 2014 Setting the FPGA Device Type DE2 Cyclone II EP2C35F672C6 Figure 1.9 Setting the FPGA Device Type. Settings shown are for the DE1 board. The Cyclone II Chip resides on the DE2 Board. ECE 3450 M. A. Jupina, VU, 2014 Creating the Top-Level Project Schematic Design File ECE 3450 M. A. Jupina, VU, 2014 Selecting a New Symbol with the Symbol Tool ECE 3450 M. A. Jupina, VU, 2014 Active Low OR-Gate Schematic Example with I/O Pins Connected ECE 3450 M. A. Jupina, VU, 2014 Assigning Pins with the Assignment Editor ECE 3450 M. A. Jupina, VU, 2014 Active Low OR-Gate Timing Simulation with Time Delays ECE 3450 M. A. Jupina, VU, 2014 VHDL Entity Declaration Text ECE 3450 M. A. Jupina, VU, 2014 VHDL OR-Gate Model (with Syntax Error) ECE 3450 M. A. Jupina, VU, 2014 VHDL Compilation with a Syntax Error ECE 3450 M. A. Jupina, VU, 2014 Timing Analyzer Showing Input to Output Timing Delays ECE 3450 M. A. Jupina, VU, 2014 Floorplan View Showing Internal FPGA Placement of ORGate in LE and I/O Pins ECE 3450 M. A. Jupina, VU, 2014 ORgate Design Symbol orgate PB1 LED PB2 inst ECE 3450 M. A. Jupina, VU, 2014 Implementation of a Simple Processor Bus Clock IEA RA IEB RB IEC RC IEX RX Data SDATA SA SB SC SY Start ECE 3450 State Machine ALU Multiplexer IEA IEB IEC IEX IEY SDATA SA SB SC SY AddSub Done IEY AddSub RY M. A. Jupina, VU, 2014 Altera Implementation of Simple Processor ECE 3450 M. A. Jupina, VU, 2014 An Example Design Illustrating the Mapping of Multi-Bit Connections ECE 3450 M. A. Jupina, VU, 2014 An Example with a LPM Device ECE 3450 M. A. Jupina, VU, 2014 Lpm_counter0 MegaWizard Edit Window ECE 3450 M. A. Jupina, VU, 2014