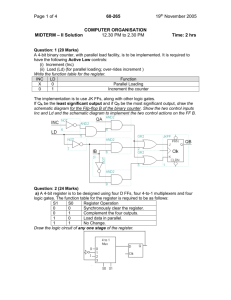

midterm test 2 (60-265)

advertisement

MIDTERM TEST 2 (60-265) Saturday, 23 March 2002 Student’s Name: Student Number: Time: 3.30 pm to 5.30 pm (2 hrs) Seat Number Q.1 (a) The content of a 4-bit shift register is initially 1101. It is shifted to the right six times with the serial input being 101101. What is the content of the register after each shift? (b) Show the external connections necessary to construct a 64K X 8 ROM by using the following components: 4 number 16K X 8 ROM chips, each with its Enable input. 1 number 2-to-4 Decoder (c) Represent the following conditional control statement by two register transfer statements with control functions: if (P = 1) then (R1 R2); else if (Q = 1) then (R1 R3) (d) Register A holds the 8-bit binary number 11011001. For each of the following two cases, determine the B operand and the logic micro-operation to be performed in order to change the value in A to (i) (ii) 01101101 11111101 (20 Marks) Q.2 Draw the logic diagram of a 2-to-4 line decoder with only NOR gates. Include an enable input. Give the truth table of the decoder. (15 Marks) Q.3 A 4-bit binary counter has the following controls: Synchronous Parallel loading Increment Draw its block diagram showing only all the inputs and outputs. Show how an AND gate and an INVERTER can be used to convert the 4-bit binary counter to a divide-by-12 counter. (10 Marks) Q.4 a) An 8-bit register R contains the binary value 10011100. Determine the sequence of binary values in R in each of the following four cases: after – an arithmetic shift right; followed by – a logical shift-left; followed by – a circular shift-right; followed by – an arithmetic shift-left. Discuss whether the last operation of arithmetic shift left leads to a multiplication by 2 or not. b) A 4-line common bus system is to be constructed for data transfer from four 4bit registers P, Q, R and S. Use 4 x 1 multiplexers to construct the system. Draw the bus system, showing the four bus lines clearly. (25 Marks) Q.5 A circuit is to provide the operations of addition and subtraction of two 4-bit operands. It should also provide the facility of incrementing to one of the two operands. Use XOR gates, 1-bit full-adders, a 4-bit counter with parallel-load and other necessary components to construct the circuit. Draw a neat circuit diagram and give the function table for the circuit. (30 Marks) ------------------------ 60-265 MIDTERM TEST 2 SOLUTION Q1 a) The content of a 4-bit counter is initially 1101. Serial input = 101101 We use the last 4 bits (1101) After 1st shift 1110 After 2nd shift 0111 After 3rd shift 1011 After 4th shift 1101 After 5th shift 0110 After 6th shift 1011 b) 14 Address A0 – A13 14 A14 A15 14 14 3 2 1 0 2 to 4 line decoder E Address E Address E Address Data Data Data 8 Data Lines 2^16 = 64k 2^14 = 16k c) 14 8 E Address Data 8 8 P: R1 R2 P’Q: R1 R3 d) (i) A = 11011001 B = 10110100 XOR ------------------011011101 (ii) A = 11011001 B = 00100100 OR ------------------11111101 Q2. 2-to-4 line decoder Truth table S1 0 0 1 1 S0 0 1 0 1 D0 1 0 0 0 D1 0 1 0 0 D2 0 0 1 0 D3 0 0 0 1 S1 S0 D0 D1 D2 D3 E S1 S0 S0’ S1’ D3 D2 D1 D0 E Q3 I0 D0 D1 D2 I1 I2 I3 4 Bit Binary Counter INR D3 Load 0 Clock Divide – by –12 counter Counts from 0000 to 1011 Q4 a) First Operation 10011100 Second Operation 11001110 Third Operation 10011100 Fourth Operation 01001110 Fifth Operation 10011100 The last operation leads to an OVERFLOW. Hence it does not lead to a multiplication by 2. b) 4-bit bus using MUX D0 D1 D2 D3 4 to 1 S0 S1 MUX 0 1 2 3 0 1 2 P 3 0 0 1 2 3 0 1 2 1 3 01 2 Q 2 R 3 3 0 1 2 3 0 1 2 S 3 Q5. Function Table C INR L F S D 0 0 1 B D+B D+B 1 0 1 B’ D- B D- B X 1 0 X X D+1 C Cin S0 I0 FA Co 4 bit Counter S1 D0 I1 D1 I2 Cin F0 B0 B1 B2 Register B B3 I3 D2 D3 FA INR Load F1 F2 F3 4 XOR GATES Co INR Cin FA Co Cin S2 S3 FA Co Unused 1 bit Full Adders L