Jaeger/Blalock 7/1/03

Chapter 3

Solid-State Diodes and Diode Circuits

Microelectronic Circuit Design

Richard C. Jaeger

Travis N. Blalock

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -1

Chapter Goals

• Understand diode structure and basic layout

• Develop electrostatics of the pn junction

• Explore various diode models including the mathematical model, the ideal diode model, and the constant voltage drop model

• Understand the SPICE representation and model parameters for the diode

• Define regions of operation of the diode (forward, reverse bias, and reverse breakdown)

• Apply the various types of models in circuit analysis

• Explore different types of diodes Discuss the dynamic switching behavior of the pn junction diode

• Explore diode applications

• Practice simulating diode circuits using SPICE

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -2

Diode Introduction

• A diode is formed by interfacing an n -type semiconductor with a p -type semiconductor.

• A

pn junction is the interface between n and p regions.

Diode symbol

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -3

PN Junction Animation

• Formation of PN Junction – applet

• PN Junction space charge profile and electric field – applet

• Biased PN Junction applet

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

pn

Junction Electrostatics

Donor and acceptor concentration on either side of the junction.

Concentration gradients give rise to diffusion currents.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -5

Drift Currents

• Diffusion currents lead to localized charge density variations near the pn junction.

• Gauss’ law predicts an electric field due to the charge distribution:

E

c

s

• Assuming constant permittivity,

E ( x )

1

s

( x ) dx

• Resulting electric field gives rise to a drift current. With no external circuit connections, drift and diffusion currents cancel. There is no actual current, since this would imply power dissipation, rather the

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -6

Space Charge Region Formation at the

pn

Junction

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -7

Potential across the Junction

Charge Density Electric Field Potential

j

E ( x ) dx

V

T ln

N

A

N n i

2

D

, V

T

kT q

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -8

Width of Depletion Region

Combining the previous expressions, we can form an expression for the width of the space-charge region, or depletion region. It is called the depletion region since the excess holes and electrons are depleted from the dopant atoms on either side of the junction.

w d 0

( x n

x p

)

2

s q

N

1

A

1

N

D

j

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -9

7/1/03

Width of Depletion Region (Example)

Problem: Find built-in potential and depletion-region width for given diode

Given data :On p -type side: N

A

=10 17 /cm 3 on n -type side: N

D

=10 20 /cm 3

Assumptions : Room-temperature operation with V

T

=0.025 V

Analysis:

j

V

T ln

N

A

N

D n i

2

(0.025

V)ln

10

17

/cm

10

20

3

10

/cm

20

6

/cm

3

0 .

979 V w d 0

2

q s

N

1

A

N

1

D

j

0 .

113

m

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -10

Diode Electric Field (Example)

• Problem: Find electric field and size of individual depletion layers on either side of pn junction for given diode

• Given data :On p -type side: N

A

=10 17 /cm 3 on n -type side: N

D

=10 20 /cm 3 from earlier example,

j

0 .

979 V w d 0

0 .

113

m

• Assumptions : Room-temperature operation

• Analysis: w d 0

x n

E

MAX

x n

w d x p

0

x n

1

N

N

D

A

1

2

w d j

N

0

N

D

A

2 ( 0 .

979 V )

0 .

113

m

x p

1 .

13

10

4 m

1

x p

N

N

173 kV/cm

A

D

1

w d

N

N

0

A

D

0 .

113

m

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -11

Internal Diode Currents

Mathematically, for a diode with no external connections, the total current expressions developed in chapter 2 are equal to zero. The equations only dictate that the total currents are zero. However, as mentioned earlier, since there is no power dissipation, we must assume that the field and diffusion current tendencies cancel and the actual currents are zero.

j n

T j

T p

q

n

q

p nE

qD n pE

qD p

n

x

p

= 0

x

= 0

When external bias voltage is applied to the diode, the above equations are

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -12

Diode Junction Potential for Different

Applied Voltages

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -13

Diode

i-v

Characteristics

Turn-on voltage marks point of significant current flow. I s reverse saturation current.

is called the

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -14

Diode Equation

i

D

I

S

exp

qv

D

nkT

1

I

S

exp

v

D nV

T

1

where I

S v

D

=

= reverse saturation current (A) voltage applied to diode (V) q = electronic charge (1.60 x 10-19 C) k =

Boltzmann’s constant (1.38 x 10 -23 J/K)

T = absolute temperature n = nonideality factor (dimensionless)

V

T

= kT/q = thermal voltage (V) (25 mV at room temp.)

I

S is typically between 10 -18 and 10 -9 A, and is strongly temperature dependent due to its dependence on n i

2 . The nonideality factor is typically close to 1, but approaches 2 for devices with high current densities. It is assumed to be 1 in this text.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -15

Diode Voltage and Current Calculations

(Example)

Problem: Find diode voltage for diode with given specifications

Given data : I

S

=0.1 fA I

D

= 300

A

Assumptions : Room-temperature dc operation with V

T

=0.025 V

Analysis:

With I

S

=0.1 fA V

D

nV

T ln

1

I

I

D

S

1 ( 0 .

0025 V)ln(1

3

10

4

A

10

16

A

)

0 .

718 V

With I

S

=10 fA

V

D

0 .

603 V

With I

D

= 1 mA, I

S

=0.1 fA V

D

0 .

748 V

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -16

Diode Current for Reverse, Zero, and

Forward Bias

• Reverse bias: i

D

I

S

exp

v

D nV

T

1

I

S

0

1

I

S

• Zero bias:

• Forward bias: i

D

I

S

exp

v

D nV

T

1

I

S

1

1

0

i

D

I

S

exp

v

D nV

T

1

I

S exp

v

D nV

T

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -17

Semi-log Plot of Diode Current and

Current for Three Different Values of I

S

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

I

S

[ A ]

10 I

S

[ B ]

100 I

S

[ C ]

Chap 3 -18

Diode Temperature Coefficient

Diode voltage under forward bias: v

D

V

T ln

i

I

D

S

1

kT q ln

i

I

D

S

1

kT q

Taking the derivative with respect to temperature yields ln

i

I

D

S

dv

D dT

k q ln

Assuming i

D

i

I

D

S

>> I

S

, I kT

S q

1 dI

S v

I

S

n dT i

2 , and V

T

D

GO

V

T

I

1

S dI dT

S v

D

V

GO

T

3 V

T

V/K is the silicon bandgap energy at 0K.

For a typical silicon diode dv

D dT

0.65

1.12

0.075

V

300 K

= -1.82 mV/K

- 1.8 mV/

C

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -19

PTAT Voltage and Electronic Thermometry

• The well-defined temperature dependence of the diode voltage is used as the basis for most digital themometers.

• PTAT Voltage(Voltage proportional to absolute temperature) V

PTAT

= V

D1

-V

D2

= V

T ln(I

D1

/I

S

) -V

T ln(I

D2

/I

S

)

=V

T ln(I

D1

/I

D2

) = KT/qln(I

D1

/I

D2

)

• By using two diode, the temperature dependence of Is has been eliminated from the equation.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

PTAT Thermometer

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Reverse Bias

External reverse bias adds to the built-in potential of the pn junction. The shaded regions below illustrate the increase in the characteristics of the space charge region due to an externally applied reverse bias, v

D

.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -22

Reverse Bias (cont.)

External reverse bias also increases the width of the depletion region since the larger electric field must be supported by additional charge.

w d

( x n

x p

)

2

q s

N

1

A

N

1

D

j

v

R

w d

w d 0

1

v

R j where w

d 0

( x n

x p

)

2

s q

N

1

A

1

N

D

j

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -23

Reverse Bias Saturation Current

We earlier assumed that reverse saturation current was constant.

Since it results from thermal generation of electron-hole pairs in the depletion region, it is dependent on the volume of the space charge region. It can be shown that the reverse saturation gradually increases with increased reverse bias.

I

S

I

S 0

1

v

R j

I

S is approximately constant at I

S0 under forward bias.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -24

Reverse Breakdown

Increased reverse bias eventually results in the diode entering the breakdown region , resulting in a sharp increase in the diode current.

The voltage at which this occurs is the breakdown voltage , V

Z

.

2 V < V

Z

< 2000 V

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -25

Reverse Breakdown Mechanisms

• Avalanche Breakdown

Si diodes with V

Z greater than about 5.6 volts breakdown according to an avalanche mechanism. As the electric field increases, accelerated carriers begin to collide with fixed atoms. As the reverse bias increases, the energy of the accelerated carriers increases, eventually leading to ionization of the impacted ions. The new carriers also accelerate and ionize other atoms. This process feeds on itself and leads to avalanche breakdown.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -26

Reverse Breakdown Mechanisms (cont.)

• Zener Breakdown

Zener breakdown occurs in heavily doped diodes. The heavy doping results in a very narrow depletion region at the diode junction.

Reverse bias leads to carriers with sufficient energy to tunnel directly between conduction and valence bands moving across the junction.

Once the tunneling threshold is reached, additional reverse bias leads to a rapidly increasing reverse current.

• Breakdown Voltage Temperature Coefficient

Temperature coefficient is a quick way to distinguish breakdown mechanisms. Avalanche breakdown voltage increases with temperature, zener breakdown decreases with temperature.

For silicon diodes, zero temperature coefficient is achieved at approximately 5.6 V.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -27

Breakdown Region Diode Model

Jaeger/Blalock

7/1/03

In breakdown, the diode is modeled with a voltage source,

V

Z

R

Z

, and a series resistance, R

Z models the slope of the i-v characteristic.

.

Diodes designed to operate in reverse breakdown are called

Zener diodes and use the indicated symbol.

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -28

PN Junction Capacitance

• The capacitance is important under dynamic signal conditions because it prevents the voltage across the diode from changing instantaneously.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Reverse Bias Capacitance

Changes in voltage lead to changes in depletion width and charge.

This leads to a capacitance that we can calculate from the charge voltage dependence.

Q n

qN

D x n

A

q

N

N

A

A

N

D

N

D

w d

A Coulombs

C j

dQ n dv

R

C j 0

A

1

v

R j

F/cm

2

where C j 0

s w d 0

C j0 is the zero bias junction capacitance per unit area.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -30

Reverse Bias Capacitance (cont.)

Diodes can be designed with hyper-abrupt doping profiles that optimize the reverse-biased diode as a voltage controlled capacitor.

Jaeger/Blalock

7/1/03

Circuit symbol for the variable capacitance diode (varactor)

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -31

Forward Bias Capacitance

In forward bias operation, additional charge is stored in neutral region near edges of space charge region.

Q

D

i

D

T

Coulombs

T is called diode transit time and depends on size and type of diode.

Additional diffusion capacitance, associated with forward region of operation is proportional to current and becomes quite large at high currents.

C j

dQ

D dv

D

i

D

V

T

I

S

T

i

D

T F

V

T

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -32

Schottky Barrier Diode

One semiconductor region of the pn junction diode is replaced by a nonohmic rectifying metal contact.A

Schottky contact is easily added to n -type silicon,metal region becomes anode. n + region is added to ensure that cathode contact is ohmic.

Schottky diode turns on at lower voltage than pn junction diode, has significantly reduced internal charge storage under forward bias.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -33

Schottky Diode

• Key uniqueness: fast switching from ON to OFF and back.

• Widely used:

– in analog circuits: in track and hold circuits in A/D converters,pin drivers of IC test equipment

– in communications and radar applications: as detectors and mixers,also as varactors

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Fermi Level & Fermi Function

• The Fermi function f(E) gives the probability that a given available electron energy state will be occupied at a given temperature.

• Fermi level is the top of the collection of electron energy levels at absolute zero temperature. At higher temperatures, f(E) = 0.5 at Fermi level.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Density of Energy States

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Population of Conduction Band for a

Semiconductor

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Energy Band View of Diode Operation

• For a p-n junction at equilibrium, the fermi levels match on the two sides of the junctions . Electrons and holes reach an equilibrium at the junction and form a depletion region.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Reverse Bias

• To reverse-bias the p-n junction, the p side is made more negative, making it "uphill" for electrons moving across the junction. The conduction direction for electrons in the diagram is right to left, and the upward direction represents increasing electron energy.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Forward Bias

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Schottky Diode Energy Band Diagram

• Electrons flow into the metal until equilibrium is reached between the diffusion of electrons from the semiconductor into the metal and the drift of electrons caused by the field created by the ionized impurity atoms. This equilibrium is characterized by a constant Fermi energy throughout the structure.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Ohmic Contact

• a contact between a metal and a semiconductor is typically a Schottky barrier contact.

• However, if the semiconductor is very highly doped, the

Schottky barrier depletion region becomes very thin. At very high doping levels, a thin depletion layer becomes quite transparent for electron tunneling.

• a practical way to make a good ohmic contact is to make a very highly doped semiconductor region between the contact metal and the semiconductor.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Jaeger/Blalock

7/1/03

Diode Spice Model

R s is inevitable series resistance of a real device structure. Current controlled current source represents ideal exponential behavior of diode.

Capacitor specification includes depletion-layer capacitance for reverse-bias region as well as diffusion capacitance associated with junction under forward bias.

Typical default values: Saturation current= 10 fA, R s

= 0

W

, Transit time= 0 second

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -43

Diode Layout

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -44

Diode Circuit Analysis: Basics

V and R may represent Thevenin equivalent of a more complex 2terminal network.Objective of diode circuit analysis is to find quiescent operating point for diode, consisting of dc current and voltage that define diode’s i-v characteristic.

Jaeger/Blalock

7/1/03

Loop equation for given circuit is:

V

I

D

R

V

D

This is also called the load line for the diode. Solution to this equation can be found by:

• Graphical analysis using load-line method.

• Analysis with diode’s mathematical model.

• Simplified analysis with ideal diode model.

• Simplified analysis using constant voltage drop model.

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -45

Load-Line Analysis (Example)

Jaeger/Blalock

7/1/03

Problem: Find Q-point

Given data: V =10 V, R =10k

W

.

Analysis:

10

I

D

10

4

V

D

To define the load line we use,

V

D

= 0 I

D

( 10 V / 10 k

W

)

1 mA

V

D

= 5 V, I

D

=0.5 mA

These points and the resulting load line are plotted.Q-point is given by intersection of load line and diode characteristic:

Q-point = (0.95 mA, 0.6 V)

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -46

Analysis using Mathematical Model for

Problem: Find Q-point for given diode characteristic.

Given data: I

S

=10 -13 A, n=1, V

T

=0.0025 V

Analysis:

I

D

10

I

S

exp

V

D nV

T

10

4

10

13

exp

1

40 V

D

10

1

13

exp

V

D

40 V

D

1

Diode

•Make initial guess V

D

0 .

•Evaluate f and its derivative f’ for this value of V

•Calculate new guess for V

D

0

D

.

f

D using

V

D

1

V

D

f

0

' ( V

D

)

•Repeat steps 2 and 3 till convergence.

Using a spreadsheet we get :

Q-point = ( 0.9426 mA, 0.5742 V) is load line, given by a transcendental equation. A numerical answer can be found by using Newton’s iterative method.

f

10

10

4

10

13

exp

40 V

D

1

V

D

Since, usually we don’t have accurate saturation current and significant tolerances for sources and passive components, we need answers precise up to only 2or 3 significant digits.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -47

Analysis using Ideal Model for Diode

Jaeger/Blalock

7/1/03

If diode is forward-biased, voltage across diode is zero. If diode is reverse-biased, current through diode is zero.

v

D

=0 for i

D

>0 and i

D

=0 for v

D

< 0

Thus diode is assumed to be either on or off.

Analysis is conducted in following steps:

• Select diode model.

• Identify anode and cathode of diode and label v

D and i

D

.

• Guess diode’s region of operation from circuit.

• Analyze circuit using diode model appropriate for assumed operation region.

• Check results to check consistency with assumptions.

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -48

Analysis using Ideal Model for Diode:

Example

Since source is forcing positive current through diode assume diode is on.

I

D

( 10

10 k

0

W

) V

1 m A

I

D

0 our assumption is right.

Q-point is(1 mA, 0V)

Since source is forcing current backward through diode assume diode is off. Hence I

D

10

V

D

10 4 I

D

V

D

10 V

=0 . Loop equation is:

0 our assumption is right.

Q-point is (0, -10 V)

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -49

Analysis using Constant Voltage Drop

Model for Diode

Analysis:

Since 10V source is forcing positive current through diode assume diode is on.

I

D

( 10

10

V on k

W

) V

( 10

0 .

6 ) V

10 k

W

0 .

94 mA v

D

= V on for i

D

>0 and i

D

= 0 for v

D

< V on

.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -50

Jaeger/Blalock

7/1/03

Two-Diode Circuit Analysis

Analysis: Ideal diode model is chosen. Since

15V source is forcing positive current through

D

1 and D

2 and -10V source is forcing positive current through D

2

, assume both diodes are on.

Since voltage at node D is zero due to short circuit of ideal diode D

1

,

I

1

( 15

0 ) V

10 k

W

I

1

I

D 1

I

D 2

1 .

50 mA

I

D 1

I

D 2

0

(

10

5 k

W

) V

2 .

00 mA

1 .

5

2

0 .

50 mA

Q-points are (-0.5 mA, 0 V) and (2.0 mA, 0 V)

But, I

D1

<0 is not allowed by diode, so try again.

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -51

Two-Diode Circuit Analysis (contd.)

Analysis: Since current in

D

2 but that in D

1 is invalid, the second guess is D

1 and D

2 on.

off

Since current in

15

10 , 000 I

1

5

D

1

, 000 is zero, I

D2

I

D 2

(

10 )

= I

1

,

0

V

I

1

D 1

25 V

1 .

67 mA

15,000

15

10

W

, 000 I

1

15

16 .

7

1 .

67 V

Q-points are D

1

: (0 mA, -1.67 V):off

D

2

: (1.67 mA, 0 V) :on

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -52

Three Diode Circuit

• A more complicated circuit.

CVD model will be used in the analysis to improve accuracy.

• First make an initial guess on the state of the diodes then verify with KCL

• Repeat until correct diode states are found

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Three diode Circuit, all diodes on

-0.6V

-0.6V

0V

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Iteration 1 Analysis

V

C

= - 0.6 V, V

B

= - 0.6 + 0.6 = 0 V,

I

V

A

1

= 0 – 0.6 = - 0.6 V

= (10 – 0) V/10 k

W

= 1 mA

I

2

= [-0.6 – (-20)]/10K = 1.94 mA

I

3

= [-0.6 – (-10)]/10K = 0.94 mA (3.36)

Using Kirchhoff’s current law

I

2

= I

D1

, I

1

= I

D1

+ I

D2

, I

3

= I

D2

+ I

D3

(3.37)

Combining Eqs. (3.39) and (3.40) yields the three diode currents:

I

D1

=1.94 mA > 0, I

D2

= -0.94 mA < 0, I

D3

= 1.86 mA > 0 (3.38)

Check : I

D2

< 0 contradicted with our initial assumption.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Three diode circuits, D1 and D3 on only

10-R

1

*I

1

-0.6V

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Iteration 2 Analysis

I

D1

= 29.4 / 20K = 1.47 mA > 0,

I

D3

= I

3

= -0.6 – (-10) /10K = 0.94 mA > 0

The voltage across diode D

2 is given by

V

D2

= 10 – 10K * I1 – (-0.6) = 10 – 14.7 + 0.6 = -4.10 V < 0

Check : I

D1

>0, I

D3

>0, and V

D2

<0 are consistent with our assumptions.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Analysis of Diodes in Reverse

Breakdown Operation

Choose 2 points (0V, -4 mA) and (-5 V, -3 mA) to draw the load line.It intersects with i-v characteristic at Q-point (-2.9 mA, -5.2 V).

Using piecewise linear model :

I

Z

I

D

0

Using load-line analysis:

20

V

D

5000 I

D

Jaeger/Blalock

7/1/03

20

I

Z

5100 I

Z

( 20

5

5100

W

) V

5

0

2 .

94 mA

Since I

Z

>0 ( I

D

<0), solution is consistent with Zener breakdown assumption.

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -58

Voltage Regulator using Zener Diode

Zener diode keeps voltage across load resistor constant.

For Zener breakdown operation, I

Z

>0.

I

S

I

L

V

S

V

Z

R

V

Z

R

L

I

S

I

5 V

5 k

W

L

( 20

5 k

W

1 mA

2 mA

5 ) V

3 mA

I

Z

For proper regulation, Zener current must be positive. If Zener current <0, Zener diode no longer controls voltage across load resistor and voltage regulator is said to have

“dropped out of regulation”.

I

Z

V

S

R

V

Z

1

R

1

R

L

0

R

L

V

V

S

Z

R

1

R min

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -59

Voltage Regulator using Zener Diode:

Example (Including Zener Resistance)

V

20 V

L

5000

W

V

5 V

L

100

W

V

L

5000

W

0

V

L

5 .

19 V

I

Z

V

L

100

5

W

V

5 .

19 V

100

W

5 V

1 .

9 mA

0

Problem: Find output voltage and

Zener diode current for Zener diode regulator.

Given data: V

S

=20 V, R =5 k

W

, R

Z

=

0.1 k

W,

V

Z

=5 V

Analysis: Output voltage is a function of current through Zener diode.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -60

Photo Diodes and Photodetectors

Jaeger/Blalock

7/1/03

If depletion region of pn junction diode is illuminated with light with sufficiently high frequency, photons can provide enough energy to cause electrons to jump the semiconductor bandgap to generate electron-hole pairs:

E

P

h

hc

E

G h =Planck’s constant= 6.626e-34 J.s

υ = frequency of optical illumination

= wavelength of optical illumination c =velocity of light=3e+8m/s

Photon-generated current can be used in photo detector circuits to generate output voltage v o

i

PH

R

Diode is reverse-biased to enhance depletion-region width and electric field.

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -61

CMOS Image Sensor

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Diode i-v curve with illumination

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Optical Fiber Application

• In optical fiber communication systems, the amplitude of the incident light is modulated by rapidly changing digital data, and i

PH is a time-varying signal. The time-varying signal voltage at v o is fed to additional electronic circuits to demodulate the signal and recover the original data that were transmitted down the optical fiber.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Solar Cells and

Light-Emitting Diodes

In solar cell applications, optical illumination is constant, dc current I

PH is generated. Aim is to extract power from cell, i-v characteristics are plotted in terms of cell current and cell voltage. For solar cell to supply power to external circuit,

I

C

V

C product must be positive and cell should be operated near point of maximum output power P max

.

Light-Emitting Diodes use recombination process in forward-biased pn junction diode. When a hole and electron recombine, energy equal to bandgap of semiconductor is released as a photon.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -65

Solar Cell Videos

• Next generation cheap solar cell – link

• NASA Helios – link

• 2008 Solar Challenge link

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Solar Power for the Home

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

LED

• Organic LED introduction – link

• Sony OLED TV XEL1 – link

• Cool LED light ad link

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

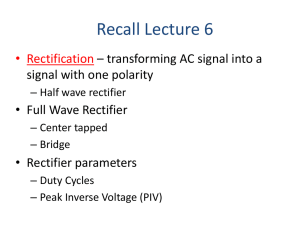

Rectifier Circuits

•

Basic rectifier converts an ac voltage to a pulsating dc voltage.

• A filter then eliminates ac components of the waveform to produce a nearly constant dc voltage output.

• Rectifier circuits are used in virtually all electronic devices to convert the 120 V-60 Hz ac power line source to the dc voltages required for operation of the electronic device.

• In rectifier circuits, the diode state changes with time and a given piecewise linear model is valid only for a certain time interval.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -69

Delta Electronics

• 台達電子集團 (The Delta Group) holds the world's number one position in switching power supplies.

• Power Product:

– Switching Power Supply

– DC / DC converter

– Uninterrupted Power Supply (UPS)

– AC / DC adapter

– Telecom Power

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Delta Electronics

Half-Wave Rectifier Circuit with

Resistive Load

For positive half-cycle of input, source forces positive current through diode, diode is on, v o

= v s

.

During negative half cycle, negative current can’t exist in diode, diode is off, current in resistor is zero and v o

=0 .

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -72

Half-Wave Rectifier Circuit with

Resistive Load (contd.)

Using CVD model, during on state of diode v o

=( V

P sin w t)- V on

. Output voltage is zero when diode is off.

Often a step-up or step-down transformer is used to convert 120 V-60 Hz voltage available from power line to desired ac voltage level as shown.

Jaeger/Blalock

7/1/03

Time-varying components in circuit output are removed using filter capacitor.

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -73

Jaeger/Blalock

7/1/03

Peak Detector Circuit

As input voltage rises, diode is on and capacitor (initially discharged) charges up to input voltage minus the diode voltage drop.

At peak of input, diode current tries to reverse, diode cuts off, capacitor has no discharge path and retains constant voltage providing constant output voltage

V dc

= V

P

V on

.

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -74

A 175,000 uF, 15-V filter Capacitor

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Half-Wave Rectifier Circuit with

RC

Load

As input voltage rises during first quarter cycle, diode is on and capacitor (initially discharged) charges up to peak value of input voltage.

At peak of input, diode current tries to reverse, diode cuts off, capacitor discharges exponentially through R . Discharge continues till input voltage exceeds output voltage which occurs near peak of next cycle. Process then repeats once every cycle.

This circuit can be used to generate negative output voltage if the top plate of capacitor is grounded instead of bottom plate. In this case,

V dc

= -( V

P

V on

)

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -76

Ripple Voltage and Conduction Interval

During the discharge period, the voltage across the capacitor is described by v o

(t’) = (V p

- V on

) exp(-t’/RC) for t’ = (t – T/4)

0 (3.53)

The ripple voltage V r

V r

= (V p

– V on

) – (V p is given by

– V on

) exp(-(T -

T)/RC) (3.54)

Using exp(-x) ~= (1-x) for small x to simplify.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Half-Wave Rectifier Circuit with

RC

Load (contd.)

Output voltage is not constant as in ideal peak detector, but has ripple

voltage V r

.

Diode conducts for a short time

T called conduction interval during each cycle and its angular equivalent is called conduction angle θ c

V r

( V

P

V on

)

T

RC

1

T

T

( V

P

R

V on

)

T

C

.

T

2 T

RC

( V

P

V on

)

V

P

2 V

V

P r

c

w

T

2

V

V r

P

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -78

Half-Wave Rectifier Analysis: Example

Problem: Find dc output voltage, output current, ripple voltage, conduction interval, conduction angle.

Given data: secondary voltage V r ms

V on

= 1 V

Analysis:

V dc

I dc

V

P

V

P

V on

V on

R

Using discharge interval T

( 12 .

6 2

12.6 (60 Hz),

1 ) V

16.8V

16.8V

15

W

1 .

12 A

=1/60 s ,

V r

( V

P

V on

)

T

R

R = 15

C

W

, C

0 .

747 V

= 25,000

F,

c

T

w

w c

T

2

c f

2 V r

V

P

0 .

290 rad

0 .

29

120

16 .

6

0

0 .

769 ms

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -79

Jaeger/Blalock

7/1/03

T*I dc

Peak Diode Current

I p

*

T/2

In rectifiers, nonzero current exists in diode for only a very small fraction of period T , yet an almost constant dc current flows out of filter capacitor to load.

Total charge lost from capacitor in each cycle is replenished by diode during short conduction interval causing high peak diode currents. If repetitive current pulse is modeled as triangle of height I

P and width

T ,

I

P

I dc

2

T

T

48 .

6 A using values from previous example.

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -80

Surge Current

Besides peak diode currents, when power supply is turned on, there is an even larger current through diode called surge current.

During first quarter cycle, current through diode is approximately i d

( t )

i c

( t )

C d dt

V

P sin w t

w

CV

P cos w

Peak values of this initial surge current occurs at t = 0 + : t

I

SC

w

CV

P

168 A using values from previous example.

Actual values of surge current won’t be as large as predicted because of neglected series resistance associated with rectifier diode as well as transformer.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -81

Jaeger/Blalock

7/1/03

Peak Inverse Voltage Rating

Peak inverse voltage (PIV) rating of the rectifier diode gives the breakdown voltage.

When diode is off, reverse-bias across diode is V dc

negative peak, v s

. When v s reaches

PIV

V dc

v s min

V

P

V on

(

V

P

)

2 V

P

PIV value corresponds to minimum value of Zener breakdown voltage for rectifier diode.

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -82

Diode Power Dissipation

Average power dissipation in diode is given by

P

D

1

T

T

v

0

D

( t ) i

D

( t ) dt

1

T

T

0

V on i

D

( t ) dt

V on

I

P

2

T

T

V on

I dc

The simplification is done by assuming the triangular approximation of diode current and that voltage across diode is constant at V dc

.

P

D

=1*1.1=1.1W

Average power dissipation in the diode series resistance is given by

P

D

1

T

T

i

0

D

2

( t ) R

S dt

1

3

I

P

2

R

S

T

T 4

3

T

T

I dc

2

R

S

This power dissipation can be reduced by minimizing peak current through use of minimum required size of filter capacitor or using fullwave rectifiers. Rs=0.2ohm yields P

D

=7.3W

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -83

Full-Wave Rectifiers

Jaeger/Blalock

7/1/03

Full-wave rectifiers cut capacitor discharge time in half and require half the filter capacitance to achieve given ripple voltage.

All specifications are same as for half-wave rectifiers.

Reversing polarity of diodes gives a fullwave rectifier with negative output voltage.

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -84

Full Wave vs. Half Wave Rectifier

• Same formulas for dc output voltage, ripple voltage, and

ΔT, except the discharge interval is T/2 rather than T.

• The ripple voltage V r is halved, the conduction interval ΔT and peak current are reduced. The PIV rating are the same.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Full Wave Rectifier with Negative Output

Voltage

• By reversing the polarity of the diodes, a full-wave rectifier circuit with a negative output voltage is realized

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Full-Wave Bridge Rectification

Requirement for a center-tapped transformer in the full-wave rectifier is eliminated through use of 2 extra diodes.All other specifications are same as for a half-wave rectifier except

PIV= V

P

.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -87

Rectifier Topology Comparison

•

Filter capacitor is a major factor in determining cost, size and weight in design of rectifiers.

• For given ripple voltage, full-wave rectifier requires half the filter capacitance as that in half-wave rectifier. Reduced peak current can reduce heat dissipation in diodes. Benefits of full-wave rectification outweigh increased expenses and circuit complexity (a extra diode and center-tapped transformer).

• Bridge rectifier eliminates center-tapped transformer, PIV rating of diodes is reduced. Cost of extra diodes is negligible.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -88

Rectifier Comparison Table

Table 3. 4 - Comparison of Rectifiers with Capacitive Filters

Rectifier

Parameter

Filter Capacitor

PIV Rating

Peak Diode

Current

(Constant V

R

)

Comments

Half-Wave

Rectifier

C

V

P

V o n

V r

T

R

2V

P

Highest

I

P

Least Complexity

Full-Wave

Rectifier

C

V

P

V o n

V r

T

2 R

2V

P

Reduced

I

P

2

Smaller Capacitor

Requires

Center-Tapped

Transformer

Two Diodes

Full-Wave Bridge

Rectifier

C

V

P

2 V o n

V r

T

2 R

V

P

Reduced

I

P

2

Smaller Capacitor

Four Diodes

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Rectifier Design Analysis

Problem: Design rectifier with given specifications.

Given data: V dc

=15 V, V r

< 0.15 V, I dc

= 2 A

Analysis: Use full-wave bridge rectifier that needs smaller value of filter capacitance, smaller diode PIV rating and no center-tapped transformer.

V

V

P

2

V dc

2 V on

2

15

2

2

V

12V rms

C

I dc

T /

V r

2

2 A

1

120 s

1

0 .

15 V

0 .

111 F

T

1 w

2 V r

V

P

1

120

2 ( 0 .

15

17V

V)

0 .

352 ms

I

P

I dc

2

T

T

2

2 A

1/60 s

0.352ms

94 .

7 A I surge

PIV

V

P w

CV

P

17 V

120

( 0 .

111 )( 17 )

711 A

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -90

Three-terminal IC Voltage Regulators

• Uses feedback with high-gain amplifier to reduce ripple voltage at output.Bypass capacitors provide low-impedance path for high-frequency signals to ensure proper operation of regulator.

• Provides excellent line and load regulation, maintaining constant voltage even if output current changes by many orders of magnitude.

• Main design constraint is V

REG which must not fall below a minimum specified “dropout” voltage (a few volts).

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -91

Clamping or DC-Restoring Circuit

Jaeger/Blalock

7/1/03

After the initial transient lasting less than one cycle in both circuits, output waveform is an undistorted replica of input.

Both waveforms are clamped to zero. Their dc levels are said to be restored by the clamping circuit.

Clamping level can also be shifted away from zero by adding a voltage source in series with diode.

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -97

Clipping or Limiting Circuits

Clipping circuits have dc path between input and output, whereas clamping circuits use capacitive coupling between input and output.

The voltage transfer characteristic shows that gain is unity for v

I

V

C

.

< V

C

, and gain is zero for v

I

>

A second clipping level can also be set as shown or diodes can be used to control circuit gain by switching resistors in and out of circuits.

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -98

Dynamic Switching Behavior of Diode

Non-linear depletion-layer capacitance of diode prevents voltage from changing instantaneously and determines turn-on and recovery times. Both forward and reverse current overshoot final value when diode switches on and off as shown. Storage time is given by:

S

T ln

1

I

F

I

R

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill

Chap 3 -99

Homework 3

• Written Homework

– 3.2

– 3.24

– 3.56

– 3.69 for figure (b)

– 3.72 for figure (a)

– 3.91

• SPICE Homework for rectifier

Jaeger/Blalock

7/1/03

Microelectronic Circuit Design

McGraw-Hill