V DS - Weber State University

advertisement

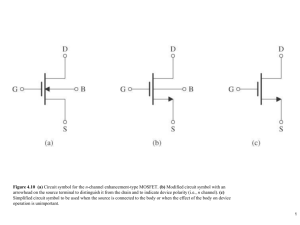

1 Course Outline 1. Chapter 1: Signals and Amplifiers 2. Chapter 3: Semiconductors 3. Chapter 4: Diodes 4. Chapter 5: MOS Field Effect Transistors (MOSFET) 5. Chapter 6: Bipolar Junction Transistors (BJT) 6. Chapter 2 (optional): Operational Amplifiers EE 3110 Microelectronics I Suketu Naik 2 Chapter 5: MOSFETs Part I EE 3110 Microelectronics I Suketu Naik 3 Introduction IN THIS CHAPTER WE WILL LEARN The physical structure of the MOS transistor and how it works. How the voltage between two terminals of the transistor control the current that flows through the third terminal, and the equations that describe these current-voltage characteristics. How the transistor can be used to make an amplifier, and how it can be used as a switch in digital circuits. EE 3110 Microelectronics I Suketu Naik Introduction 4 IN THIS CHAPTER WE WILL LEARN How to obtain linear amplification from the fundamentally nonlinear MOS transistor. The three basic ways for connecting a MOSFET to construct amplifiers with different properties. Practical circuits for MOS-transistor amplifiers that can be constructed using discrete components. EE 3110 Microelectronics I Suketu Naik 5 Introduction We studied two-terminal semi-conductor devices (e.g. diode) Now we turn our attention to three-terminal devices They are more useful because they present multitude of applications: signal amplification, digital logic, memory, etc… Buck Converter (DC-DC) Power Amplifier EE 3110 Microelectronics I Op Amp Suketu Naik Introduction 6 Q: What, in simplest terms, is the desired operation of a three-terminal device? A: Employ voltage between two terminals to control current flowing in to the third. EE 3110 Microelectronics I Suketu Naik Introduction Q: What are two major types of three-terminal semiconductor devices? metal-oxide-semiconductor field-effect transistor (MOSFET) bipolar junction transistor (BJT) Q: Why are MOSFET’s more widely used? size (smaller) ease of manufacture consume less power 7 MOSFET technology It allows placement of approximately 2 billion transistors on a single IC backbone of very large scale integration (VLSI) It is considered preferable to BJT technology for many applications. EE 3110 Microelectronics I Suketu Naik 8 5.1. Device Structure and Operation Figure 5.1. shows general structure of the n-channel enhancementtype MOSFET Figure 5.1: Physical structure of the enhancement-type NMOS transistor: (a) perspective view, (b) cross- section. Note that typically L = 0.03um to 1um, W = 0.1um to 100um, and the thickness of the oxide Oxford University Publishing layer (tox(0195323033) ) is in the range of 1 to 10nm. Microelectronic Circuits by Adel S. Sedra and Kenneth C. Smith EE 3110 Microelectronics I Suketu Naik 9 twoOperation n-type doped 5.1. Device Structure and regions (drain, source) layer of SiO2 separates source and drain metal, placed on top of SiO2, forms gate electrode one p-type doped region Figure 5.1: Physical structure of the enhancement-type NMOS transistor: (a) perspective view, (b) cross- section. Note that typically L = 0.03um to 1um, W = 0.1um to 100um, and the thickness of the oxide Oxford University Publishing layer (tox(0195323033) ) is in the range of 1 to 10nm. Microelectronic Circuits by Adel S. Sedra and Kenneth C. Smith EE 3110 Microelectronics I Suketu Naik Layout of NMOS Transistor 10 Side View (Fabricated Device) Top View (Masks) Ref: Lecture 9 – MOSFET, Microelectronic Devices and Circuits, Fall 2005, MIT OpenCourseWare EE 3110 Microelectronics I Suketu Naik 5.1. Device Structure and Operation 11 The name MOSFET is derived from its physical structure However, many MOSFET’s do not actually use any “metal”, polysilicon is used instead Another name for MOSFET is insulated gate FET, or IGFET The device is composed of two pn-junctions, however they maintain reverse biasing at all times. Drain will always be at positive voltage with respect to source. EE 3110 Microelectronics I Suketu Naik 5.1.2. Operation with Zero Gate Voltage 12 With zero voltage applied to gate, two back-to-back diodes exist in series between drain and source. “They” prevent current conduction from drain to source when a voltage vDS is applied. yielding very high resistance (1012ohms) Figure 5.1: Physical structure EE 3110 Microelectronics I Suketu Naik 5.1.3. Creating a Channel for Current Flow 13 Q: What happens if (1) source and drain are grounded and (2) positive voltage is applied to gate? step #1: vGS is applied to the gate terminal, causing a positive build-up of positive charge along metal electrode. step #2: This build-up causes free holes to be repelled from region of p-type substrate under gate. Figure 5.2: The enhancement-type NMOS transistor with a positive voltage applied to the gate. An n channel is induced at the top of the substrate beneath the gate EE 3110 Microelectronics I Suketu Naik 5.1.3. Creating a Channel for Current Flow 14 step #3: This migration results in the uncovering of negative bound charges, originally neutralized by the free holes step #4: The positive gate voltage also attracts electrons from the n+ source and drain regions into the channel. Figure 5.2: The enhancement-type NMOS transistor with a positive voltage applied to the gate. An n channel is induced at the top of the substrate beneath the gate EE 3110 Microelectronics I Suketu Naik 15 this induced channel is 5.1.3. Creating a Channel for Current Flow also known as an inversion layer step #5: Once a sufficient number of “these” electrons accumulate, an n-region is created… connecting the source and drain regions step #6: This provides path for current flow between D and S. Figure 5.2: The enhancement-type NMOS transistor with a positive voltage applied to the gate. An n channel is induced at the top of the substrate beneath the gate EE 3110 Microelectronics I Suketu Naik 5.1.3. Creating a Channel for Current Flow 16 threshold voltage (Vt) – is the Vtn is used for n-type minimum value of vGS required to MOSFET, Vtp is used for p-channel form a conducting channel between drain and source effective / overdrive voltage – is typically between 0.3 and the difference between vGS applied 0.6Vdc and Vt. field-effect – when positive vGS is oxide capacitance (Cox) – is the capacitance of the parallel plate applied, an electric field develops capacitor per unit gate area (F/m2) between the gate electrode and induced n-channel – the (eq5.1) vOV vGS Vt conductivity of this channel is affected by the strength of field ox is permittivity of SiO2 3.45E11 F / m tox is thickness of SiO2 layer SiO2 layer acts as dielectric (eq5.3) C ox EE 3110 Microelectronics I ox tox in F / m2 Suketu Naik 5.1.3. Creating a Channel for Current Flow Q: What is main requirement for n-channel to form? A: The voltage across the oxide layer must exceed Vt. For example, when vDS = 0… the voltage at every point along channel is zero the voltage across the oxide layer is uniform and equal to vGS 17 Q: How can one express the magnitude of electron charge contained in the channel? W and L represent width and length of channel respectively (eq5.2) Q C ox WL vOV in C Q: What is effect of vOV on nchannel? A: As vOV increases, so does the depth of the nchannel as well as its conductivity. EE 3110 Microelectronics I Suketu Naik 18 5.1.4. Applying a small vDS Q: For small values of vDS, how does one calculate iDS ( iD)? n represents mobility of electrons at surface of the n-channel in m2 / Vs nvDS (eq5.7) iD C oxWvOV in A L charge per unit length of n -channel in C / m electron drift velocity in m2 / Vs EE 3110 Microelectronics I Suketu Naik 19 5.1.4. Applying a small vDS Q: What can be observed from equation (5.7)? A: For small values of vDS, the n-channel acts like a variable resistance whose value is controlled by vOV (vOV =vGS -vt) W (eq5.7) iD nC ox vOV vDS in A L vDS 1 (eq5.8a) rDS in iD W nC ox vOV L process transconductance aspect ratio parameter EE 3110 Microelectronics I Suketu Naik 20 5.1.4. Applying a Note small v DS vOV represents that this the depth of the n-channel what if it is not assumed to be constant? How does this equation change? VERY Q: IMPORTANT What do weequation note from equation (5.7)? A: For small values of vDS, the n-channel acts like a variable resistance whose value is controlled by vOV. W (eq5.7) iD nC ox vOV vDS in A L vDS 1 (eq5.8a) rDS in iD W nC ox vOV L process transconductance aspect ratio parameter EE 3110 Microelectronics I Suketu Naik 5.1.4. Applying a Small vDS 21 Q: What is rDS? A: rDS is the channel resistance Q: What three factors is rDS dependent on? A: process transconductance parameter for NMOS (nCox) – which is determined by the manufacturing process A: aspect ratio (W/L) – which is dependent on size requirements / allocations A: overdrive voltage (vOV) – which is applied by the user EE 3110 Microelectronics I Suketu Naik 22 kn is known as NMOS-FET transconductance parameter and is defined as nCoxW/L 1/rDS low resistance, high vOV high resistance, low vOV Figure 5.4: The iD-vDS characteristics of the MOSFET in Figure 5.3. Oxford University Publishing Microelectronic Circuits by Adel S. Sedra applied and Kenneth C. Smith (0195323033) when the voltage between and source VDS is kept Suketu small. EE 3110drain Microelectronics I Naik 5.1.5. Operation as vDS is Increased 23 Q: What happens to iD when vDS increases beyond small values? A: The relationship between them ceases to be linear. Q: How can this non-linearity be explained? step #1: Assume that vGS is held constant at value greater than Vt. step #2: Also assume that vDS is applied and appears as voltage drop across n-channel. step #3: Note that voltage decreases from vGS at the source end of channel to vGD at drain end, where… vGD = vGS – vDS vGD = Vt + vOV – vDS EE 3110 Microelectronics I Suketu Naik 24 avOV avDS The voltage differential between both sides of nchannel increases with vDS. Figure 5.5:Oxford Operation University Publishingof the enhancement NMOS transistor as vDS is Microelectronic Circuits by Adel S. Sedra and Kenneth C. Smith (0195323033) EE 3110 Microelectronics I Suketu Naik increased note the average value 25 As vDS is increased, the channel becomes more tapered and channel resistance increases Figure 5.6(a): For a MOSFET with vGS = Vt + vOV , application of vDS causes the voltage drop along the channel to vary linearly, with an average value of 0.5vDS at the midpoint. Since vGD > Vt, the channel still exists at the drain end. (b) The channel shape corresponding to the situation in (a). While the depth of the channel at the source is still proportional to vOV,I the drain end is not. EE 3110 Microelectronics Suketu Naik Q: How can this non-linearity be explained? 26 action: replace vOV with vOV 12 vDS W 1 (eq5.7) iD nC ox vOV 2 vDS vDS step #4: Define L iDS in terms of vDS and vOV. W 1 C v if vDS vOV n ox OV 2 vDS vDS L iD is dependent on the (eq5.7) iD W 1 apparent vOV (not vDS C v otherwise n ox OV 2 vDS vDS L inherently) which does not if vDS vOV then vDS vOV change after vDS > vOV W 1 C v if vDS vOV n ox OV 2 vDS vDS L (eq5.14) iD in A 1 W nC ox vO2 V otherwise 2 L Oxford University Publishing Microelectronic Circuits by Adel S. Sedra and Kenneth C. Smith (0195323033) triode vs. saturation region EE 3110 Microelectronics I Suketu Naik 27 saturation occurs once vDS > vOV W 1 triode: C v n ox OV 2 vDS vDS L (eq5.14) iD saturation: 1 nC ox W vO2 V Oxford University Publishing 2 L Microelectronic Circuits by Adel S.Sedra and Kenneth C. Smith (0195323033) EE 3110 Microelectronics I if vDS vOV in A otherwise Suketu Naik 28 5.1.6. Operation for vpinch-off >> v does DS OV not mean blockage of current In section 5.1.5, we assume that n-channel is tapered but channel pinch-off does not occur. Trapezoid doesn’t become triangle for vGD > Vt Q: What happens if vDS > vOV? A: MOSFET enters saturation region. Any further increase in vDS has no effect on iD. Figure 5.8: Operation of MOSFET with vGS = Vt + vOV as vDS is increased to vOV. At the drain end, vGD decreases to Vt and the channel depth at the drainend reduces to zero (pinch-off). At this point, the MOSFET enters saturation more of operation. Further increasing vDS (beyond vOV) has no effect on the channel shape and iD remains constant. EE 3110 Microelectronics I Suketu Naik Summary The equation used to define iD depends on relationship btw vDS and vOV. vDS << vOV vDS < vOV vDS => vOV vDS >> vOV 29 n represents mobility of electrons at surface of the n-channel in m2 / Vs v (eq5.7) iD C oxWvOV n DS in A L charge per unit length of n -channel in C / m electron drift velocity in m2 / Vs W (eq5.14) iD nC ox vOV 12 vDS vDS in A L W 2 1 in A (eq5.17) iD nC ox vOV L 2 W 2 1 (eq5.23) iD nC ox vOV 1 vDS in A L 2 EE 3110 Microelectronics I Suketu Naik n-channel MOSFET (NMOS) 30 Figure 5.11 shows an nchannel enhancement MOSFET. There are four terminals: drain (D), gate (G), body (B), and source (S). Usually it is assumed that body and source are connected. EE 3110 Microelectronics I Suketu Naik 31 n-channel MOSFET (NMOS) Gap indicates insulation (oxide) between the gate electrode (G) and the Body (B) This arrow from Body (p-type) to the nchannel (n-type) indicates pn junction and hence the type of device (n channel mosfet) This arrow indicates the current going into the source and thus indicates the type of device (n channel mosfet) EE 3110 Microelectronics I Suketu Naik 32 NMOS Symbol Although MOSFET is symmetrical device, one often designates terminals as source and drain. Q: How does one make this designation? A: By polarity of voltage applied. Arrowheads designate “normal” direction of current flow Note that, in part (b), we designate current as DS. No need to place arrow with B. the potential at drain (vD) is always positive with respect to source (vS) EE 3110 Microelectronics I Suketu Naik 33 NMOS Symbol Although MOSFET is symmetrical device, one often designates terminals as source and drain. Q: How does one make this designation? A: By polarity of voltage applied. Arrowheads designate “normal” direction of current flow Note that, in part (b), we designate current as DS. No need to place arrow with B. the potential at drain (vD) is always positive with respect to source (vS) EE 3110 Microelectronics I Suketu Naik Representations of NMOS Transistor EE 3110 Microelectronics I 34 Suketu Naik Regions of Operation of Enhancement NMOS 35 Tabe 5.1 EE 3110 Microelectronics I Suketu Naik iD -vDS characterstics of Enhancement NMOS 36 Keep vGS constant and vary vDS EE 3110 Microelectronics I Suketu Naik 37 iD -vGS characterstics of Enhancement NMOS Keep vDS constant (vDS > vOV; saturation) and vary vGS These charactertics are useful for amplification 2 vOV 1 W 2 (eq5.21) iD kn vGS Vtn 2 L this relationship provides basis for application of MOSFET as amplifier EE 3110 Microelectronics I Suketu Naik 38 iD -vGS characterstics of Enhancement NMOS Vary vGS Voltage controlled current Source Useful for amplification 2 vOV 1 W 2 (eq5.21) iD kn vGS Vtn 2 L this relationship provides basis for application of MOSFET as amplifier EE 3110 Microelectronics I Suketu Naik 39 Large signal model of NMOS in saturation MOSFET in saturation behaves as a voltage controlled current source EE 3110 Microelectronics I Suketu Naik 40 Example 5.2: NMOS Transistor Consider an NMOS transistor fabricated in an 0.18-m process with L = 0.18m and W = 2m. The process technology is specified to have Cox = 8.6fF/m2, n = 450cm2/Vs, and Vtn = 0.5V. Q(a): Find VGS and VDS that result in the MOSFET operating at the edge of saturation with ID = 100A Q(b): If VGS is kept constant, find VDS that results in ID = 50A Q(c): To investigate the use of the MOSFET as a linear amplifier, let it be operating in saturation with VDS = 0.3V. Find the change in iD resulting from vGS changing from 0.7V by +0.01V and -0.01V EE 3110 Microelectronics I Suketu Naik 5.2.4. Finite Output Resistance in Saturation 41 Q: What effect will increased vDS have on n-channel once pinch-off has occurred? A: Addition of finite output resistance (ro). Figure 5.16: Increasing vDS beyond vDSsat causes the channel pinch-off point to move slightly away from the drain, thus reducing the effective channel length by DL Q: What is the effect on iD? valid when vDS vOV 1 W 2 (eq5.17) iD nC ox vOV in A 2 L 1 W 2 (eq5.23) iD nC ox vOV 1 vDS in A 2 L valid when vDS vOV EE 3110 Microelectronics I Suketu Naik 5.2.4. Output Resistance in Saturation 42 Q: How is ro defined? step #1: Note that ro is the 1/slope of iD-vDS characteristic. step #2: Define relationship between iD and vDS using (5.23). step #3: Take derivative of this function. step #4: Use above to define ro. Note that ro is defined in terms of iD, where iD does not take in to account channel length modulation EE 3110 Microelectronics I Suketu Naik 5.2.4. Finite Output Resistance in Saturation 43 Q: What is ? A: A device parameter with the units of V -1, the value of which depends on manufacturer’s design and manufacturing process. Figure 5.17 demonstrates the effect of channel length modulation on iD - vDS curves In short, we can draw a straight line between VA and saturation. Figure 5.17: Effect of vDS on iD in the saturation region. The MOSFET parameter VA depends on the process technology and, for a given process, is proportional to the channel length L. EE 3110 Microelectronics I Suketu Naik Exercise 5.6: Channel length modulation effect 44 NMOS transistor fabricated in an 0.4-m process with W = 16 m , L = 0.8 m,VA' = 50 V/m, n Cox= 200 A/V2. Q(a): Find VA and λ. Q(b): Find ID if VOV = 0.5 V and VDS = 1 V. Q(c): Find rO. Q(b): Find the change in ID if VOV is increased by 2 V EE 3110 Microelectronics I Suketu Naik 5.1.7. The p-Channel MOSFET 45 Figure 5.9(a): cross-sectional view of a p-channel enhancement-type MOSFET. structure is similar but current is opposite to the n-channel Complementary devices – two devices such as the pchannel and n-channel MOSFETs. EE 3110 Microelectronics I Suketu Naik 5.1.7. The p-Channel MOSFET 46 Q: What are main differences between n-channel and pchannel? A: Negative voltage applied to gate allowing path for current flow A: Threshold voltage is represented as Vtp |vGS| > |Vtp| EE 3110 Microelectronics I Suketu Naik 5.1.7. The p-Channel MOSFET 47 Q: What are main differences between n-channel and pchannel? A: Process transconductance parameters are defined differently k’p = pCox kp = pCox(W/L) A: The rest, essentially, is the same, but with reverse polarity... EE 3110 Microelectronics I Suketu Naik 5.1.7. The p-Channel MOSFET EE 3110 Microelectronics I 48 Suketu Naik 49 PMOS Equations: Table 5.2 ID I D ,tri 1 W 2 pCox VGS Vtp (1 VDS ) 2 L W 1 2 pCox VGS Vtp VDS VDS L 2 I D ,sat 2 1 W I D ,sat pCox VSG Vtp 1 VSD 2 L W 1 2 I D ,tri pCox V V V V SG tp SD SD L 2 EE 3110 Microelectronics I Suketu Naik 5.1.7. The p-Channel MOSFET (PMOS) 50 Q: Why is NMOS advantageous over PMOS? A: Because electron mobility n is 2 – 4 times greater than hole mobility p. Complementary MOS (CMOS) technology – is technology which allows fabrication of both N and PMOS transistors on a single chip. EE 3110 Microelectronics I Suketu Naik 5.2.5. Characteristics of the p-channel MOSFET 51 Characteristics of the pchannel MOSFET are similar to the n-channel, however with signs reversed. Please review section 5.2.5 from the text, with focus on table 5.2. EE 3110 Microelectronics I Suketu Naik iD-vDS Characteristics of the p-channel MOSFET Fig.1 (a) 52 Fig.1 (b) Fig.2(b) Fig.2(a) vGS + vDS + + vGD - Note: 1) In Fig.1(a) and (b) VSG > 0, VSD > 0 and iD > 0 2) In Fig.2 (a) and (b) VGS < 0, VDS < 0 and iD < 0 (opposite direction than in Fig. 1 EE 3110 Microelectronics I Suketu Naik PMOS Transistor 53 Exercise 5.7: PMOS Transistor Vtp = -1 V, kp'=pCox = 60A/V2 W/L = 10 (a) Find the range of VG in which transistor conducts (b) In terms of VG, find the range of VD for which transistor is in triode region (c) In terms of VG, find the range of VD for which transitor is in saturation region (d) Neglect channel length modulation effect and find values of |VOV| and VG EE 3110 Microelectronics I Suketu Naik 54 5.1.8. Complementary MOS or CMOS CMOS employs MOS transistors of both polarities more difficult to fabricate more powerful and flexible now more prevalent than NMOS or PMOS by itself Oxford University Publishing Microelectronic Circuits by Adel S. Sedra and Kenneth C. Smith (0195323033) EE 3110 Microelectronics I Suketu Naik 55 Figure 5.10: Cross-section of a CMOS integrated circuit. Note that the PMOS transistor is formed in a separate n-type region, known as an n well. Another arrangement is also possible in which an n-type body is used and the n device is formed in a p well. Not shown are the connections made to the p-type body and to the n well; the latter functions as the body terminal for the p-channel device. p-type semiconductor provides the MOS body (and allows generation of n-channel) Oxford University Publishing n-well is added to allow generation of p-channel SiO2 is used to isolate NMOS from PMOS Microelectronic Circuits by Adel S. Sedra and Kenneth C. Smith (0195323033) EE 3110 Microelectronics I Suketu Naik