Review of FET

advertisement

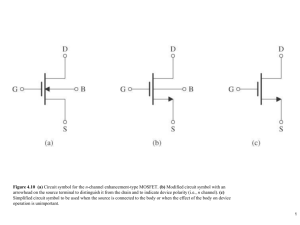

Field Effect Transistors Introduction • Two main types of FET: - JFET –Junction field effects transistor - MOSFET – Metal oxide semiconductor field effect transistor - D-MOSFET ~ Depletion MOSFET - E-MOSFET ~ Enhancement MOSFET • Similarities: -Amplifiers -Switching devices -Impedance matching circuits • Differences: -FET’s are voltage controlled devices whereas BJT’s are current controlled devices. -FET’s also have a higher input impedance, but BJT’s have higher gains. -FET’s are less sensitive to temperature variations and more easily integrated on IC’s. - FET’s are also generally more static sensitive than BJT’s. Construction and characteristics of JFET • N-channel device will appear as the prominent device with paragraph and section devoted to the impact of using a p-channel. • Major part of structure is n-type material. • Top of the n-type channel is connected through an ohmic contact to a terminal referred to as the drain (D) • The lower end-connected through an ohmic contact to a terminal referred as source (S) • P-type materials are connected together and to the gate (G) terminal. • JFET has two p-n junctions under nobias conditions. Construction and characteristics of JFET • JFET operation can be compared to a water faucet: • The source of water pressure – accumulated electrons at the negative pole of the applied voltage from Drain to Source • The drain of water – electron deficiency (or holes) at the positive pole of the applied voltage from Drain to Source. • The control of flow of water – Gate voltage that controls the width of the n-channel, which in turn controls the flow of electrons in the n-channel from source to drain. Construction and characteristics of JFET N-Channel JFET Circuit Layout JFET Operating Characteristics There are three basic operating conditions for a JFET: A. VGS = 0, VDS increasing to some positive value B. VGS < 0, VDS at some positive value C. Voltage-Controlled Resistor VGS = 0, VDS increasing to some positive value Three things happen when VGS = 0 and VDS is increased from 0 to a more positive voltage: • the depletion region between p-gate and n-channel increases as electrons from n-channel combine with holes from p-gate. • increasing the depletion region, decreases the size of the n-channel which increases the resistance of the n-channel. • But even though the n-channel resistance is increasing, the current (ID) from Source to Drain through the n-channel is increasing. This is because VDS is increasing. VGS = 0, VDS increasing to some positive value • The flow of charge is relatively uninhibited and limited solely by the resistance of the n-channel between drain and source. • The depletion region is wider near the top of both p-type materials. • ID will establish the voltage level through the channel. • The result: upper region of the p-type material will be reversed biased by about 1.5V with the lower region only reversed biased by 0.5V (greater applied reverse bias, the wider depletion region). VGS = 0, VDS increasing to some positive value • IG=0A p-n junction is reverse-biased for the length of the channel results in a gate current of zero amperes. • As the VDS is increased from 0 to a few volts, the current will increase as determined by Ohm’s Law. • VDS increase and approaches a level referred to as Vp, the depletion region will widen, causing reduction in the channel width. (p large, n small). • Reduced part of conduction causes the resistance to increase. • If VDS is increased to a level where it appears that the 2 depletion regions would touch (pinch-off) VGS = 0, VDS increasing to some positive value • Vp = pinch off voltage. • ID maintain the saturation level defined as IDSS • Once the VDS > VP, the JFET has the characteristics of a current source. • As shown in figure, the current is fixed at ID = IDSS, the voltage VDS (for level >Vp) is determined by the applied load. • IDSS is derived from the fact that it is the drain-to-source current with short circuit connection from gate to source. • IDSS is the max drain current for a JFET and is defined by the conditions VGS=0V and VDS > | Vp|. VGS = 0, VDS increasing to some positive value At the pinch-off point: •any further increase in VGS does not produce any increase in ID. VGS at pinch-off is denoted as Vp. • ID is at saturation or maximum. It is referred to as IDSS. • The ohmic value of the channel is at maximum. Typical JFET operation JFET modeling when ID=IDSS, VGS=0, VDS>VP VGS < 0, VDS at some positive value • VGS is the controlling voltage of the JFET. • For n-channel devices, the controlling voltage VGS is made more and more negative from its VGS = 0V level. • The effect of the applied negative VGS is to establish depletion regions similar to those obtained with VGS=0V but a lower level of VDS to reach the saturation level at a lower level of VDS. VGS < 0, VDS at some positive value • When VGS = -Vp will be sufficiently negative to establish saturation level that is essentially 0mA, the device has been ‘turn off’. • The level of the VGS that results in ID = 0 mA is defined by VGS = Vp, with Vp being a negative voltage for n-channel devices and a positive voltage or p-channel JFETs. • In this region, JFET can actually be employed as a variable resistor whose resistance is controlled by the applied gate to source voltage. • A VGS becomes more and more negative; the slope of each curve becomes more and more horizontal. VGS < 0, VDS at some positive value • The region to the right of the pinch-off locus of the figure is the region typically employed in linear amplifiers (amplifiers with min distortion of the applied signal) and is commonly referred to as the constant-current, saturation, or linear amplification region. Characteristic curves for Nchannel JFET Voltage-Controlled Resistor • The region to the left of the pinch-off point is called the ohmic region. • The JFET can be used as a variable resistor, where VGS controls the drain-source resistance (rd). As VGS becomes more negative, the resistance (rd) increases. ro rd (1 VGS VP )2 And as summary in practical… p-Channel JFETS p-Channel JFET acts the same as the n-channel JFET, except the polarities and currents are reversed. P-Channel JFET Characteristics As VGS increases more positively: • the depletion zone increases • ID decreases (ID < IDSS) • eventually ID = 0A Also note that at high levels of VDS the JFET reaches a breakdown situation. ID increases uncontrollably if VDS> VDSmax. JFET Symbols Transfer Characteristics • The transfer characteristic of input-to-output is not as straight forward in a JFET as it was in a BJT. • In a BJT, indicated the relationship between IB (input) and IC (output). • In a JFET, the relationship of VGS (input) and ID (output) is a little more complicated: VGS 2 ID IDSS(1 ) VP Transfer Characteristics Transfer Curve From this graph it is easy to determine the value of ID for a given value of VGS. Plotting the Transfer Curve Shockley’s Equation Methods. • Using IDSS and Vp (VGS(off)) values found in a specification sheet, the Transfer Curve can be plotted using these 3 steps: • Step 1: ID IDSS(1 • Solving for VGS = 0V: ID IDSS • Step 2: ID IDSS(1 • Solving for VGS = Vp (VGS(off)): ID 0 A VGS 2 ) VP VGS 0V VGS 2 ) VP VGS VP • Step 3: • Solving for VGS = 0V to Vp: ID IDSS(1 VGS 2 ) VP Plotting the Transfer Curve Shorthand method VGS ID 0 IDSS 0.3VP IDSS/2 0.5 IDSS/4 VP 0mA Specification Sheet (JFETs) Case Construction and Terminal Identification This information is also available on the specification sheet. MOSFETs MOSFETs have characteristics similar to JFETs and additional characteristics that make then very useful. There are 2 types: 1. 2. Depletion-Type MOSFET Enhancement-Type MOSFET Depletion-Type MOSFET Construction The Drain (D) and Source (S) connect to the to n-doped regions. These Ndoped regions are connected via an n-channel. This n-channel is connected to the Gate (G) via a thin insulating layer of SiO2. The n-doped material lies on a p-doped substrate that may have an additional terminal connection called SS. Depletion-Type MOSFET Construction • VGS is set to 0V by the direct connection from one terminal to the other. • VDS is applied across the drain-to-source terminals. • The result is an attraction for the positive potential at the drain by the free electron of the n-channel and a current similar to that established through the channel of the JFET. • In the figure, VGS has been set at a negative voltage (-1V) Depletion-Type MOSFET Construction • Negative potential at gate will tend to pressure electron towards the ptype substrate and attract holes from the p-type substrate. • Depending on negative bias established by VGS, a level recombination between electron and hoes will occur.--- it will reduce the number of free electron in the n-channel available for conduction. • The more negative bias, the higher the rate of recombination • ID decrease, negative bias for VGS increase Basic Operation A Depletion MOSFET can operate in two modes: Depletion or Enhancement mode. Depletion-type MOSFET in Depletion Mode Depletion mode The characteristics are similar to the JFET. When VGS = 0V, ID = IDSS When VGS < 0V, ID < IDSS The formula used to plot the Transfer Curve still applies: ID IDSS(1 VGS 2 ) VP Depletion-type MOSFET in Enhancement Mode Enhancement mode VGS > 0V, ID increases above IDSS The formula used to plot the Transfer Curve still applies: (note that VGS is now a positive polarity) ID IDSS(1 VGS 2 ) VP p-Channel Depletion-Type MOSFET The p-channel Depletion-type MOSFET is similar to the n-channel except that the voltage polarities and current directions are reversed. Symbols Enhancement-Type MOSFET Construction The Drain (D) and Source (S) connect to the to n-doped regions. These n-doped regions are connected via an n-channel. The Gate (G) connects to the p-doped substrate via a thin insulating layer of SiO2. There is no channel. The n-doped material lies on a p-doped substrate that may have an additional terminal connection called SS. Enhancement-Type MOSFET Construction • VGS=0, VDS some value, the absence of an n-channel will result in a current of effectively 0A • VDS some positive voltage, VGS=0V, and terminal SS is directly connected to the source, there are in fact 2 reversed-biased p-n junction between the n-doped regions and p substrate to oppose any significant flow between drain and source. • VDS and VGS have been set at some positive voltage greater than 0V, establishing the D and G at a positive potential with respect to the source • The positive potential at the gate will pressure the holes in the p substrate along the edge of the SiO2 layer to leave the area and enter deeper regions of the p-substrate • The result is a depletion region near the SiO2 insulating layer void of holes Enhancement-Type MOSFET Construction • The electrons will in the p substrate will be attracted to the +G and accumulate in the region near the surface of the SiO2 layer • The SiO2 layer and its insulating qualities will prevent the negative carriers from being absorbed at the gate terminal • VGS increase, the concentration of electrons near the SiO2 surface increase until eventually the induced n-type region can support a measurable flow between D and S • The level of VGS that results in the significant increase in drain current is called the threshold voltage, VT. • VGS increase beyond the VT level the density of the carriers in the induced channel will increase and ID also increase Enhancement-Type MOSFET Construction • If VGS constant and increase the level of VDS, ID will eventually reach a saturation level as occurred for the JFET • Applying Kirchoff’s voltage law to the terminal voltage of the MOSFET VDG = VDS- VGS • If VGS fixed at some value, 8V, VDS increased from 2 – 5V, the VDG will drop from 6V to -3V and the gate will become less and less positive with respect to the drain Enhancement-Type MOSFET Construction The Enhancement-type MOSFET only operates in the enhancement mode. VGS is always positive As VGS increases, ID increases But if VGS is kept constant and VDS is increased, then ID saturates (IDSS) The saturation level, VDSsat is reached. VDsat VGS VT Enhancement-Type MOSFET Construction To determine ID given VGS: I D k (VGS VT ) 2 where VT = threshold voltage or voltage at which the MOSFET turns on. k = constant found in the specification sheet. k can also be determined by ID(on) using values at a specific point and the formula: k (VGS(ON) VT) 2 VDsat VGS VT VDSsat can also be calculated: p-Channel Enhancement-Type MOSFETs The p-channel Enhancement-type MOSFET is similar to the nchannel except that the voltage polarities and current directions are reversed. Symbols Specification Sheet MOSFET Handling • MOSFETs are very static sensitive. Because of the very thin SiO2 layer between the external terminals and the layers of the device, any small electrical discharge can stablish an unwanted conduction. Protection: • Always transport in a static sensitive bag • Always wear a static strap when handling MOSFETS • Apply voltage limiting devices between the Gate and Source, such as back-to-back Zeners to limit any transient voltage. VMOS VMOS – Vertical MOSFET increases the surface area of the device. Advantage: •This allows the device to handle higher currents by providing it more surface area to dissipate the heat. •VMOSs also have faster switching times. CMOS CMOS – Complementary MOSFET p-channel and n-channel MOSFET on the same substrate. Advantage: Useful in logic circuit designs Higher input impedance Faster switching speeds Lower operating power levels Summary Table