Digital Design

advertisement

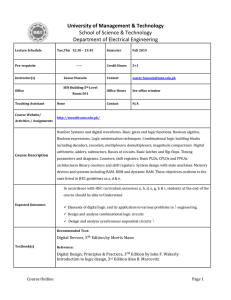

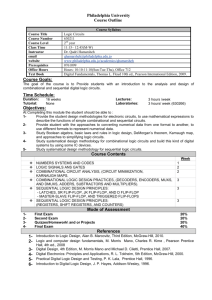

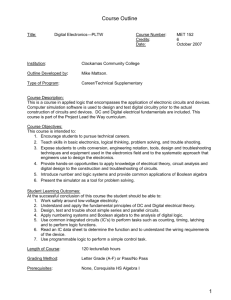

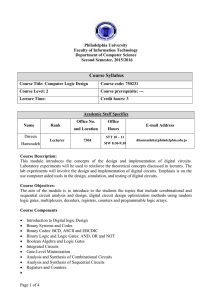

Digital Design Eng. Ruba A. Salamh Digital Design- SYLLABUS Instructor: Eng. Ruba A. Salamh Office: N501 Email: Rsalamah@iugaza.edu.ps http://site.iugaza.edu.ps/rsalamah Course Time and Location EELE 2313 Sat-Mon-Wed 12 – 1 L504 ECOM 2312 Sat-Mon-Wed 12 – 1 L504 Office hours will be 11:00-12:00 Sun and Tues. Course Description: Our goal in this course is to study the process digital circuit design. The course will begin with a review of the basics of binary system operation and the Boolean algebra. We will then study the details of binary logic gates and the concepts of logic minimization. Specifically, we will cover the MAP methods to simplify the Productof-Sum. Afterwards, we will examine techniques for design and analysis of combinational and synchronous sequential circuits. We will study combinational circuits such as Adder/Subtractor, Decoder, Encoder, Magnitude Comparator, and Multiplexer. This will be followed by an overview of sequential elements: latches and flops, and we will study sequential circuits such as registers and counters. We will also study memories and memory addressing and will review some of the programmable logics. Text Book: Digital Design (4th Edition), M. Morris Mano and Michael D. Ciletti. Digital Design Eng. Ruba A. Salamh Course Learning Outcomes: Students will be able to carry basic arithmetic operations in various number systems. Students will be able to apply basic Boolean postulates to simplify Boolean expressions. Students will be able to apply the K-map (karnaugh) map to simplify Boolean expressions. Students will be able to analyze and design various combinational logic circuits such as adders, subtractors, comparators, decoders, multiplexers and logic arrays. Students will be to analyze and design various sequential circuits such as registers, counters, RAM ( Random Access Memory ), and control circuits. Students will become familiar with the design of programmable devices such as PLA, PAL, and FPGA. COURSE SCHEDULE Number Systems & Arithmetic Boolean Algebra & Logic Operations Gate-Level Minimization Analysis & Design of Combinational Logic Circuits Analysis & Design of Synchronous Sequential Logic Circuits Registers & Counters Memory & Design with Programmable Logic Grading Policies & Scale Quizzes + Teaching Assistant control. Midterm exam Final 20% 30% 50% Important Notice: Sometimes (& suddenly) I will test you by giving Quizzes at the beginning of the lecture! - To solve it easily and to get the highest marks, you should always read the last two lectures before attending the class – Good Luck. Important Advice: From first day in the semester you should work very hard and you must activate your mind to think as much as you can!