Sill Torres: Microelectronics - Universidade Federal de Minas Gerais

advertisement

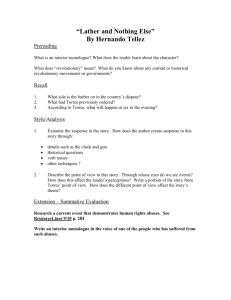

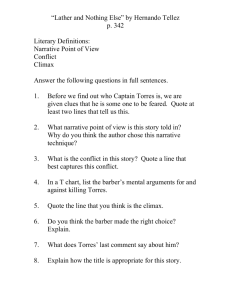

Microelectronics Today Problems and Solutions Frank Sill Torres OptMAlab / ART Universidade Federal de Minas Gerais (UFMG), Brazil Sill Torres: Microelectronics 1 About Me I’m German (from the NorthEast) Master / PhD. in Electrical Engenering / Microelectronics (Universität Rostock, Germany) Research areas: – Low Power Integrated Circuit (IC) Design – IC Design for Reliability (analog / digital) – Nanoelectronics – ... Sill Torres: Microelectronics 2 Outline 1. Areas of Microelectronics 2. Chip Design 3. State of the Art 4. Problems 5. Solutions 6. Microelectronics at UFMG and in Brazil Sill Torres: Microelectronics 3 Areas of Microelectronics Process/Devices All activities related to chip fabrication (Lithography, Etching, Ion Implantation,…) Design of new transistor devices (Bulk-CMOS, SOI, FinFet,…) Work on materials for semiconductors Clean room - UFMG MicroElectroMechanical Systems (MEMS), e.g. – Microphone of the iPhone4 – Micro-lenses Related laboratory at UFMG / EE – OptMAlab Knowles S1950 MEMS Die Sill Torres: Microelectronics 4 Areas of Microelectronics Circuits Design of integrated analog circuits Design of logic cells Design of integrated sensors and actuators Related laboratories at UFMG / EE Active pixel for digital camera (OptMAlab) – OptMAlab – OptMAlab / ART high-Vth/Tox low-Vth/Tox Advanced low leakage cell (OptMAlab/ART) Sill Torres: Microelectronics 5 Areas of Microelectronics Systems Design of integrated systems – Application Specific Integrated Systems (ASIC) – Processors – System on Chip (SOC) – Digital / Analog / Mixed-Signal Design of Intellectual Property (IP) blocks FPGA design Related laboratories at UFMG / EE Copyright: ELV.de – OptMAlab / ART – LSI – LabSCI Sill Torres: Microelectronics 6 Chip Design Sill Torres: Microelectronics 7 Chip Design Standard Designflow VHDL, SystemC … Textual description of the design Synthesis Mapping of the design onto logic cells Floorplanning Planing of basic structure of the chip (Size, I/O, power supply, blocks, …) Placement Placement of logic cell on chip Routing Wiring of logic cells Production Sill Torres: Microelectronics 88 ASIC Design Task Description Up to 25 years ago: chips developed on drawing board End of 80‘s: Hardware Description Languages (HDL) – Verilog - 1985 – VHDL - 1987 Newest developments – Object orientated approach – SystemC Sill Torres: Microelectronics 9 ASIC Design Representation with logic cells Called: Synthesis Conversion of high-level description into logic cells Happens automatic by special tools Sill Torres: Microelectronics 10 Chip Design Synthesis – Tool (Synopsys DesignVision) Sill Torres: Microelectronics 11 Chip Design Determination of Chip Sizes Called: Floorplanning Planning of basic structure of the chip (Size, Inputs/Outputs, power supply, blocks) What decides the chip size? PAD-limited Sill Torres: Microelectronics CORE-limited BLOCK-limited 12 Chip Design Floorplanning – Tool (Cadence Second Encounter) Menu Layer selection Tools Coordinates Overview window Sill Torres: Microelectronics Control output 13 Chip Design Placement Placement of logic cells Usually: Standard cells Uniform cell height Different widths Tool support Copyright: Weste, 2011 Copyright: Yu, UC Davies Sill Torres: Microelectronics 14 Chip Design Placement - Example Copyright: Yu, UC Davies Sill Torres: Microelectronics 15 Chip Design Routing Placing of wires that connect logic cells Two Phases: – Global Routing – Detailed Routing Tool support Sill Torres: Microelectronics 16 Chip Design Routing - Examples Ref.: Wikipedia Copyright: Yu, UC Davies Sill Torres: Microelectronics 17 Chip Design Fabrication Design project saved as file (e.g. GDS2) → sent to fab Fab: – Fabrication, packing, and testing – Very expensive (e.g. Intel 14 nm - USD 5 Billion, GlobalFoundries 28 nm – USD 4.6 Billion, source: Wikipedia) CEITEC S.A., Rio Grande do Sul (Work in Progress, 0.6 um) Sill Torres: Microelectronics 18 Chip Design Design Houses In the past – Chip designer and factories together – Intellectual Property belongs to factory Today – Chip designers and factories separate – Intellectual Property stays with designer Sill Torres: Microelectronics 19 State of the Art Sill Torres: Microelectronics 20 State of the Art Overview Technology sizes: starting from 22 nm Processors with 64 bit Multi-cores Processors for – Servers (Opteron, Xeon, …) – PCs (Core i3/i5/i7, Fusion, …) – Smartphones / Pads (ARM, Atom, ...) High integration of functionalities – Memory controller – Graphic card Sill Torres: Microelectronics 21 State of the Art Processors [Mill.] Transistors [Mill.] Transistors 130 nm 400 400 90 nm 300 300 100 100 0 0 100 nm Yonah 65 nm 151 Mill. 200 200 150 nm Technology Wolfdale 410 Mill. 500 500 Prescott 125 Mill. 45 nm 50 nm Northwood 55 Mill. Yonah, 151 Mill. 0 nm 2002 2002 Sill Torres: Microelectronics 2004 2004 Year Year 2006 2006 2008 2008 22 State of the Art Dimensions m 10 cm 100 nm 10 111mm cm µm µm Source: „Spektrum der Wissenschaften“ „22 nm“-Transistor Source: Intel Sill Torres: Microelectronics 23 Problems Sill Torres: Microelectronics 24 Problems Power Dissipation SoC Consumer Portable Power Trend [Source: ITRS, 2010 Update] Sill Torres: Microelectronics 25 Problems Power Density Nuclear Reactor → ←Hot Plate Source: http://cpudb.stanford.edu/ Sill Torres: Microelectronics 26 Problems Leakage MOS-Transistor: Basic Element Conducting: Closed (ideal): Closed (real): Current flow No Current Still current flow Dynamic power dissipation No power dissipation Until early 2000‘s dominating Sill Torres: Microelectronics (Leakage) Power dissipation 27 Problems Subthreshold Leakage Isub Vgs < >V Vthth Threshold Voltage Vth Gate – Transistor characteristic – If: „Gate-Source“-Voltage Vgs higher than Vth Gate Drain Source Source Current between Drain and Source Isub Drain – If: Vgs lower than Vth (ideal) No current Subthreshold leakage Isub – Leakage between Drain and Source when Vgs < Vth – Based on: Short Channels Diffusion Thermionic Emission Sill Torres: Microelectronics Diffusion high Concentration Low concentration 28 Problems Gate Leakage Igate Tunneling effect Potential Energy Energy Potential – Electromagnetic wave strikes at barrier: Reflection + Intrusion into barrier 0 – If thickness is small enough: Wave interfuses barrier partially: (Electrons tunnel through barrier) Gate oxide leakage Igate Igate – At transistors with Tox< 2 nm Gate Gateoxide Electrons tunnel through gate oxide Leakage current Sill Torres: Microelectronics x Tox Source Tox Drain 29 Problems Process Failures Occur at production phase Based on – Process Variations – Particles – … Source: Mak Sill Torres: Microelectronics 30 Problems Electromigration Transport of material caused by the gradual movement of ions in a conductor Top View Void Metal 1 Major failure mechanisms in interconnects Metal 1 Proportional to width and thickness of metal lines Inversely proportional to current density Whisker, Hillock Cross Section View Metal 1 Thick Oxide Metal 2 Source: Plusquellic, UMBC Sill Torres: Microelectronics 31 Problems Electromigration cont’d Void in 0.45mm Al-0.5%Cu line Source: IMM-Bologna Whiskers in Sn Source: EPA Centre Hillocks in ZnSn Source: Ku&Lin,2007 Sill Torres: Microelectronics 32 Problems Gate Oxide Breakdown Tunneling currents Wear out of gate oxide Creation of conducting path between Gate and Substrate, Drain, Source Depending on electrical field Source: Pey&Tung over gate oxide, temperature (exp.), and gate oxide thickness (exp.) Also: abrupt damage due to extreme overvoltage Sill Torres: Microelectronics Source: Pey&Tung 33 Problems Soft Errors Source: Automotive 7-8, 2004 1 In 70’s observed: DRAMs occasionally flip bits for no apparent reason Ultimately linked to alpha particles and cosmic rays Collisions with particles create electron-hole pairs in substrate These carriers are collected on dynamic nodes, disturbing the voltage Sill Torres: Microelectronics 34 Problems Soft Errors cont’d Internal state of node flips shortly If error isn’t masked by – Logic: Wrong input doesn’t lead to wrong output – Electrical: Pulse is attenuated by following gates – Timing: Data based on pulse reach flipflop after clock transistion wrong data FF FF FF FF Sill Torres: Microelectronics 35 Problems Delay [s] Drain current IDS [pA] Temperature Variations Temperature [°C] Threshold voltage Vth changes with temperature drain-source current changes delay changes Source: Burleson, UMASS, 2007 Sill Torres: Microelectronics 36 Problems Failures due to Increasing Delay FF Logic FF Data are processed before clock phase is over Clk Clock (Clk) VDD↓, Temp.↑, ... FF Clk Sill Torres: Microelectronics Logic too slow! → Data processing FF longer than clock phase → Wrong Data in next clock phase! 37 Solutions Sill Torres: Microelectronics 38 Solutions New Technologies For example: Intel Sill Torres: Microelectronics 39 Solutions Basics: Delay and Power versus VDD 10 5 8 Pdyn 4 td 6 3 4 2 1 2 0 0 0.8 1 1.2 1.4 1.6 1.8 2 2.2 Relative Pdyn Relative Delay td 6 2.4 Supply voltage (VDD) Dynamic Power can be traded by delay Sill Torres: Microelectronics 40 Solutions Adaptive Dynamic Voltage/Frequency Scaling (DVS/DFS) Slow down processor to fill idle time More Delay lower operational voltage Active Idle Active Idle Active 3.3 V 2.4 V Runtime Scheduler determines processor speed and selects appropriate voltage Transitions delay for frequencies <150s Potential to realize 10x energy savings E.g.: Intel SpeedStep, AMD PowerNow, Transmeta Longrun Sill Torres: Microelectronics 41 Solutions DVS/DFS with Transmeta LongRun % of max powerl consumption 100 90 80 70 60 50 40 30 20 10 0 300 300 Mhz 0.80 V Peak performance region Typical operating region 400 433 Mhz 0.87 V 500 533 Mhz 0.95 V 600 700 667 Mhz 1.05 V 800 800 Mhz 1.15 V 900 900 Mhz 1.25 V 1000 1000 Mhz 1.30 V Frequency (MHz) Source: Transmeta Sill Torres: Microelectronics 42 Solutions Clock Gating Most popular method for power reduction of clock signals and functional units Gate off clock to idle functional units Logic for generation of disable signal necessary Strong reduction of dynamic power dissipation clock R Functional e unit g disable Sill Torres: Microelectronics 43 Solutions Clock Gating: Example Without clock gating 30.6mW With clock gating 8.5mW 0 5 10 15 VDE 20 25 MIF DSP/ HIF Power [mW] 90% of FlipFlops clock-gated DEU 896Kb SRAM 70% power reduction by clock-gating MPEG4 decoder Source: M. Ohashi, Matsushita, 2002 Sill Torres: Microelectronics 44 Solutions Power-orientated Programming Switched Capacitance (nF) 14000 12000 10000 Others Functional Unit Pipeline Registers Register File 8000 6000 4000 2000 0 bubble.c heap.c quick.c Algorithms can differ in power dissipation Source: Irwin, 2000 Sill Torres: Microelectronics 45 Solutions Basics: Stack Effect Transistor stack: at least two transistors in a row Based on behavior of internal nodes: The more transistors are non-conducting (off) the lower the leakage Leakage Isub [nA] 10 8 6 4 2 0 1 2 3 4 Transistors off in stack Source: Roy, “Lecture” Sill Torres: Microelectronics 46 Solutions Sleep Transistors Idea: Insertion of additional transistors between logic block and supply lines sleep Vdd Virtual Vdd These transistors: connected with SLEEP-signal If circuit has nothing to do: SLEEP signal is active: Stack effect (additional off transistor in row to other) Mostly insertion only of 1 transistor Circuit sleep Virtual Vss Vss Source: Kaijian Shi, Synopsys Sill Torres: Microelectronics 47 Solutions Basics: Relation of Vth, Delay and Leakage Threshold Voltage Vth: – Influence on sub-threshold leakage Isub – Influence on delay of logic gates 160 120 55 Isub 50 45 80 40 40 0 0.25 35 0.27 0.29 0.31 0.33 0.35 Dealy [ps] Leakage- -Isub Isub [nA] [nA] Leakage Inverter (BPTM 65 nm) 30 0.37 Threshold Voltage [V] [V] Threshold VoltageVthNMOS VthNMOS Sill Torres: Microelectronics 48 Solutions Dual-Vth “LVT”- Cells Cells consist of transistors with low Vth Low delay High leakage For critical paths “HVT”- Cells Cells consist of transistors with high Vth Longer delay Low leakage For uncritical paths Leakage reduction at constant performance Sill Torres: Microelectronics 49 Solutions Dual-Vth Example LVT- Cells HVT- Cells Critical Path Sill Torres: Microelectronics 50 Solutions Triple Module Redundancy (TMR) Input Logic L A Copy of Logic L B Voter Output C Copy of Logic L Sill Torres: Microelectronics 51 Solutions Self Adaptive Design Extend idea of clock domains to Adaptive Power Domains Tackle static process and slowly varying timing variations Control VDD, Vth (indirectly by body bias), fclk by calibration at Power On Test inputs and responses fclk Test Module VDD Module VBB Sill Torres: Microelectronics 52 Solutions Reliability Enhancement via Sleep Transistors Basic idea: Reduction of degradation via module deactivation Problem: What to do at run-time? Module 1 Instance 1 Module 2 SLEEP Module 1 Instance 2 Sill Torres: Microelectronics MUX 53 Opportunities in Brazil and Activities at UFMG Sill Torres: Microelectronics 54 Opportunities in Brazil CEITEC S.A. – Design House and Chip factory (Rio Grande do Sul) Over 22 Design Houses – DHBH in Belo Horizonte – MINASIC in Itajubá – CTI, Eldorado, LSI-TEC, von Braun, … Many other companies, e.g.: – AEGIS / SEMIKRON: Power devices – SMART / HT Micron: Back-end for memories – FREESCALE: Design center Sill Torres: Microelectronics 55 Opportunities in Brazil cont’d Minas Gerais – InventVision - Optical Systems, FPGA – Jasper - Verification – CBS (wafer production) - planned – CMinas (MEMS) - planned – Foxconn (Displays) - planned Sill Torres: Microelectronics 56 Activities at UFMG / EE OptMAlab Laboratory for Optronics and Microtechnologies (OptMAlab) Located at PPGEE / UFMG Coordinator: Dr. Davies William de Lima Monteiro Adaptive Optics: wavefront aberration, components and systems Microelectronics: Analog Integrated-Circuit design custom pixels, image sensors and optical position-sensitive devices (PSDs) Micromachining: silicon wet processing micro-optics Ophthalmic Optics: technology and characterization of intraocular lenses Photovoltaics: alternative self-configurable cells Sill Torres: Microelectronics 57 Activities at UFMG / EE OptMAlab - IC for read-out for infrared sensor CMOS AMS 0.35µm Chip area: 12 mm2 3.3V e 5.0V > 90 pins > 60 structures Digital circuits Analog circuits Mixed-Signal Circuits Photo-diodes Photo-resistors Sill Torres: Microelectronics 58 Activities at UFMG / EE OptMA - ART Asic-ReliabiTiy (OptMAlab / ART) Extension of OptMAlab at PPGEE/UFMG Coordinator: Frank Sill Torres Dedicated to reliability in micro- and nanoelectronics applications Activities in the field of – Design for Reliability – Low Leakage / Low Power Chip Design – Development of CAD tools extensions – Robust Nanoelectronics More information: www.asic-reliabity.com Sill Torres: Microelectronics 59 Activities at UFMG / EE OptMA – ART / Reliable Adder CMOS AMS 0.35µm Chip area: 1 mm2 3.3V > 10 pins Test structures Modified logic cells Sleep Transistors Prepared for Controlled Destruction Sill Torres: Microelectronics 60 LSI – Laboratório de Sistemas Inteligentes Projeto: Desenvolvimento de um Sistema de Determinação de Atitude com Tolerância a Falhas para Satélites de Baixa Órbita. Projeto Financiado pela AEB – Programa UNIESPAÇO – Colaboradores: INPE, UFABC, OptMa Síntese do Projeto: – O que é Atitude – Satélites que operam em Baixa Órbita Terrestre – O ambiente hostil a que os CIs são colocados em funcionamento. – Condições limitadoras: alta precisão de apontamento, baixa potência, baixo peso, baixo custo e confiabilidade 99,99999% durante a missão. Sill Torres: Microelectronics 61 LSI – Laboratório de Sistemas Inteligentes Sill Torres: Microelectronics 62 LSI – Laboratório de Sistemas Inteligentes Áreas de atuação da Microeletrônica: – Entender e modelar o efeito de falhas em CIs. Diversidade de Dispositivos Diversidade de Arquiteturas Diversidade de Ambientes e Situações – Emular o efeito de falhas em CIs. – Mitigar o efeito das falhas dos CIs nos Sistemas que os compreendem Técnicas de Tolerância a Falhas Sill Torres: Microelectronics 63 LSI – Laboratório de Sistemas Inteligentes Equipe atual: – Fernando Esquírio Torres (bolsista de mestrado CPDEE) – Thalles Hermes R. Gomes (bolsista PET-EE) – Wagno Alves Bragança J. (bolsista PET-EE) – Bruno Henrique S. Guimarães (voluntário IC-EE) – ... ???? Contato: – Prof. Ricardo de Oliveira Duarte Email: ricardoduarte@ufmg.br Sala pessoal: 2521 Sala do LSI: 2515 Sill Torres: Microelectronics 64 LSI – Laboratório de Sistemas Inteligentes Sill Torres: Microelectronics 65 Thank you! franksill@ufmg.br OptMAlab / ART www.asic-reliability.com Sill Torres: Microelectronics 66 Solutions Network on Chip Sill Torres: Microelectronics 67