Logic Synthesis - UCSD VLSI CAD Laboratory

advertisement

CSE241A

VLSI Digital Circuits

Winter 2003

Recitation 3: Synthesis

CSE241 Synthesis Overview.1

Kahng & Cichy, UCSD ©2003

Logic Synthesis: explained

Logic synthesis:

HDL

Process of transforming Hardware Description Language (HDL)

code into a logic circuit

VDHL

Verilog (we’ll only use Verilog RTL)

The circuitry:

Structural-level HDL netlist

Components from a technology specific library

CSE241 Synthesis Overview.2

Kahng & Cichy, UCSD ©2003

Logic Synthesis

Logic synthesis converts a software code into a connected set a

standard cells

Real cell properties must be accounted in order to insure that

the actual circuit will perform correctly:

Propagation Delay through cells

Connection Delay between cells

Load Capacitance

Drive Resistance

Slew rate (10%- 90% v)

Area of Cells

Clock rates

Setup & Hold times

Power Consumption

CSE241 Synthesis Overview.3

Kahng & Cichy, UCSD ©2003

Ideal is converted into Real

Sel

case (Sel)

2'b00

00

B

01

10

10

11

11

: status <= A;

2'b01

: status <= B;

2'b10

: status <= 2'b10;

2'b11

: status <= 2'b11;

endcase

A

status

Mux4x1 1x Drive Strength

Area: 12microns

Max Transition 1.0 ns

Input Pin capacitance: .0015pf

Output Pin Max Load: .45 pf

Cell Delay (A -> Z) with .455pf load

and .5ns slew is .3ns

CSE241 Synthesis Overview.4

Kahng & Cichy, UCSD ©2003

Synthesis Related File Types

Script file

.scr

Verilog file

.v

Synthesized Verilog file

.sv

VHDL file

.vhd

Synthesized VHDL files

.svhd

EDIF file

.edif

Synopsys database file

.db

Reports

.rpt

Log file(standard for most tools).log

CSE241 Synthesis Overview.5

Kahng & Cichy, UCSD ©2003

Synthesis Related File Types

Library File

.lib

TCL script file

.tcl

Ambit Library Format file

.alf

Ambit Database file

.adb

Magma Database file

.volcano

Command file

.cmd

Standard Delay Format file

.sdf

Standard Parasitics Exchange

Format

CSE241 Synthesis Overview.6

.spef

Kahng & Cichy, UCSD ©2003

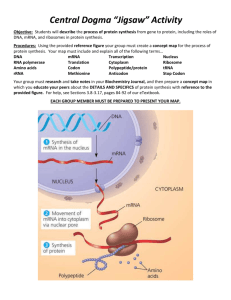

Synthesis Data Flow

HDL

Code

Tech

Library

2

Constraints

1

3

Synthesis

Tool

Gate Level Netlist

CSE241 Synthesis Overview.7

Kahng & Cichy, UCSD ©2003

Step 1: Synthesis Setup

Setup accomplished through setup files and global shell

variables

Synopsys (.synopsys_dc.setup & script)

Setup directories (example: Project is called Lab2)

Script

Reports

Libaries

Verilog

CSE241 Synthesis Overview.8

(/ee260b/ee260b/lab2/script)

(/ee260b/ee260b/lab2/reports)

(/ee260b/ee260b/lab2/libraries) (local)

(/ee260b/ee260b/lab2/src)

Kahng & Cichy, UCSD ©2003

Example of .synopsys_dc.setup

Company

=

“UCSD”

Designer

=

“Ben Cichy”

Technology =

“0.13 micron”

Search_path = search_path + {“.” “./libraries/”}

Target_library = {lsi_10k.db}

Link_library

= {“*” lsi_10k.db}

Symbol_library = {lsi_10k.sdb}

//work library for intermediate files

Define_design_lib

CSE241 Synthesis Overview.9

work

-path work

Kahng & Cichy, UCSD ©2003

Reading a Library

Synopsys: read_db msi_10k.db

•

If the .db library file doesn’t exist then it must be created from

the .lib library file (vendor supplied)

•

•

.lib is readable by the user , .db is internal format

•

Library Compiler

Use library compiler to create the.db.

msi_10k.lib -> msi_10k.db ]

-

[ libcompile

Checks the .lib for errors

Translates to .db

CSE241 Synthesis Overview.10

Kahng & Cichy, UCSD ©2003

Purpose of the Library

The Library contains the cells of the technology (.18,

.13u)

Cells are “Building Blocks” for the circuit

Must use technology library for physical properties

Synthesis tools considers properties and function of cells

The key properties:

-

Cell delay

Rise/fall transitions

Capacitive load

Drive strength

Area and power

DelayTotal = DelayCell + DelayWire

CSE241 Synthesis Overview.11

Kahng & Cichy, UCSD ©2003

Contents of a Library

Units (V, A, pW, KOhm, nS, etc)

Default parameters

Nominal Parameters (PVT)

Operating Conditions

K Factors

Wireload Models

Worst Case /Best Case

Scaling factors

Max transition

Input pin cap

Wireload mode

Operating condition

Max fanout

Estimate for fan-in, fan-out

Look-up table templates

Cells: all properties & attributes, Delay Tables, Rise/Fall

Transition Tables, Power Tables

CSE241 Synthesis Overview.12

Kahng & Cichy, UCSD ©2003

Wireload model

wire_load("45Kto75K") {

capacitance : 0.000070;

resistance : 0.000042;

area : 0.28;

slope : 40.258665;

fanout_length(1, 40.258865);

fanout_length(2, 80.517750);

fanout_length(3, 120.776600);

fanout_length(4, 161.045450);

fanout_length(5, 241.543200);

fanout_length(6, 322.070900);

fanout_length(7, 402.587600);

}

CSE241 Synthesis Overview.13

Kahng & Cichy, UCSD ©2003

Reading RTL

Synthesis tool reads the RTL files.

The synthesis tool checks for

Syntax errors

Enters design into synopsys .db format

Command:

Synopsys: analyze –format verilog –lib work

./src/example.v

CSE241 Synthesis Overview.14

Kahng & Cichy, UCSD ©2003

Generic Tech Generation

Synopsys: elaborate example –arch “BEHAVIORAL” –lib work

Generates Control Data Flow Graphs (CDFGs)

Performs high level logic optimizations

Performs resource allocation

Adders

Multipliers

Produces a table of the resources that are used

Generates a hierarchical netlist

Generic” components (gtech.db)

No timing or electrical properties in the design

Genlib cells

CSE241 Synthesis Overview.15

Kahng & Cichy, UCSD ©2003

Design Error Checking

Check:

Warnings and Errors in the log file

Examples of Warnings and Errors:

Signals missing in sensitivity lists

Shorted inputs or outputs

Unused & Undriven inputs and outputs

Blackboxes

Dangling, undeclared and undriven wires

Unsynthesizeable or ignored HDL constructs (# delay, etc.)

- Might need linting tool

Latches

CSE241 Synthesis Overview.16

Kahng & Cichy, UCSD ©2003

Constrain the Design

Constraints define the parameters of the block which the synthesis

tool must meet.

Constraints define the relationships between the block and the rest

of the chip.

These items are defined:

Clocks

Arrival times

Loading on the output pins

Drive resistance on the input pins

Timing exceptions

Operating Conditions

Wireload model mode

CSE241 Synthesis Overview.17

Kahng & Cichy, UCSD ©2003

Constraints: Commands

Synopsys

Clocks

create_clock

Input Delay

set_input_delay

Output Delay

Output Load

set_output_delay

set_load

Input Drive

Resistance

set_driving_cell

False Paths

set_false_path

Multicycle Paths

set_multicycle_path

Operating

Conditions

set_operating_conditions

Wireload Model

set_wire_load

CSE241 Synthesis Overview.18

Kahng & Cichy, UCSD ©2003

Constraints: set performance targets

Synthesized design:

Bounded by constraints

Input/Output, clk; all bound design

The RTL defines the functionality of design

The library contains the building blocks for building the design

The constraints tell the synthesis tool the timing and electrical

relationships between the block and the chip

CSE241 Synthesis Overview.19

Kahng & Cichy, UCSD ©2003

Optimization

Optimization:

The generic netlist

Iteratively

Mapped to the cells in the tech library a

Timing is computed (with a clocked design)

Tools restructures design until timing is met

Targets:

Power

Area

Timing (cycle time)

Note: See Lecture 5 for more details

Command:

Synopsys: compile

CSE241 Synthesis Overview.20

Kahng & Cichy, UCSD ©2003

Timing Reports

Timing reports:

Are created in synopsys script

Generate longest paths

Timing: set-up/hold-time violations

Timing not met:

Reconstrain design

Error in netlist

Too long (depth) logic path

CSE241 Synthesis Overview.21

Kahng & Cichy, UCSD ©2003

Example 1 of a Timing Report

Operating Conditions: WCCOM

Wire Load Model Mode: top

Library: lsi_10k

Startpoint: crcprv_reg[0]

(rising edge-triggered flip-flop clocked by clk)

Endpoint: err_reg (rising edge-triggered flip-flop clocked by clk)

Path Group: clk

Path Type: max

Des/Clust/Port

Wire Load Model

Library

-----------------------------------------------crcscram16bi

10x10

lsi_10k

Point

Incr

Path

----------------------------------------------------------clock clk (rise edge)

0.00

0.00

clock network delay (ideal)

0.00

0.00

crcprv_reg[0]/CP (FD2)

0.00

0.00 r

crcprv_reg[0]/QN (FD2)

3.36

3.36 f

U56/Z (NR2P)

1.41

4.77 r

U45/Z (ENP)

2.25

7.02 f

U112/Z (EOP)

2.07

9.09 f

U52/Z (EOP)

2.25

11.34 f

U151/Z (MUX21LP)

1.11

12.46 r

U14/Z (EN3)

3.67

16.13 f

U86/Z (EOP)

2.17

18.30 f

U49/Z (EOP)

2.07

20.38 f

U27/Z (ND6)

2.51

22.88 r

err_reg/TE (FD2S)

0.00

22.88 r

data arrival time

22.88

clock clk (rise edge)

10.00

10.00

clock network delay (ideal)

0.00

10.00

err_reg/CP (FD2S)

0.00

10.00 r

library setup time

-1.25

8.75

data required time

8.75

----------------------------------------------------------data required time

8.75

data arrival time

-22.88

----------------------------------------------------------slack (VIOLATED)

-14.13

CSE241 Synthesis Overview.22

Kahng & Cichy, UCSD ©2003

Other Reports

Log file output:

Area Report

Command window shows errors per excuted command (gui)

Log file (dc_shell) shows execution trace

Just make sure design is not too large

Don’t try to overoptimize in DC

Hierarchy Report

Library Report

State Machine (FSM) report

CSE241 Synthesis Overview.23

Kahng & Cichy, UCSD ©2003

Example of Area Report page1

****************************************

Report : area

Design : crcscram16bi

Version: 2002.05-SP1

Date : Thu Jan 23 02:43:31 2003

****************************************

Library(s) Used:

lsi_10k (File: /space/software/tools/synopsys/dc/libraries/syn/lsi_10k.db)

Number of ports:

Number of nets:

Number of cells:

Number of references:

41

187

159

27

Combinational area:

466.000000

Noncombinational area:

88.000000

Net Interconnect area:

undefined (Wire load has zero net area)

Total cell area:

Total area:

554.000000

undefined

CSE241 Synthesis Overview.24

Kahng & Cichy, UCSD ©2003

Final Netlist Generation

Synopsys:

Write verilog netlist

write –format verilog –hierarchy –output

example.mapped.sv

Write synopsys database file

write –hierarchy –output example.mapped.db

CSE241 Synthesis Overview.25

Kahng & Cichy, UCSD ©2003

Compilation Strategies

Top-Down Compilation Strategy

Method: Constraints are applied at the top level and the entire chip

is synthesized.

Time-Budgeting Compilation Strategy (Bottom-Up Approach)

Method: Constrain and synthesize each sub-block. Then import

results and synthesize top level.

Compile-Characterize-Write Script-Recompile Strategy (CCWSR)

Method: Apply timing constraints to top level. Let tool propagate

timing constraints to lower level blocks (i.e. let the tool do a timing

budget). Have tool generate a constraint script on the characterized

sub-blocks. Synthesize sub-blocks then synthesize top level block.

CSE241 Synthesis Overview.26

Kahng & Cichy, UCSD ©2003

Top-Down Compilation Strategy

Advantages

•

•

Only top level constraints are needed.

Better results are achieved because optimization is performed

across the entire design.

Disadvantages

•

•

Long compile times

•

If the design contains multiple clocks or generated clocks the

tool doesn’t perform as well

A small change in the design requires that the entire design be

re-synthesized

CSE241 Synthesis Overview.27

Kahng & Cichy, UCSD ©2003

Time-Budgeting Compilation Strategy

Advantages

•

Easier to manage because each sub-block has it’s own

constraint and synthesis scripts.

•

A change in a sub-block does not necessary require that other

sub-blocks be resynthesized.

•

Multiple and generated clocks are more easily handled.

Disadvantages

•

•

Each block is individually synthesized

•

Very tedious and time-consuming to update and maintain

multiple scripts.

•

Some critical paths don’t become apparent until top level

compile is performed. (unobservability of critical paths)

•

A final incremental compile of entire design may be necessary

in order to remove DRC errors.

May not produce optimal design. Prone to error due to

manually specified time budgets.

CSE241 Synthesis Overview.28

Kahng & Cichy, UCSD ©2003

The Automated Chip Synthesis Approach

Advantages

•

•

•

Less CPU memory is needed to do synthesis

Automated Chip Synthesis (ACS) can create subblock

constraint budgets based on the top-level constraints

because budgeting is an integrated part of the ACS flow. It

can see across the hierarchy like the top-down methodology.

Individual scripts are created for each sub-block

Disadvantages

•

•

•

Tool generated constraint scripts are not very readable

A change in a lower level sub-block requires that the entire

design be re-synthesized

May be difficult to achieve convergence between sub-blocks

because of a “Ping-Pong” effect while synthesizing subblocks.

Synopsys ACS White Paper

CSE241 Synthesis Overview.29

Kahng & Cichy, UCSD ©2003

Synthesizeable Verilog Constructs

(For Verilog 1997)

always

endcase

module

repeat

and

endmodule

nand

supply0

assign

endfunction

negedge

supply1

begin

endtask

buf

for

nor

tri

bufif0

function

not

wait

bufif1

if

notif0

wand sometimes

case

inout

notif1

while

casex

input

or

wire

casez

integer

output

wor

default

large

parameter

xnor

else

macromodule

posedge

xor

end

medium

reg

CSE241 Synthesis Overview.30

task

Kahng & Cichy, UCSD ©2003

Ignored Keywords

<delay specifications>

scalared, vectored

small, large, medium

specify

time (some tools treat these as integers)

weak1, weak0, highz0, highz1, pull0, pull1

$keyword (some tools use these to set synthesis

constraints)

wait (some tools support wait with a bounded condition)

CSE241 Synthesis Overview.31

Kahng & Cichy, UCSD ©2003

Unsupported Constructs

<global variables>

= = =, != =

cmos, nmos, rcmos,

rnmos, pmos, rpmos

deassign

fork, join

forever, while

initial

pullup, pulldown

release

repeat

rtran, tran, tranif0, tranif1, rtranif0, rtranif1

table, endtable, primitive, endprimitive

defparam

event

force

CSE241 Synthesis Overview.32

Kahng & Cichy, UCSD ©2003

Common Synthesis Problems

Latches

Setup Time Violations/ Hold Time Violations

Poor Constraints

Only real #s through place and route

Slow run-times

What are the specifications?

Inaccuracy of Wireload models

RTL, flip-flop designs

Multiple Clock domains correctly

Unassagined statements

Flat design

Achieving Timing Closure

Many problems: constraints, RTL design, library, routing

CSE241 Synthesis Overview.33

Kahng & Cichy, UCSD ©2003

Timing Closure

Timing problem:

Can’t reach closure

to rapidly achieve timing closure on a design is a HUGE

PROBLEM for semiconductor industry

A timing closure problem exists when all timing

violations in a design cannot be eliminated despite

multiple synthesis and place & route iterations

The timing closure problem occurs for a few reasons

•

•

•

Poor design practices

Inaccurate wireload models

No placement information used during synthesis; therefore

inaccurate connection delays

CSE241 Synthesis Overview.34

Kahng & Cichy, UCSD ©2003