STRJ WG1_tablesWdescription0404

advertisement

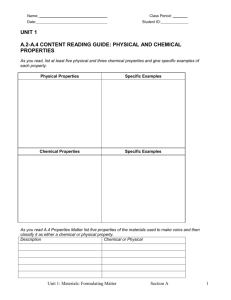

Proposed Roadmap Tables on SOC Design Productivity, SOC Low Power, and DSM related issues STRJ-WG1 March 2000 February 9,2000 - 1 STRJ-WG1 Contents (1)SOC Design Productivity Assumptions and study reaching to the table SOC Design Productivity Table (2)SOC Low Power Assumptions and study reaching to the table SOC Low Power Table Potential solution map P.3 - P.9 P.10 P.11 - P.17 P.18 P.19 - p.20 (3)DSM Related Issues An overall DSM requirements table P.21 - p.22 Assumptions and study reaching to the table for each DSM issue those are Crosstalk noise, RC delay, EMI, IR drop and Electro-migraton P.23 - p.30 February 9,2000 - 2 STRJ-WG1 Design Productivity SOC Design Productivity Premises Technology Node, ASIC Usable Transistors, and DRAM capacity conform to ITRS99 ORTC. Die size remains around 10mm Application is not specified, but surely it is high-end SOC in each generation. Prospects Logic gate count ratio continuously decreases from 80%(1999) thru 50%(2002), 35%(2005), into 15%(2011). Contrarily, re-use circuit ratio within Logic gate count grows from 20% (1999), thru 50%(2002), 70%(2005), to be 90%(2011) . Power supply voltage goes down from 1.5V(1999) to 0.5V(2011) . Operation frequency goes up from 150MHz(1999) to 2000MHz(2011) . February 9,2000 - 3 STRJ-WG1 Design Productivity SOC Design Productivity(cont.) Assumptions Total design resource is in proportion to size of newly designed circuit, e.g. 1Man*Year as 360Kgates. There now exists approximately 50% design overhead for re-use circuit, namely it costs 50% of design resource with same size newly designed circuit. Contribution from both productivity improvement for Newly designed circuit and Overhead reduction for Re-use circuit are considered as gate size reduction for each circuit in accordance with amount of improvement and overhead reduction, respectively. February 9,2000 - 4 STRJ-WG1 Design Productivity SOC Design Productivity(cont.) Productivity Requirement Total required design resource is unchangingly kept around 10 Man*Year. Solution to be accomplished Both 30% improvement per every 3 years for newly designed circuit and 30% improvement per every 3 years for design overhead for re-use circuit are needed to be accomplished. February 9,2000 - 5 STRJ-WG1 Design Productivity SOC Design Productivity(cont.) SOC consists of Logic blocks and existing hard IP(mainly Memory) Logic block Existing hard IP Each logic block can be implemented by newly designed portion and re-use portion such as IPs Newly designed portion Re-use portion February 9,2000 - 6 STRJ-WG1 Design Productivity SOC Design Productivity(cont.) Total logic gate count and Newly/Re-use ratio Total gate count and Logic/Non-Logic ratio MGates 35 MGates 250 30 200 25 150 20 100 15 50 10 5 0 1999 2002 2005 Logic Non-Logic February 9,2000 - 7 2011 0 1999 2002 2005 2011 New Re-use STRJ-WG1 Design Productivity SOC Design Productivity(cont.) How to derive “Total Design Resource” and “Target Design Resource” Total Design Resource( M gates) = #(Newly designed circuit) x [Productivity improvement(%)] + #(Re-use circuit) x [Overhead in Re-use circuit(%)] Target Design Resource( Man * Year) = (Total Design Resource) / (Normalized unit Man*Year productivity) here, “Normalized unit Man*Year productivity” is assumed as 0.36M gates (Ex.) in 2005 Total Design Resource( M gates) = (11.64 x (1 - 0.7) ) x 0.49 + (11.64 x 0.7 ) x 0.24 = 3.67 M gates Hence, Target Design Resource( Man * Year) = 3.67 / 0.36 = 10.19 Man * Year February 9,2000 - 8 STRJ-WG1 Design Productivity SOC Design Productivity(cont.) Man*Years 50 45 40 35 30 25 20 15 10 5 0 1999 2002 2005 Target No-imp Case A 2011 Case B No-imp : in case of No improvement Case A : in case of achieving improvement only for Newly designed circuit Case B : in case of achieving improvement only for Re-use overhead February 9,2000 - 9 STRJ-WG1 Design Productivity SOC Design Productivity Table Unit 2005 2011 1999 2002 180 130 100 20 54 133 811 (*1) Technology Node nm ASIC Usable Transistors M Tr./cm2 Logic gate count ratio in area % M gates M bits/cm2 M bits 80% 50% 35% 4.00 200 6.75 525 11.64 1,230 15% 30.41 7,510 (*1) 16 105 319.8 2,553 V MHz 1.5 150 1 20% 1.2 400 1.7 50% 0.9 1000 2.9 70% 0.5 2000 7.6 90% Newly designed circuit Productivity improvement % Resource for Newly designed(A) M gates 3.20 100% 3.20 3.38 70% 2.36 3.49 49% 1.71 3.04 24.% (*2) 0.73 Overhead in Re-use circuit Resource for Re-use circuit(B) Total Design resource(A+B) % M gates M gates 50% 0.40 3.60 35% 1.18 3.54 24% 2.00 3.67 12% (*3) 3.29 4.02 Target Design Resource Man*Years 10 9.8 10.2 11.2 Logic Gate count DRAM (Production) Embedded Memory size Power supply voltage Operation Frequency Design Resource Re-use circuit ratio (ratio) % M gates (*1) ITRS‘99 ORTC (*3) 30% off / 3 years improvement February 9,2000 - 10 50 (*2) 30% off / 3 years improvement STRJ-WG1 Low Power SOC Low Power Premises & Prospects Technology Node, ASIC Usable Transistors, DRAM capacity, and Power Supply Voltage conform to ITRS99 ORTC. Application is not specified, but surely it is high-end SOC in each generation. Other premises or prospects are consistent with those of “SOC Design Productivity”, such as ; Die size remains around 10mm Logic gate count ratio continuously decreases from 80%(1999) thru 50%(2002), 35%(2005), into 15%(2011) . Operation frequency goes up from 150MHz(1999) to 2000MHz(2011) . February 9,2000 - 11 STRJ-WG1 Low Power SOC Low Power(cont.) Assumptions Power consumption follows a basic well-known formula, that is Power ∝ C * V * V * f . “C” can be decomposed into “size factor” and “process factor”. Total transistor count and technology node represents “size factor” and “process factor”, respectively. “V*V” is considered as “voltage factor”, and it is just internal voltage. Also, “f” is considered as “frequency factor”, and it is just max frequency. “total power trend” is defined as relative amount of power consumption for each year(2002, 2005, and 2011) comparing each of above four “factor” for 1999 as unit(=1). February 9,2000 - 12 STRJ-WG1 Low Power SOC Low Power(cont.) Assumptions(cont.) “total power trend” is derived by the following calculation, “total power trend” = “size factor” x “process factor” x ”voltage factor” x “frequency factor” For “size factor”, constant coefficient 0.85 is applied to Memory portion, while 1.0 to Logic portion. Current SOC power consumption is assumed around 3W. February 9,2000 - 13 STRJ-WG1 Low Power SOC Low Power(cont.) Low Power Target Current power consumption(around 3W) should be kept at the minimum level. Ultimate goal is to achieve 0.5W in any technology node generation. A Scenario for solution to keep 3W By virtue of a set of potential low power technology, reduction for each “factor” in the following table is needed to be realized. Size factor Process factor Frequency factor Voltage factor February 9,2000 - 14 2002 50% 2011 70% 10% 2005 60% 20% 25% 17% 50% 33% 60% 40% 30% STRJ-WG1 Low Power SOC Low Power(cont.) How to derive “Total Power trend” and “Power estimation” Total Power trend = “size factor” x “process factor” x ”voltage factor” x “frequency factor” Power estimation (W) = (Total Power Trend) x 3W (Ex.) in 2002 Total Power trend = 3.93 x 0.72 x 0.64 x 2.67 = 4.84 Hence, Power estimation( W ) = 4.84 x 3 = 14.52 W February 9,2000 - 15 STRJ-WG1 Low Power SOC Low Power(cont.) Total Power Trend with No Low Power Solution Total Power Trend with Low Power Solution Scenario to keep 3W 100 100 10 10 1 1999 2002 2005 2011 volatage frequency 1 1999 2002 2005 2011 0.1 0.1 0.01 size February 9,2000 - 16 process voltage frequency total size process total STRJ-WG1 Low Power SOC Low Power(cont.) 120 100 80 W 60 40 20 0 1999 2002 W/O Solution February 9,2000 - 17 2005 2011 W/ Solution STRJ-WG1 Low Power SOC Low Power Table logic tr count memory tr count total tr count size factor(logic*1.0+mem*0.85) factor reduction technology node process factor factor reduction max frequency frequency factor factor reduction internal voltage voltage factor voltage reduction total power trend estimation target Low Power Spec switching activity external voltage battery February 9,2000 - 18 unit Mtr Mtr Mtr % nm % MHz % V % W W current 16 16 32 1 3.93 0 180 1.00 0.72 0 150 1.00 2.67 0 1.5 1.2 1 0.64 0 1 4.84 3 14.52 0.5 % 1.8 V 1.7~5.0 Wh/kg 120~130 2.66 2002 27 105 132 → 130 → 400 → → → → → 0.5 1.96 50 10.76 2005 46.55 319.8 366.4 → 0.65 10 0.56 100 → 2.00 6.67 25 1.0 0.9 0.44 0.36 17 1.13 14.34 3.40 43.02 → 2.61 1.2~5.0 140~150 2.7 1000 → → → → → 0.5 4.30 60 0.44 20 2011 121.7 2553.4 2675.1 77.43 → 0.28 3.33 13.33 50 0.6 0.5 0.16 0.11 33 1.02 31.87 3.06 95.60 → 2.67 1.2~5.0 200~250 1.85 50 → 2000 → → → → → 0.5 23.23 70 0.19 30 5.33 60 0.3 0.04 40 0.96 2.89 → 0.96 0.9~5.0 400~500 STRJ-WG1 Low Power SOC Low Power Design - Potential Solution Map - February 9,2000 - 19 STRJ-WG1 Low Power SOC Low Power Design - Potential Solution Map - What this figure means …. Trade-off line between operation frequency and size(Mtr) is put for each Technology node under the condition to accomplish 0.5W power consumption. A set of potential low power technology is overlaid in accordance with those contribution area and degree of range. Each potential technology is classified into three types( speed, size, and all ) with respect to main contribution. February 9,2000 - 20 STRJ-WG1 DSM DSM Related Issues Overall Premises & Prospects Technology Node and Power Supply Voltage conform to ITRS99 ORTC. Other premises or prospects are consistent with those of “SOC Design Productivity”, such as ; Die size remains around 10mm Operation frequency goes up from 150MHz(1999) to 2000MHz(2011) . Wiring metal is assumed Al till 2002 and Cu after 2005. Issues to be examined Crosstalk noise, RC delay, EMI, IR Drop, and ElectroMigration For each issue, “estimated value” will be examined in contrast to “required value” at each Technology node. February 9,2000 - 21 STRJ-WG1 DSM An overall DSM requirements table Base data/Condition (table 2-1-4-1) DSM requirements unit 1999 2002 2005 nm 180 130 100 50 Nominal Ion [25c,NMOS,low power] uA/um 490 490 490 490 Nominal Ion [25c,PMOS,low power] uA/um 230 230 230 230 ITRS99 Table28 V 1.5 1.2 0.9 0.6 STRJ-WG1/LP-SWG Frequency MHz 150 400 1000 2000 STRJ-WG1/LP-SWG Die size cm□ 1 1 1 1 STRJ-WG1/LP-SWG 2 2.1 1.7 2.1 STRJ -WG4 Metal effective resistivity μΩcm 2.2 2.2 2.2 <1.8 STRJ -WG4 Maximum metal current mA 2.16 1.56 1.2 0.6 STRJ -WG4 mm 1.08 0.78 0.60 0.30 mm 2.70 0.21 0.00 0.00 mm 10 10 10 10 mm 289 67 12 2 Technology node Voltage Metal height/width aspect 2011 Reference ITRS99 Table28 Signal Integrity DSM Category Crosstalk noise Required parallel interconnect maximum allowable length which considers parastic capacitence effect Required Estimated parallel interconnect maximum allowable length which considers parastic capacitence effect Estimated RC delay Required interconnect maximum allowable length which considers resistence Required Estimated interconnect maximum allowable length which considers resistence Estimated Inductance Interconnect Inductance Effect EMI Allowed Man ufac ture Reliability Estimated IR drop Required Estimated ElectroMigration OPE (*a) Next Page (*b) Next CP1 (*1) CP2 (*2) Allowable EMI by FCCclassB (at a distance of 3.0m ) uV/m 150 200 500 500 Estimated EMI by a chip (observation point =3.0m) uV/m 11 22 43 43 Required maximum allowable number of FF which is driven by power line without failure due to IR Drop. Estimated maximum allowable number of FF which is driven by power line without failure due to IR Drop. 20 20 20 20 34 21 10 5 Number of Power Pads (High Performance) 342 472 800 1,066 Number of Power Pads (Battery/Hand-Held) 6 9 16 16 Number of Power Pads (Target of LP-SWG) 2 2 3 4 CP CP Optical Proximity Correction See tab.2-1-4-2 Page See tab.2-1-4-3 (*c) Next Page (*d) Next See tab.2-1-4-4 Page See tab.2-1-4-5 See tab.2-1-4-6 CP1(1st Crisis Point): Interconnect effects becomes critical in high speed blocks(1GHz). CP2(2nd Crisis Point): Interconnect effects becomes major delay in high speed blocks(2GHz). February 9,2000 - 22 STRJ-WG1 DSM An overall DSM requirements table --- A supplementary explanation --- (*a) (*b) Derived from 3000 x ( wiring pitch ), and wiring pitch is assumed as 2X of Technology node. Namely, 1.08 mm is coming from 180nm x 2 x 3000. At least 3000 wiring pitch parallel interconnect is required. 10mm interconnect length is directly coming from that Die size remains 10mm Obviously, the longest interconnect probably reaches to 10mm under the above assumption. (*c) Source of these values is FCC classB standard( at a distance of 3.0m). (*d) Because estimated number of FFs in 2002 is 21, around 20 should be considered as required number of FFs at each Technology node era. February 9,2000 - 23 STRJ-WG1 DSM Crosstalk Noise (table 2-1-4-2) Parallel maximum length unit nm V MHz cm□ Technology node Voltage Frequency Die size Metal height/width aspect Interlevel metal insulator effective dielectric constant k Maximum parallel length μΩ-cm Metal effective resistivity Nominal Metal width nm Metal Thickness nm Resistance /Metal length Ω/mm Lumped Capacitance /Metal length fF/mm Coupled Capacitance /Metal length Output resistance in aggressor Output resistance in victim Maximum parallel length fF/mm Ω Ω mm 1999 180 1.5 150 1 2 2002 130 1.2 400 1 2.1 2.5~3.0 2005 100 0.9 1000 1 1.7 2.0~2.5 2011 50 0.6 2000 1 2.1 <1.5 2.2 360 720 85 51 2.2 260 546 155 30 2.2 200 340 324 28 1.8 100 210 857 22 58 1000 300 2.70 42 1300 390 0.21 45 1400 420 -0.33 40 1450 435 -0.26 Reference STRJ-WG1/LP-SWG STRJ-WG1/LP-SWG STRJ-WG4 STRJ-WG4 STRJ-WG4 STRJ-WG4 STRJ-WG4 STRJ-WG1/DSM-SWG STRJ-WG1/DSM-SWG *1 *1 STRJ-WG1/DSM-SWG *2 STRJ-WG1/DSM-SWG *2 STRJ-WG1/DSM-SWG *3 *1 The values are from Table2 in 『Challenges and Opportunities for Design Innovations in Nanometer Technologies』 J. Cong UCLA *2 The values are calculated on the model assuming that drivability of a victim net is 3 times as large as that of an aggressor net. *3 Maximum parallel length is calculated from eqation (3). February 9,2000 - 24 STRJ-WG1 Cc : Coupling capacitance between two lines Rline,a: Longitudinal resistance of a line in an aggressor net Rline,v: Longitudinal resistance of a line in a victim net DSM According to reference [1],[2], the peak noise voltage of the above model is shown below. - How the the maximal parallel length is calculated - Vdd Vnoise = -----------------------------------------Rout,a * Ci,a Ci,v ----------------------------- + ----(Rout,v + Rline,v / 2) * Cc Cc Reference [1] describes the following simplified model of coupled wires. | | === Ci,a | _ Rout,a Rline,a/2 | Rline,a/2 aggressor --( | )---VVVVVV--------VVVVVV------+-------VVVVVV-------------~ | | === Cc | | Rout,v Rline,v/2 | Rline,v/2 victim ------------VVVVVV--------VVVVVV------+-------VVVVVV-------------| | === Ci,v | | Rout,a : Output resistance of a driver in an aggressor net Rout,v : output resistance of a driver in a victim net Ci,a : Intrinsic capacitance of a line in an aggressor net Ci,v : Intrinsic capacitance of a line in a victim net Cc : Coupling capacitance between two lines Rline,a: Longitudinal resistance of a line in an aggressor net Rline,v: Longitudinal resistance of a line in a victim net To derive an upper limit of geometrical adjacent lengh not to exceed allowable peak noise Vdd/3, the model is further simplified as follows. Vnoise = Vdd/3 Ci,a = Ci,v = L * c Cc = L * cc Rline,a = Rline,v = L * r L : Geometrical adjacent length (victim and aggressor running in parallel) c : Intrinsic line capacitance per unit length cc: Coupling capacitance per unit length r : Longitudinal line resisitance per unit length R : Output resistance The above terms are substituted for equation (1). Vdd Vdd ------ = ----------------------------------------------3 Rout,a * L * c L*c -------------------------------- + ------(Rout,v + L * r / 2) * L * cc L * cc (2) An upper limit of geometrical adjacent length is calculated according to equation (2). 6 * Rout,v * cc - 2 * Rout,v * c - 2 * Rout,a * c L = --------------------------------------------------r * c - 3 * r * cc According to reference [1],[2], the peak noise voltage of the above model is shown below. Vdd Vnoise = -----------------------------------------Rout,a * Ci,a Ci,v ----------------------------- + ----(Rout,v + Rline,v / 2) * Cc Cc (1) (1) (3) [1] "Analysis, Reduction and Avoidance of Crosstalk on VLSI Chips", IBM International Symposium on Physical Design, 1998 [2] A.Vittal, M.Marek-Sadowska, University of California, Santa Barbara, "Reducing Coupled Noise During Routing", Proceedings, Fifth ACM SIGDA Phisical Design Workshop, 1996, pp.27-33 To derive an upper limit of geometrical adjacent lengh not to exceed allowable peak noise Vdd/3, the model is further simplified as follows. Vnoise = Vdd/3 Ci,a = Ci,v = L * c = L * cc - 25 FebruaryCc9,2000 Rline,a = Rline,v = L * r STRJ-WG1 DSM Interconnect Delay (table 2-1-4-3) Maximum length Technology node Frequency Metal height/width aspect Maximum wire length Cycle Time Allowable Time for RC delay Metal effective resistivity Nominal Metal Width Metal Thickness Resistance / Metal length Plate Capacitance per area Fringe Capacitance per length Plate Capacitance / Metal length FringeCapacitance / Metal length Total Capacitance / Metal length RC delay / Metal length Interconnect maximum allowable length which considers resistence unit nm MHz 1999 180 150 2 2002 130 400 2.1 2005 100 1000 1.7 2011 50 2000 2.1 ID 2500 1250 2.2 260 546 154.97 0.08 0.10 20.80 100.00 120.80 18.72 1000 500 2.2 200 340 323.53 0.06 0.12 12.00 120.00 132.00 42.71 500 250 1.8 100 210 857.14 0.04 0.15 4.00 150.00 154.00 132.00 E =1/B F = E x 0.5 nm nm Ω/mm fF/um2 fF/um fF/um fF/um fF/um ps/mm 6667 3333 2.2 360 720 84.88 0.10 0.10 36.00 100.00 136.00 11.54 mm 288.770 66.771 11.708 1.894 ps ps μΩ-cm Equation Reference A B STRJ-WG1/LP-SWG C STRJ-WG4 STRJ-WG1/DSM-SWG (*1) STRJ-WG4 G H =Ax2 I =HxC J =G/H/I STRJ-WG1/DSM-SWG (*2) K L STRJ-WG1/DSM-SWG (*3) M =KxH N =L O =M+N P =JxO Q =F/P (*1) Allowable RC delay is defined as the half time of cycle time (*2) Plate Capacitance per area are derived by the trend of process technology (*3) Fringe Capacitance per area are derived by the trend of process technology February 9,2000 - 26 STRJ-WG1 DSM Electro Magnetic Interference (table 2-1-4-4) EMI 1999 180 5 80 4 25 1.5 150 1 2 2.16 2.2 2002 130 20 50 10 100 1.2 400 1 2.1 1.56 2.2 2.5~3.0 2005 100 100 30 30 500 0.9 1000 1 1.7 1.2 2.2 2.0~2.5 2011 50 1000 10 100 5000 0.6 2000 1 2.1 0.6 <1.8 <1.5 Allowable EMI by FCC classB (at a distance of 3.0muV/m ) 150.0 200.0 500.0 500.0 Estimated EMI by a chip (at a distance of 3.0m ) 11.4 22.1 43.3 42.8 Technology node Size in gate count Logic gate count ratio Logic gate count Total Transistor count Voltage Frequency Die size Metal height/width aspect Maximum metal current Metal effective resistivity Interlevel metal insulator effective dielectric unit nm Mgates % Mgates Mtrs V MHz cm□ mA μΩ-cm k EMI February 9,2000 - 27 uV/m STRJ-WG1 DSM IR Drop (table 2-1-4-5) IR drop Technology node Nominal Ion [25c,NMOS,low power] Nominal Ion [25c,PMOS,low power] Voltage Metal height/width aspect unit nm uA/um uA/um V 1999 180 490 230 1.5 2 2002 130 490 230 1.2 2.1 2005 100 490 230 0.9 1.7 2011 50 490 230 0.6 2.1 ID 2.2 360 720 2.0 1.8 17.0 34.0 1.800 0.648 22.0 5 1.1 10.0 150 136 4 2.2 260 546 2.0 1.3 31.0 62.0 1.300 0.468 29.0 5 1.5 10.0 120 83 4 2.2 200 340 2.0 1.0 64.7 129.4 1.000 0.360 46.6 5 2.3 10.0 90 39 4 1.8 100 210 2.0 0.5 171.4 342.9 0.500 0.180 61.7 5 3.1 10.0 60 19 4 G H I J K L M N O P Q R S T U V 34 21 10 5 Equation A B C E F Reference ITRS99 Table28 ITRS99 Table28 STRJ-WG1/LP-SWG STRJ -WG4 Maximum number of F/Fs Metal effective resistivity Nominal Metal Width Metal Thickness Average Power Wire Length for each Trs Nominal Power Metal Width Resistance / Power Metal Length Average Power Wire resistance per Trs Typical Gate Width of Tr Average Current Consumption per Tr (mA) Average IR Drop per Trs Activation ratio Effective IR Drop perTtrs Maximum allowable IR drop ratio Maximum allowable IR Drop Maximum number of trs on each power line Average number of clock Trs in a FF Maximum allowable number of FF which is driven by power line without failure due to IR Drop February 9,2000 - 28 μΩ-cm nm nm mm um Ω/mm Ω um mA mV % mV % mV STRJ -WG4 =Ax2 =HxF STRJ-WG1/DSM-SWG = A x 10 =G/I/K =JxL = A * 10 = (B+C)/2*N =MxO STRJ-WG1/DSM-SWG STRJ-WG1/DSM-SWG STRJ-WG1/DSM-SWG =P*Q STRJ-WG1/DSM-SWG =ExS =T/R W =U/V STRJ-WG1 DSM IR Drop Assumed Conditions in table 2-1-4-5 H : Nominal Metal width is assumed as 2X of Technology node. J : Average power wire length from a pad to Trs. is assumed as 2mm. K : Nominal power wire width is assumed as 10X of Technology node. N : Typical gate width(W) is assumed as 10X of Technology node. Q : Overall average activation ratio is assumed as 5%. S : Maximum allowable IR drop ratio is defined as 10% of power supply voltage. V : Average number of clock Trs. driven by one FF is assumed as 4. February 9,2000 - 29 STRJ-WG1 DSM Electro Migration (Table 2-1-4-6) Electro Migration High Performance Battery Target of LP-SWG unit Technology Node nm Metal Material Metal Thickness/Width Aspect Jmax A/cm2 Wire Width from Pads to Core um Power W Power Supply Voltage V Chip Power Current A Nominal Metal Width nm Metal Thickness nm Number of Power Pads Power W Power Supply Voltage V Chip Power Current A Nominal Metal Width nm Metal Thickness nm Number of Power Pads Power W Power Supply Voltage V Chip Power Current A Nominal Metal Width nm Metal Thickness nm Number of Power Pads 1999 180 Al 2.0 5.8E+05 70.0 90 1.8 50.0 360 720 342 1.4 1.5 0.9 360 720 6 0.5 1.5 0.3 360 720 2 2002 130 Al 2.1 9.6E+05 70.0 130 1.5 86.7 260 546 472 2.0 1.2 1.7 260 546 9 0.5 1.2 0.4 260 546 2 2005 100 Cu 1.7 1.4E+06 70.0 160 1.2 133.3 200 340 800 2.4 0.9 2.7 200 340 16 0.5 0.9 0.6 200 340 3 2011 50 Cu 2.1 3.7E+06 70.0 174 0.6 290.0 100 210 1,066 2.2 0.5 4.4 100 210 16 0.5 0.5 1.0 100 210 4 ID A B C D E F G H I J E F G H I J H F G H I J Reference / Equation STRJ-WG1/DSM-SWG STRJ-WG4 STRJ-WG4 ITRS99 (Maximum Power, High-performance) ITRS99 (Minimum logic VDD - maximum) = E/F = A*2 = B*H = D/(C*D*I), (Number of pads for VDD and GND) ITRS99 (Maximum Power, Battery) ITRS99 (Minimum logic VDD - minimum) = E/F = A*2 = B*H = D/(C*D*I), (Number of pads for VDD and GND) STRJ-WG1/LP-SWG (Target) ITRS99 (Minimum logic VDD - minimum) = E/F = A*2 = B*H = D/(C*D*I), (Number of pads for VDD and GND) (*) To show the relative difficulty of electro migration problem, we estimated the number of pads needed for power supply at each technology node. February 9,2000 - 30 STRJ-WG1