嵌入式微處理機

Embedded Microprocessors

UBI

Time:Mon. 6, 7, 8 (EE 501)

Evaluation:

Lab Experiments

50%

Midterm (Operation) 25%

Final (Operation)

25%

Website:

http://ares.ee.nchu.edu.tw/Course.files/epr103

/

References:

MSP430 and RX210 user's guides

>> Contents

Outline

UBI

Introductory Overview

MSP430 Architecture

General purpose Input/Output

Device Systems and Operating Modes

Timers

Data Acquisition

Digital-to-Analogue Converter

Direct Memory Access (DMA)

Hardware Multiplier

Communications

>> Contents

MSP430 Teaching Materials

UBI

Introductory Overview

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

w.msp430.ubi.pt

Contents

UBI

MSP430 Integrated Development Environments (IDEs)

MSP430 Experimenter’s board

eZ430-F2013

MSP-EXP430F5438

Wireless expansion (Chipcon’s RF transceiver chip)

MSP-FET430 Flash Emulation Tool

How to read technical datasheets

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

4

MSP430 IDEs (1/2)

UBI

Main characteristics of the MSP430 Integrated

Development Environments (IDEs);

Available both from TI and third parties;

Special attention will be given to:

Code Composer Essentials v3;

IAR Embedded Workbench (EWB) IDE.

Using an IDE:

Basic functions;

Step by step project development;

• Structure and management (source files; compiling,

assembling and linking operations) of projects developed

both in C and/or Assembly language.

>> Contents

5

Copyright 2009 Texas Instruments

All Rights Reserved

MSP430 IDEs (2/2)

UBI

A range of software tools are available for the

generation of MSP430 source code:

Code Composer Essentials (TI)

IAR EWB - Kickstart ed. (IAR Systems);

CrossStudio (Rowley Associates);

MSPGCC (open-source comunity)...

SwiftX (Forth, Inc.);

HI-TECH (HI-TECH software);

ANSI C (ImageCraft);

Project-430 (Phyton, Inc.);

AQ430 (Quadravox);

…

>> Contents

6

Copyright 2009 Texas Instruments

All Rights Reserved

Code Composer Essentials v3 (1/2)

UBI

TI’s MSP430 IDE:

It is available as:

A free upgrade for existing v2 users;

Professional version ($499), the main features being:

• Unlimited code size;

• Can be ordered from the MSP430 web page;

• Supported by TI Software Support.

Evaluation Version (Free):

• 16 kB Limit on C/ASM code size;

• Download from MSP430 web page;

• Supported by TI Software Support.

>> Contents

7

Copyright 2009 Texas Instruments

All Rights Reserved

Code Composer Essentials v3 (2/2)

UBI

New features include:

Free 16 kB code-limited version;

Support for large memory model (Place data >64k);

Enhanced Compatibility with IAR C-code:

#pragma (ISR declarations), most intrinsics;

GDB Debugger replaced by TI proprietary debugger that

allows faster single stepping;

Hardware Multiplier libraries (16 bits and 32 bits);

CCE v2 project support (auto convert);

Breakpoints:

• EEM support via unified breakpoint manager;

• Use of Enhanced Emulation Module (EEM), with

predefined Use Cases;

• Unlimited Breakpoints.

>> Contents

8

Copyright 2009 Texas Instruments

All Rights Reserved

Starter kit: Experimenter’s board

UBI

Features:

MSP430F2013;

MSP430F5438;

Compatible with TI’s wireless

evaluation modules.

Combining 2 MCUs provides

nearly every MSP430 peripherals

available.

Needs a MSP-FET430 for development

>> Contents

9

Copyright 2009 Texas Instruments

All Rights Reserved

Starter kit: eZ430-F2013

UBI

All 14 input/output pins on the MSP430F2013 are

accessible on the MSP-EZ430D target board for easy

debugging and interfacing to peripherals;

One of these input/output pins is connected to an LED

for visual feedback;

Device features and integrated peripherals:

16-MIPS performance;

16-bit Sigma Delta ADC;

16-bit timer;

Watchdog timer;

Brownout detector;

USI module supporting SPI and I2C;

5 low power modes (0.5 μA standby).

>> Contents

10

Copyright 2009 Texas Instruments

All Rights Reserved

Starter kit: MSP-EXP430F5438 (1/5)

UBI

MSP-EXP430F5438:

MSP430F5438.

New features:

Power Management Module (PMM);

Unified Clock System (UCS);

System (SYS) modules;

Expanded memory/peripheral mapping

Peripheral module enhancements.

Enhanced performance

20 bit address capability;

32 bit Hardware Multiplier.

This board provides the wide range of F5438 peripherals.

>> Contents

11

Copyright 2009 Texas Instruments

All Rights Reserved

Starter kit: MSP-EXP430F5438 (2/5)

UBI

Device features and integrated peripherals

Device: MSP430F5438:

• 256 kB + 512 kB flash memory; 16 kB RAM.

>> Contents

Integrated peripherals:

• Three 16-bit timers;

• 12-bit SAR Analogue-to-Digital Converter;

• Direct Memory Access (DMA);

• Hardware multiplier (supporting 32-Bit operations);

• Universal Serial Communication Interfaces (USCI):

Enhanced UART Supporting Auto-Baudrate; IrDA

Encoder and Decoder; Synchronous SPI; I2C™;

• Real time clock module with alarm capabilities;

• Temperature sensor;

• Up to 87 I/O pins.

12

Copyright 2009 Texas Instruments

All Rights Reserved

Starter kit: MSP-EXP430F5438 (3/5)

UBI

The MSP430F5438 supports I2C and SPI protocols using

the USCI and the USI peripherals;

This protocol is used for inter-processor communication;

The link can be disconnected in hardware allowing these

peripherals to be used for other communication purposes.

Programming and Debugging:

Can be programmed using any MSP430 Flash Emulation

Tool (MSP-FET430xIF);

Wireless expansion:

Compatible with TI Wireless CCxxxXEMK Evaluation

Modules, such as the CC2500EMK.

Compatible with TI eZ-RF2500.

>> Contents

13

Copyright 2009 Texas Instruments

All Rights Reserved

Starter kit: MSP-EXP430F5438 (4/5)

UBI

The demo board has various system clock options that

support low and high frequencies.

The MSP430F5438 has integrated an Unified Clock

System that provides different clock sources:

Three low-frequency sources:

• LFXT1;

• Internal Very Low Power/Low Frequency Oscillator (VLO);

• Internal Reference Oscillator (REFO).

Internal Digitally Controlled Oscillator (DCO) / Frequency

Locked Loop (FLL) for highspeed operation:

• FLL reference selectable from LFXT1, REFO, or XT2.

ACLK/SMCLK/MCLK can all be driven from any source;

Dedicated MODOSC (internal) used for modules like Flash

controller, ADC, among others.

>> Contents

14

Copyright 2009 Texas Instruments

All Rights Reserved

Starter kit: MSP-EXP430F5438 (5/5)

UBI

MSP-EXP430F5438 demo board jumper and connectors

locations:

>> Contents

15

Copyright 2009 Texas Instruments

All Rights Reserved

Wireless expansion (Chipcon’s RF

transceiver chip)

UBI

CC2500EMK Evaluation Module 2.4 GHz:

The CC2500EM evaluation modules are provided with

antennas;

These evaluation modules are add-on daughter boards that

require a CC2500 development kit for evaluation and

development;

It allows to do range testing (PER testing) and transfer data

from one PC to another using the SmartRF®04DK, in order to

evaluate how well the SmartRF®04 products fit the intended

application;

It allows performing RF measurements.

>> Contents

16

Copyright 2009 Texas Instruments

All Rights Reserved

MSP-FET430 Flash Emulation Tool (1/2)

UBI

The flash emulation tool (FET) allow the application

development on the MSP430 MCU;

There are available two debugging interfaces:

USB port: MSP-FET430UIF;

Parallel port: MSP-FET430PIF.

MSP-FET430UIF flash emulation tool:

>> Contents

17

Copyright 2009 Texas Instruments

All Rights Reserved

MSP-FET430 Flash Emulation Tool (2/2)

UBI

Are used to program and debug the MSP430 in-system

through the:

4-wire JTAG interface: MSP-FET430PIF and MSP-FET430UIF;

2-wire JTAG interface (Spy Bi-Wire): MSP-FET430UIF.

These debugging tools interface the previously presented

MSP430 hardware development tools to the included

integrated software environment (CCE or IAR) and

include code to start an application.

Both MSP-FET430 supports development with all MSP430

flash devices.

>> Contents

18

Copyright 2009 Texas Instruments

All Rights Reserved

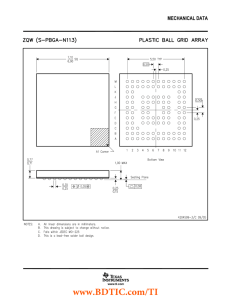

How to Read Datasheets (1/6)

UBI

Manufacturers of electronic components provide

datasheets containing the specifications detailing the

part/device characteristics;

Datasheets give the electrical characteristics of the

device and the pin-out functions, but without detailing

the internal operation;

More complex devices are provided with documents that

aid the development of applications, such as:

Application notes;

User's guides;

Designer's guides;

Package drawings, etc…

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

19

How to Read Datasheets (2/6)

UBI

Datasheets include information:

Concerning the part number of the device or device series;

Electrical characteristics:

• Maximum and minimum operating voltages;

• Operating temperature range e.g. 0 to 70 degrees C;

• Output drive capacity for each output pin, as well as an

overall limit for the entire chip;

• Clock frequencies;

• Pin out electrical characteristics (capacitance, inductance,

resistance);

• Noise tolerance or the noise generated by the device

itself;

• Physical tolerances…

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

20

How to Read Datasheets (3/6)

UBI

MSP430 device datasheet:

Device has a large number of peripherals;

Each input/output pin usually has more than one function;

It has a table with the description of each pin function;

Example, Pin number 2 = P6.3/A3;

• Digital Input/Output Port 6 bit 3;

• 3rd analogue input.

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

21

How to Read Datasheets (4/6)

UBI

MSP430 User’s Guide:

Most peripherals are represented by Block Diagrams.

Example: Part of the MSP430F44x clock module block

diagram:

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

22

How to Read Datasheets (5/6)

UBI

MSP430 User’s Guide:

Example: Part of the MSP430F44x clock module block diagram:

Detail SELMx;

Multiplexed block: (4 inputs and 1 output):

• SELMx = 00: Output routed to the 1st multiplexer output;

• SELMx = 01: Output routed to the second one and so on;

• SELMx is a 2-bit mnemonic: SELM1 (MSB), SELM0 (LSB).

To use the peripheral, it is necessary to find out how the

register(s) need to be configured:

• SELMx is in the FLL_CTL1 register.

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

23

How to Read Datasheets (6/6)

UBI

MSP430 User’s Guide:

SELMx are the 3rd and 4th bits of FLL_CTL1 control register.

FLL_CTL1, FLL+ control register 1

7

6

5

-

SMCLKOFF

XT2OFF

Bit

4

3

2

SELMx

SELS

1

0

FLL_DIVx

Description

6

SMCLKOFF

Disable the submain clock signal (SMCLK):

SMCLKOFF = 0

SMCLKOFF = 1

SMCLK active

SMCLK inactive

5

XT2OFF

Disable the second crystal oscillator (XT2):

XT2OFF = 0

XT2OFF = 1

XT2 active

XT2 inactive

4-3

SELMx

Select the master clock (MCLK) source:

SELM1 SELM0 = 0 0

SELM1 SELM0 = 0 1

SELM1 SELM0 = 1 0

SELM1 SELM0 = 1 1

2

SELS

Select the submain clock (SMCLK) source:

SELS = 0

DCO

SELS = 1

XT2

1-0

FLL_DIVx

Select the auxiliary clock (ACLK) signal divider:

FLL_DIV_0 = 0 0

Divider

FLL_DIV_1 = 0 1

Divider

FLL_DIV_2 = 1 0

Divider

FLL_DIV_3 = 1 1

Divider

>> Contents

DCO

DCO

XT2

LFXT1

factor:

factor:

factor:

factor:

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

/1

/2

/4

/8

24

Good software practices for low power

consumption (1/2)

UBI

C coding tips:

Use local variable as much as possible (Local variables use

CPU registers whereas global variables use RAM);

Use unsigned data types where possible;

Use pointers to access structures and unions;

Use “static const” class to avoid run-time copying of

structures, unions, and arrays;

Avoid modulo;

Count down “for” loops.

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

25

Good software practices for low power

consumption (2/2)

UBI

Principles for low power applications:

Maximize the time in standby;

Use interrupts to control program flow;

Replace software functions with peripheral hardware;

Manage the power of internal peripherals;

Manage the power of external devices;

Device choice can make a difference;

Effective code is a must. Every unnecessary instruction

executed is a portion of the battery wasted that will never

return.

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

26

MSP430 Teaching Materials

UBI

MSP430 Architecture

Texas Instruments Incorporated

University of Beira Interior (PT)

Pedro Dinis Gaspar, António Espírito Santo, Bruno Ribeiro, Humberto Santos

University of Beira Interior, Electromechanical Engineering Department

www.msp430.ubi.pt

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

Contents

UBI

MSP430 architecture:

Main characteristics

Architecture topology

Address space

Interrupt vector table

Central Processing Unit (MSP430 CPU)

Central Processing Unit (MSP430X CPU)

Addressing modes

Instructions set

>> Contents

28

Copyright 2009 Texas Instruments

All Rights Reserved

Introduction

UBI

A comprehensive description of the MSP430 architecture,

covering its:

Main characteristics;

Device architecture;

Address space;

Interrupt vector table;

Central Processing Unit (MSP430 CPU and MSP430X CPU);

7 seven addressing modes and instruction set composed of:

• 27 base opcodes;

• 24 emulated instructions.

>> Contents

29

Copyright 2009 Texas Instruments

All Rights Reserved

Microcontroller characteristics

UBI

Integration: Able to implement a whole design onto a single

chip.

Cost: Are usually low-cost devices (a few $ each);

Clock frequency: Compared with other devices

(microprocessors and DSPs), MCUs use a low clock frequency:

MCUs today run up to 100 MHz/100 MIPS (Million

Instructions Per Second).

Power consumption: Low power (battery operation);

Bits: 4 bits (older devices) to 32 bits devices;

Memory: Limited available memory, usually less than 1 MByte;

Input/Output (I/O): Low to high (8 to 150) pin-out count.

>> Contents

30

Copyright 2009 Texas Instruments

All Rights Reserved

MSP430 main characteristics (1/3)

UBI

Low power consumption:

0.1 A for RAM data retention;

0.8 A for real-time clock mode operation;

250 A/MIPS during active operation.

Low operation voltage (from 1.8 V to 3.6 V);

< 1 s clock start-up;

< 50 nA port leakage;

Zero-power Brown-Out Reset (BOR).

>> Contents

31

Copyright 2009 Texas Instruments

All Rights Reserved

MSP430 main characteristics (2/3)

UBI

On-chip analogue features:

10/12/16-bit Analogue-to-Digital Converter (ADC);

12-bit dual Digital-to-Analogue Converter (DAC);

Comparator-gated timers;

Operational Amplifiers (Op Amps);

Supply Voltage Supervisor (SVS).

16 bit RISC CPU:

Compact core design reduces power consumption and cost;

16-bit data bus;

27 core instructions;

7 addressing modes;

Extensive vectored-interrupt capability.

>> Contents

32

Copyright 2009 Texas Instruments

All Rights Reserved

MSP430 main characteristics (3/3)

UBI

Flexibility:

Up to 256 kByte Flash;

Up to 100 pins;

USART, I2C, Timers;

LCD driver;

Embedded emulation;

And many more peripherals modules…

Microcontroller performance:

Instruction processing on either bits, bytes or words

Reduced instructions set;

Compiler efficient;

Wide range of peripherals;

Flexible clock system.

>> Contents

33

Copyright 2009 Texas Instruments

All Rights Reserved

MSP430 Architecture

UBI

Block diagram:

>> Contents

34

Copyright 2009 Texas Instruments

All Rights Reserved

Address Space

UBI

Mapped into a single, contiguous address space:

Flash/ROM: All code, tables, and hard-coded constants

reside in this memory space.

Information memory: Variables needed for the next

power up can be stored here during power down. It can also

be used as code memory.

Boot memory: The bootstrap loader performs some of the

same functions as the JTAG interface.

RAM: RAM is used for both code and data.

Peripheral Modules: Peripheral modules consist of all onchip peripheral registers that are mapped into the address

space.

Special Function Registers (SFRs): Some peripheral

functions are mapped into memory with special dedicated

functions.

>> Contents

35

Copyright 2009 Texas Instruments

All Rights Reserved

Memory Map

UBI

Memory Address

End:

0FFFFh

Start:

0FFE0h

End:

0FFDFh

Description

Interrupt Vector Table

Flash/ROM

Start *:

End *:

Start:

End:

Start:

End *:

Start:

End:

Start:

End:

Start:

End:

Start:

>> Contents

0F800h

01100h

010FFh

0107Fh

01000h

0FFFh

0C00h

09FFh

027Fh

0200h

01FFh

0100h

00FFh

0010h

000Fh

0000h

Access

Word/Byte

Word/Byte

Information Memory

(Flash devices only)

Boot Memory

(Flash devices only)

Word/Byte

RAM

Word/Byte

Word/Byte

16-bit Peripheral modules

Word

8-bit Peripheral modules

Byte

Special Function Registers

Byte

36

Copyright 2009 Texas Instruments

All Rights Reserved

Interrupt vector table

UBI

Mapped at the very end of memory space (upper 16

words of Flash/ROM): 0FFE0h - 0FFFEh (4xx devices);

Priority of the interrupt vector increases with the word

address.

>> Contents

37

Copyright 2009 Texas Instruments

All Rights Reserved

Central Processing Unit (MSP430 CPU) (1/7)

UBI

RISC (Reduced Instructions Set Computing) architecture:

Instructions are reduced to the basic ones (short set):

• 27 physical instructions;

• 24 emulated instructions.

This provides simpler and faster instruction decoding;

Interconnect by using a common memory address bus

(MAB) and memory data bus (MDB) - Von Neumann

architecture:

• Makes use of only one storage structure for data and

instructions sets.

• The separation of the storage processing unit is implicit;

• Instructions are treated as data (programmable).

>> Contents

38

Copyright 2009 Texas Instruments

All Rights Reserved

Central Processing Unit (MSP430 CPU) (2/7)

UBI

RISC (Reduced Instructions Set Computing) type

architecture:

Uses a 3-stage instruction pipeline containing:

• Instruction decoding;

• 16 bit ALU;

• 4 dedicated-use registers;

• 12 working registers.

Address bus has 16 bit so it can address 64 kB (including

RAM + Flash + Registers);

Arithmetic Logic Unit (ALU):

Addition, subtraction, comparison and logical (AND, OR,

XOR) operations;

Operations can affect the overflow, zero, negative, and carry

flags of the SR (Status Register).

>> Contents

39

Copyright 2009 Texas Instruments

All Rights Reserved

Central Processing Unit (MSP430 CPU) (3/7)

UBI

Incorporates sixteen 16-bit registers:

• 4 registers (R0, R1, R2 and R3) have dedicated functions;

• 12 register are working registers (R4 to R15) for general

use.

R0: Program Counter (PC):

Points to the next instruction to be read from memory and

executed by the CPU.

R1: Stack Pointer (SP):

1st: stack can be used by user to store data for later use

(instructions: store by PUSH, retrieve by POP);

2nd: stack can be used by user or by compiler for subroutine

parameters (PUSH, POP in calling routine; addressed via offset

calculation on stack pointer (SP) in called subroutine);

>> Contents

40

Copyright 2009 Texas Instruments

All Rights Reserved

Central Processing Unit (MSP430 CPU) (4/7)

UBI

R1: Stack Pointer (SP) (continued):

3rd: used by subroutine calls to store the program counter

value for return at subroutine's end (RET);

4th: used by interrupt - system stores the actual PC value

first, then the actual status register content (on top of stack)

on return from interrupt (RETI) the system get the same

status as just before the interrupt happened (as long as none

has changed the value on TOS) and the same program

counter value from stack.

>> Contents

41

Copyright 2009 Texas Instruments

All Rights Reserved

Central Processing Unit (MSP430 CPU) (5/7)

UBI

R2: Status Register (SR):

Stores status and control bits;

System flags are changed automatically by the CPU;

Reserved bits are used to support the constant generator.

15

14

13

12

11

10

9

8

Reserved for CG1

Bit

7

V

6

SCG1

SCG0

5

OSCOFF

4

3

CPUOFF

GIE

2

N

1

Z

0

C

Description

8

V

Overflow bit. V = 1 Result of an arithmetic operation overflows the signed-variable range.

7

SCG1

System clock generator 0. SCG1 = 1

DCO generator is turned off – if not used for MCLK or SMCLK

6

SCG0

System clock generator 1. SCG0 = 1

FLL+ loop control is turned off

5

OSCOFF

Oscillator Off. OSCOFF = 1

4

CPUOFF

CPU off. CPUOFF = 1

3

GIE

General interrupt enable. GIE = 1

2

N

Negative flag. N = 1

1

Z

Zero flag. Z = 1

result of a byte or word operation is 0.

0

C

Carry flag. C = 1

>> Contents

turns off LFXT1 when it is not used for MCLK or SMCLK

disable CPU core.

enables maskable interrupts.

result of a byte or word operation is negative.

result of a byte or word operation produced a carry.

42

Copyright 2009 Texas Instruments

All Rights Reserved

Central Processing Unit (MSP430 CPU) (6/7)

UBI

R2/R3: Constant Generator Registers (CG1/CG2):

Depending of the source-register addressing modes (As)

value, six constants can be generated without code word or

code memory access to retrieve them.

This is a very powerful feature which allows the

implementation of emulated instructions, for example,

instead of implement a core instruction for an increment the

constant generator is used.

Register

As

Constant

Remarks

R2

00

-

Register mode

R2

(0)

R2

01

10

00004h

Absolute mode

+4, bit processing

R2

11

00008h

+8, bit processing

R3

00000h

R3

R3

00

01

10

00001h

00002h

0, word processing

+1

+2, bit processing

R3

11

0FFFFh

-1, word processing

>> Contents

Copyright 2008 43

Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

43

Copyright 2009 Texas Instruments

All Rights Reserved

Central Processing Unit (MSP430 CPU) (7/7)

UBI

R4 - R15: General–Purpose Registers:

These general-purpose registers are adequate to store data

registers, address pointers, or index values and can be

accessed with byte or word instructions.

>> Contents

Copyright 2008 44

Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

44

Copyright 2009 Texas Instruments

All Rights Reserved

UBI

Central Processing Unit (MSP430X CPU)

(1/10)

Main features of the MSP430X CPU architecture:

The MSP430X CPU extends the addressing capabilities of the

MSP430 family beyond 64 kB to 1 MB;

To achieve this, some changes have been made to the

addressing modes and two new types of instructions have

been added;

One instruction type allows access to the entire address

space, and the other is designed for address calculations;

The MSP430X CPU address bus has 20 bits, although the

data bus still has 16 bits. Memory accesses to 8-bit, 16-bit

and 20-bit data are supported;

Despite these changes, the MSP430X CPU remains

compatible with the MSP430 CPU, having a similar number

of registers.

>> Contents

45

Copyright 2009 Texas Instruments

All Rights Reserved

UBI

Central Processing Unit (MSP430X CPU)

(2/10)

Organization of the MSP430X CPU:

Although the MSP430X CPU structure is

similar to that of the MSP430 CPU, there

are some differences that will now be

highlighted;

With the exception of the status register

SR, all MSP430X registers are 20 bits;

The CPU can now process 20-bit or 16bit data.

>> Contents

46

Copyright 2009 Texas Instruments

All Rights Reserved

UBI

Central Processing Unit (MSP430X CPU)

(3/10)

The MSP430X CPU has 16 registers, some of which have

special use:

R0 (PC) Program Counter:

Has the same function as the MSP430 CPU, although now it

has 20 bits.

R1 (SP) Stack Pointer:

Has the same function as the MSP430 CPU, although now it

has 20 bits.

R2 (SR) Status Register:

Has the same function as the MSP430 CPU, but it still has 16

bits.

>> Contents

47

Copyright 2009 Texas Instruments

All Rights Reserved

UBI

Central Processing Unit (MSP430X CPU)

(4/10)

R2 (SR) Status Register:

Description of the SR bits:

>> Contents

48

Copyright 2009 Texas Instruments

All Rights Reserved

UBI

Central Processing Unit (MSP430X CPU)

(5/10)

R2 (SR/CG1) and R3 (CG2) Constant Generators:

Registers R2 and R3 can be used to generate six different

constants commonly used in programming, without adding

an additional 16-bit word to the instruction;

The constants are fixed and are selected by the (As) bits of

the instruction. (As) selects the addressing mode.

Values of constants

generated:

>> Contents

49

Copyright 2009 Texas Instruments

All Rights Reserved

UBI

Central Processing Unit (MSP430X CPU)

(6/10)

R2 (SR/CG1) and R3 (CG2) Constant Generators:

Whenever the operand is one of the six constants, the

registers are selected automatically;

Therefore, when used in constant mode, registers R2 and R3

cannot be used as source registers.

R4-R15 – General-purpose registers:

Have the same function as in the MSP430 CPU, although

they now have 20 bits;

These registers can process 8-bit, 16-bit or 20-bit data;

If a byte is written to one of these registers it takes bits 7:0,

the bits 19:8 are filled with zeroes. If a word is written to

one of these registers it takes bits 15:0, the bits 19:16 are

filled with zeroes.

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

50

UBI

Central Processing Unit (MSP430X CPU)

(7/10)

R4-R15 – General-purpose registers:

Handling byte data (8 bits) using the suffix .B:

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

51

UBI

Central Processing Unit (MSP430X CPU)

(8/10)

R4-R15 – General-purpose registers:

Handling word data (16 bits) using the suffix .W:

>> Contents

52

Copyright 2009 Texas Instruments

All Rights Reserved

UBI

Central Processing Unit (MSP430X CPU)

(9/10)

R4-R15 – General-purpose registers:

Manipulation of a 20-bit address using the suffix .A:

>> Contents

53

Copyright 2009 Texas Instruments

All Rights Reserved

Addressing modes

UBI

7 addressing modes for the source operand:

4 addressing modes for the destination operand:

Register mode; Indexed mode; Symbolic mode; Absolute

mode.

For the destination operand, two additional addressing

modes can be emulated.

>> Contents

54

Copyright 2009 Texas Instruments

All Rights Reserved

Instruction set

UBI

27 core instructions;

24 emulated instructions;

The instruction set is orthogonal;

The core instructions have unique opcodes decoded by

the CPU, while the emulated ones need assemblers and

compilers for their mnemonics;

There are three core-instruction formats:

Double operand;

Single operand;

Program flow control - Jump.

>> Contents

55

Copyright 2009 Texas Instruments

All Rights Reserved

MSP430 Teaching Materials

UBI

General Purpose Input/Output

Texas Instruments Incorporated

University of Beira Interior (PT)

Pedro Dinis Gaspar, António Espírito Santo, Bruno Ribeiro, Humberto Santos

University of Beira Interior, Electromechanical Engineering Department

www.msp430.ubi.pt

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

Contents

UBI

I/O Introduction

I/O port registers

Interruptible ports

>> Contents

57

Copyright 2009 Texas Instruments

All Rights Reserved

I/O Introduction (1/3)

UBI

Up to ten 8-bit digital Input/Output (I/O) ports, P1 to P10

(depending on the MSP430 device);

I/O ports P1 and P2 have interrupt capability;

Each interrupt for these I/O lines can be individually

configured:

To provide an interrupt on a rising or falling edge;

All interruptible I/O lines source a single interrupt vector.

The available digital I/O pins for the hardware

development tools:

eZ430-F2013: 10 pins - Port P1 (8 bits) and Port P2 (2 bits);

eZ430-RF2500: 32 pins - Port P1 to P4 (8 bits);

Experimenter’s board: 80 pins – Port P1 to P10 (8 bits).

>> Contents

58

Copyright 2009 Texas Instruments

All Rights Reserved

I/O Introduction (2/3)

UBI

Each I/O port can be:

Programmed independently for each bit;

Combine input, output, and interrupt functionality;

Edge-selectable input interrupt capability for all 8 bits of

ports P1 and P2;

Read/write access to port-control registers is supported by

all two- or one-address instructions;

Individually programmable pull-up/pull-down resistor (2xx

family only).

>> Contents

59

Copyright 2009 Texas Instruments

All Rights Reserved

I/O Introduction (3/3)

UBI

The port pins can be individually configured as I/O for

special functions, such as:

USART – Universal Synchronous/Asynchronous

Receive/Transmit for serial data;

Input comparator for analogue signals;

Analogue-to-Digital converter;

Others functions (see specific datasheet for details).

>> Contents

60

Copyright 2009 Texas Instruments

All Rights Reserved

Registers (1/6)

UBI

Independent of the I/O port type (non-interruptible or

interruptible), the operation of the ports is configured

by user software, as defined by the following registers:

Direction Registers (PxDIR):

• Read/write 8-bit registers;

• Select the direction of the corresponding I/O pin,

regardless of the selected function of the pin (general

purpose I/O or as a special function I/O);

• For other module functions, must be set as required by

the other function.

• PxDIR configuration:

Bit = 1: the individual port pin is set as an output;

Bit = 0: the individual port pin is set as an input.

>> Contents

61

Copyright 2009 Texas Instruments

All Rights Reserved

Registers (2/6)

UBI

Input Registers (PxIN):

• When pins are configured as GPIO, each bit of these

read-only registers reflects the input signal at the

corresponding I/O pin;

• PxIN configuration:

Bit = 1: The input is high;

Bit = 0: The input is low;

• Tip: Avoid writing to these read-only registers because

it will result in increased current consumption.

>> Contents

62

Copyright 2009 Texas Instruments

All Rights Reserved

Registers (3/6)

UBI

Output Registers (PxOUT):

• Each bit of these registers reflects the value written to

the corresponding output pin.

• PxOUT configuration:

Bit = 1: The output is high;

Bit = 0: The output is low.

– Note: the PxOUT Register is read-write. This means

that the previous value written to it can be read

back and modified to generate the next output

signal.

>> Contents

63

Copyright 2009 Texas Instruments

All Rights Reserved

Registers (4/6)

UBI

Pull-up/down Resistor Enable Registers (PxREN):

• Only available for the 2xx family;

• Each bit of this register enables or disables the pullup/pull-down resistor of the corresponding I/O pin.

• PxREN configuration:

– Bit = 1: Pull-up/pull-down resistor enabled;

– Bit = 0: Pull-up/pull-down resistor disabled.

– When pull-up/pull-down resistor is enabled:

– In this case Output Registers (PxOUT) select:

» Bit = 1: The pin is pulled up;

» Bit = 0: The pin is pulled down.

>> Contents

64

Copyright 2009 Texas Instruments

All Rights Reserved

Registers (5/6)

UBI

Function Select Registers: (PxSEL) and (PxSEL2):

• Some port pins are multiplexed with other peripheral

module functions (see the device-specific datasheet);

• These bits: PxSEL and PxSEL2 (see specific device

datasheet), are used to select the pin function:

– I/O general purpose port;

– Peripheral module function.

• PxSEL configuration:

Bit = 0: I/O Function is selected for the pin;

Bit = 1: Peripheral module function enabled for pin.

>> Contents

65

Copyright 2009 Texas Instruments

All Rights Reserved

Registers (6/6)

UBI

Function Select Registers: (PxSEL) and (PxSEL2):

• The 2xx family of devices provide the PxSEL2 bit to

configure additional features of the device;

• The PxSEL and PxSEL2 bits in combination provide the

following configuration:

– Bit = 0: I/O function is selected for the pin;

– Bit = 1: Peripheral module function is selected for

the pin.

PxSEL

PxSEL2

Pin Function

0

0

Selects general purpose I/O function

0

1

Selects the primary peripheral module function

1

0

Reserved (See device-specific data sheet)

1

1

Selects the secondary peripheral module function

Note: P1 and P2 configured as peripheral module function (PxSEL = 1 and/or PxSEL2) -> interrupts disabled.

>> Contents

66

Copyright 2009 Texas Instruments

All Rights Reserved

Interruptible ports (P1 and P2)

(1/2)

UBI

Each pin of ports P1 and P2 is able to make an interrupt

request;

Pins are configured with additional registers:

Interrupt Enable (PxIE):

• Read-write register to enable interrupts on individual pins;

• PxIE configuration:

Bit = 1: The interrupt is enabled;

Bit = 0: The interrupt is disabled.

• Each PxIE bit enables the interrupt request associated with

the corresponding PxIFG interrupt flag;

• Writing to PxOUT and/or PxDIR can result in setting PxIFG.

>> Contents

67

Copyright 2009 Texas Instruments

All Rights Reserved

Interruptible ports (P1 and P2)

(2/2)

UBI

Interrupt Edge Select Registers (PxIES):

• Selects the transition on which an interrupt occurs (if PxIE

and GIE are set);

• PxIES configuration:

Bit = 1: Interrupt flag is set on a high-to-low transition;

Bit = 0: Interrupt flag is set on a low-to-high transition.

Interrupt Flag Registers (PxIFG)

• Set automatically when an the programmed signal

transition (edge) occurs;

• PxIFG flag can be set and must be reset by software.

• PxIFG configuration:

Bit = 0: No interrupt is pending;

Bit = 1: An interrupt is pending.

>> Contents

68

Copyright 2009 Texas Instruments

All Rights Reserved