Chapter 06 - MSP430 Micro

advertisement

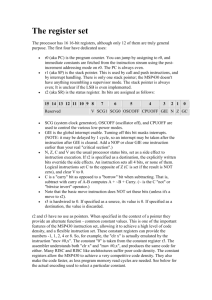

Chapter 6 – MSP430 Micro-Architecture Concepts to Learn… Computer Architecture MSP430 Micro-Architecture Instruction Cycle Review Fetch Cycle Addressing Modes Operand Fetch Cycles Execute Cycle Store Cycle Instruction Clock Cycles Digital I/O BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 2 Levels of Transformation Problems Algorithms Language (Program) Programmable Machine (ISA) Architecture Computer Specific Microarchitecture Manufacturer Specific Circuits Devices BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 3 Computer Architecture Computer Architecture Client’s requirements: function, cost, . . . Client’s taste: mood, style, . . . Goals Interface Architect Means Construction tec hnology: material, codes, . . . Engineering Arts The world of arts: aesthetics, trends, . . . Interface Like a building architect, whose place at the engineering/arts and goals/means interfaces is seen in this diagram, a computer architect reconciles many conflicting or competing demands. BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 4 MSP430 Micro-Architecture MSP430 Modular Architecture BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 5 MSP430 Micro-Architecture Memory Organization BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 6 MSP430 Micro-Architecture Micro-Architecture Simulator Program Counter Memory Address Register Address Bus Source Operand Instruction Register Destination Operand Port 1 Output Arithmetic Logic Unit BYU CS/ECEn 124 Condition Codes Memory Chapter 6 - MSP430 Micro-Architecture Data Bus 7 Quiz… Disassemble the following MSP430 instructions: Address 0x8010: 0x8012: 0x8014: 0x8016: 0x8018: 0x801a: 0x801c: 0x801e: 0x8020: 0x8022: 0x8024: 0x8026: 0x8028: 0x802a: 0x802c: 0x802e: BYU CS/ECEn 124 Data 4031 0600 40B2 5A1E 0120 430E 535E F07E 000F 1230 000E 8391 0000 23FD 413F 3FF6 Chapter 6 - MSP430 Micro-Architecture 8 Quiz… Disassemble the following MSP430 instructions: Address 0x8010: 0x8012: 0x8014: 0x8016: 0x8018: 0x801a: 0x801c: 0x801e: 0x8020: 0x8022: 0x8024: 0x8026: 0x8028: 0x802a: 0x802c: 0x802e: BYU CS/ECEn 124 Data 4031 0600 40B2 5A1E 0120 430E 535E F07E 000F 1230 000E 8391 0000 23FD 413F 3FF6 mov.w #0x0600,r1 mov.w #0x5a1e,&0x0120 mov.w #0,r14 add.b #1,r14 and.b #0x0f,r14 push #0x000e sub.w #0,0(r1) jne 0x8026 mov.w @r1+,r15 jmp 0x801c Chapter 6 - MSP430 Micro-Architecture 9 Instruction Cycle The Instruction Cycle INSTRUCTION FETCH DECODE Load destination operand EXECUTE Load source operand DESTINATION OPERAND FETCH Examine the instruction, and determine how to execute it SOURCE OPERAND FETCH Obtain the next instruction from memory Not all instructions require all six phases Carry out the execution of the instruction STORE RESULT Store the result in the designated destination BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 10 Fetch Cycle Fetching an Instruction PC BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 11 Addressing Modes Addressing Modes BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 12 Addressing Modes Source Addressing Modes The MSP430 has four basic modes for the source address: Rs - Register x(Rs) - Indexed Register @Rs - Register Indirect @Rs+ - Indirect Auto-increment In combination with registers R0-R3, three additional source addressing modes are available: label - PC Relative, x(PC) &label – Absolute, x(SR) #n – Immediate, @PC+ BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 13 Addressing Modes MSP430 Source Constants To improve code efficiency, the MSP430 "hardwires" six register/addressing mode combinations to commonly used source values: #0 - R3 in register mode #1 - R3 in indexed mode #4 - R2 in indirect mode #2 - R3 in indirect mode #8 - R2 in indirect auto-increment mode #-1 - R3 in indirect auto-increment mode Eliminates the need to use a memory location for the immediate value - commonly reduces code size by 30%. BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 14 Addressing Modes Destination Addressing Modes There are two basic modes for the destination address: Rd - Register x(Rd) - Indexed Register In combination with registers R0/R2, two additional destination addressing modes are available: label - PC Relative, x(PC) &label – Absolute, x(SR) BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 15 Operand Fetch Cycles Register Addressing Mode BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 16 Operand Fetch Cycles Source: Register Mode – Rs Rs BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 17 Operand Fetch Cycles Destination: Register Mode – Rd Rs BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 18 Operand Fetch Cycles Register-Indexed Addressing Mode BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 19 Operand Fetch Cycles Source: Indexed Mode – x(Rs) PC PC Rs BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 20 Operand Fetch Cycles Symbolic Addressing Mode BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 21 Operand Fetch Cycles Source: Symbolic Mode – Address PC PC PC BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 22 Operand Fetch Cycles Absolute Addressing Mode BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 23 Operand Fetch Cycles Source: Absolute Mode – &Address PC PC SR (0) BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 24 Operand Fetch Cycles Register Indirect Addressing Mode BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 25 Operand Fetch Cycles Source: Indirect Mode – @Rs Rs BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 26 Operand Fetch Cycles Register Indirect Auto-increment BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 27 Operand Fetch Cycles Source: Indirect Auto Mode – @Rs+ Rs Rs BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 28 Operand Fetch Cycles Immediate Addressing Mode BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 29 Operand Fetch Cycles Source: Immediate Mode – #n PC BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 30 Execute Cycle Execute Phase: PUSH.W SP SP BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 31 Execute Cycle Execute Phase: Jump BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 32 Store Cycle Store Phase: Rd BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 33 Store Cycle Store Phase: Other… BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 34 Instruction Clock Cycles Instruction Timing Instruction cycles = Power consumption Most instruction cycles limited by access to memory (von Neumann bottleneck) In general 1 cycle to fetch instruction +1 cycle for @Rn, @Rn+, or immediate +2 cycles for indexed, absolute, or symbolic +1 to write destination back to memory 2 cycles for any jump No difference between byte and word BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 35 Digital I/O Digital I/O Digital I/O grouped in 8 bit memory locations called ports Each I/O port can be: programmed independently for each bit combined for input, output, and interrupt functionality Edge-selectable input interrupt capability for all 8 bits of ports P1 and P2 Read/write access using regular MSP430 byte instructions Individually programmable pull-up/pull-down resistors The available digital I/O pins for the hardware development tools: eZ430-F2013: 10 pins - P1 (8 bits) and P2 (2 bits); eZ430-F2274: 32 pins – P1, P2, P3, and P4 BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 36 Digital I/O 8-bit Digital I/O Registers Direction Register (PxDIR): Input Register (PxIN): Bit = 1: the individual port pin is set as an output Bit = 0: the individual port pin is set as an input When pins are configured as GPIO, each bit of these read-only registers reflects the input signal at the corresponding I/O pin Bit = 1: The input is high Bit = 0: The input is low Output Register (PxOUT): Each bit of these registers reflects the value written to the corresponding output pin. Bit = 1: The output is high; Bit = 0: The output is low. Note: the PxOUT is a read-write register which means previously written values can be read, modified, and written back BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 37 Digital I/O Select Digital I/O Registers Function Select Registers: (PxSEL) and (PxSEL2): PxSEL PxSEL2 Pin Function 0 0 0 1 Selects general purpose I/O function Selects the primary peripheral module function 1 0 Reserved (See device-specific data sheet) 1 1 Selects the secondary peripheral module function Port P2.0 Example: P2SEL.0 ADC10AE0.0 0 0 General-purpose digital I/O pin 1 0 ACLK output X 1 ADC10, analog input A0 / OA0, analog input I0 BYU CS/ECEn 124 Pin Function Chapter 6 - MSP430 Micro-Architecture 38 Digital I/O Interrupt Digital I/O Registers Interrupt Enable (PxIE): Interrupt Edge Select Registers (PxIES): Read-write register to enable interrupts on individual pins on ports P1/P2 Bit = 1: The interrupt is enabled Bit = 0: The interrupt is disabled Each PxIE bit enables the interrupt request associated with the corresponding PxIFG interrupt flag Selects the transition on which an interrupt occurs Bit = 1: Interrupt flag is set on a high-to-low transition Bit = 0: Interrupt flag is set on a low-to-high transition Interrupt Flag Registers (PxIFG) Set automatically when the programmed signal transition (edge) occurs PxIFG flag can be set and must be reset by software Bit = 0: No interrupt is pending Bit = 1: An interrupt is pending BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 39 Digital I/O Pull-up/down Register Pull-up/down Resistor Enable Registers (PxREN): Each bit of this register enables or disables the pull-up/pull-down resistor of the corresponding I/O pin Bit = 1: Pull-up/pull-down resistor enabled Bit = 0: Pull-up/pull-down resistor disabled. When pull-up/pull-down resistor is enabled, Output Register (PxOUT) selects: +3.3v Bit = 1: The pin is pulled up Bit = 0: The pin is pulled down. P2.0 P2.1 P2.2 P2.3 P2.4 BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 40 Digital I/O Port P1 Registers Register Name Short Form Address Register Type Initial State Input P1IN 020h Read only − Output P1OUT 021h Read/write Unchanged Direction P1DIR 022h Read/write Reset with PUC Interrupt Flag P1IFG 023h Read/write Reset with PUC Interrupt Edge Select P1IES 024h Read/write Unchanged Interrupt Enable P1IE 025h Read/write Reset with PUC Port Select P1SEL 026h Read/write Reset with PUC Port Select 2 P1SEL2 041h Read/write Reset with PUC Resistor Enable P1REN 027h Read/write Reset with PUC BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 41 BYU CS/ECEn 124 Chapter 6 - MSP430 Micro-Architecture 42