VADA Lab.

advertisement

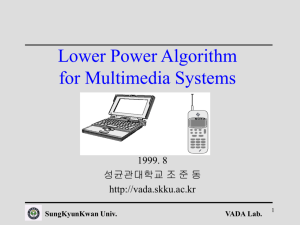

L20 :Lower Power Booth

Multiplier Design

성균관대학교

전기전자컴퓨터공학부

SungKyunKwan Univ.

VADA Lab.

1

Reduandant Binary-based

Booth Multipler

• 곱셈은 덧셈과 함께 correlation, convolution, filtering,

DFT(Discrete Fourier Transform) 등과 같은 디지털 신호 처리에

있어서 가장 많이 사용되는 연산이다.

• 현재 가장 많이 사용되는 곱셈기는 부분합들을 만들어 내는 인코

더부분은 Booth 인코더를, 부분합들을 더하는 adder array에는

Wallace Tree를 이용하는 곱셈기이다.

• 본 논문에서는 2의 보수가 아닌 Redundant Binary 표현( -1, 0, 1 )

을 사용하는 Booth 인코더를 제안하였고, 이를 Carry-

Propagation-Free Adder를 사용하여 부분곱들을 더하는 새로운

곱셈기를 제안하였다.

SungKyunKwan Univ.

VADA Lab.

2

목 차

•

•

•

•

•

•

•

•

•

•

연구의 중요성

연구배경

Modified Booth 곱셈기

Wallace Tree - 4:2 Compressor

제안된 Carry-Propogation-Free Adder

제안된 Basic Encoding Method (BEM)

제안된 Extended Encoding Method (EEM)

제안된 곱셈의 Block Diagram

실험결과

결론 및 향후계획

SungKyunKwan Univ.

VADA Lab.

3

Modified Booth 곱셈기

Multibit Recoding을 사용하여 부분합의 갯수를 n/2개로 줄여

고속의 곱셈을 가능하게 한다.

피승수(multiplicand) : X , 승수(multiplier) : Y

Recoded digit = Y2i-1 + Y2i -2Y2i+1 ( Y-1=0 )

Y2i+1 Y2i

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

Y2I-1

Recoded

Digit

Operation

on X

0

1

0

1

0

1

0

1

0

+1

+1

+2

-2

-1

-1

0

0X

+1X

+1X

+2X

-2X

-1X

-1X

0X

Recoded Digit

Operation on X

0

:

Add 0 to the partial product

+1

:

Add X to the partial product

+2

:

Shift left X one position and add it

to the partial product

-1

:

Add two’s complement of X to the

partial product

-2

:

Take two’s complement of X and

shift left one position

< Generation and operation of recoded digit >

SungKyunKwan Univ.

VADA Lab.

4

Modified Booth 곱셈기 - 예

sign

extension

(-107)

10010101 = X

(+105)

01101001 = Y

1111111110010101

00000011010110

000001101011

1100101010

Operation

Bits recoded

+1

-2

-1

+2

010

100

101

011

1101010000011101 = P (-11235)

SungKyunKwan Univ.

VADA Lab.

5

Wallace Tree - 4:2 Compressor

..............

..............

X7

Y7

X0

Y0

: Zero

: Bit jumping level

: partial product

: bit generated by

compressor

1st stage

2nd stage

Two summands to

be added

(a)

Y

1st stage

(block A)

1st stage

(block B)

2nd stage

(block C)

8

4*8 Partial Product generators

4

X3 , X2 , X1 , X0

8 4-2 compressors

4*8 Partial Product generators

4

X7 , X6 , X5 , X4

8 4-2 compressors

11 4-2 compressors

16-bit adder

P15

P0

(b)

SungKyunKwan Univ.

VADA Lab.

6

Multipliers - Area

•

16-bit Multiplier Area

2

Multiplier

type

Area(mm )

Gate count

Array

4.2

2,378

Wallace

8.1

2,544

Modified booth

8.5

3,375

SungKyunKwan Univ.

VADA Lab.

7

Multiplier - Delay

•

Average Power Dissipation (16-bit)

Multiplier

type

Power(mW)

Logic

transitions

Array

43.5

7,224

Wallace

32.0

3,793

Modified booth

41.3

3,993

SungKyunKwan Univ.

VADA Lab.

8

Multiplier - Power

•

Worst-Case Delay (16-bit)

Multiplier

type

Delay(ns)

Gate

delays

Array

92.6

50

Wallace

54.1

35

Modified booth

45.4

32

SungKyunKwan Univ.

VADA Lab.

9

Carry-Propagation-Free Adder

•

•

•

Carry-Propagation-Free adder는 carry propagation의 발생없이 2진 트리형태로 덧셈이 가능하기

때문에 고속 및 저전력을 실현할 수 있다.

Carry-Propagation-Free adder는 다음과 같은 2단계로 구성된다

– 첫번째 단계 : intermediate sum과 intermediate carry를 만드는 단계

– 두번째 단계 : final sum을 만드는 단계

첫번째 단계에서의 계산 법칙

Type

<1>

<2>

<3>

<4>

<5>

<6>

Digits at the next

Intermediate Intermediate

Augend digit Addend digit lower order position

carry

sum

(xi)

(yi)

(xi-1 , yi-1)

(ci)

(si)

1

1

1

0

0

1

0

0

1

1

1

1

0

1

1

1

0

1

SungKyunKwan Univ.

1

0

both are

nonnegative

1

1

otherwise

0

1

0

0

0

1

1

1

1

0

both are

nonnegative

otherwise

VADA Lab.

10

제안된 Carry-Propagation-Free Adder

•

•

Redundant binary 표현은 { 1 , 0, -1 }으로 구성된다.

다음과 같이 하나의 digit를 두 개의 bits로 표현한다.

Redundant

Binary Value

Binary Value

S bit

V

bit

1

1

0

0

0

0

1

0

1

곱셈 연산은 shift-and-add 알고리즘을 사용하기 때문에 덧셈기는 다음과

같이 세 부분으로 구성된다.

augend

n-bit

addend

n-bit

Remain adder

SungKyunKwan Univ.

Body adder

Pass adder

VADA Lab.

11

제안된 Basic Encoding Method (BEM)

•

•

Multibit Recoding과 Booth 인코더를 위해서는 새로운 코딩이 필요하다.

제안된 코딩은 양수와 음수로 나누어 진다.

– 양수인 경우

Y =

n-2

å

i=0

yi Î {0,1} , y n -1 = 0

y i 2 i 여기에서,

– 음수인 경우

Y =

n-2

å

i=0

•

y i 2 i 여기에서, yi Î {0, 1} , y n -1 = 0

그러므로, RB으로 구성된 Y(n-bit)는

Y =

n -1

å

i=0

=

y i 2 i 여기에서, yi Î {0,1} or {0, 1} , y n -1 = 0

n -1

2

å (y

i=0

2 i -1

SungKyunKwan Univ.

+ y 2 i - 2 y 2 i +1 ) 2 2 i

VADA Lab.

12

제안된 Basic Encoding Method (BEM) - 예

•

4-bit 코딩의 예

양 수

음 수

0000

0001

0010

0011

0100

0101

0110

0111

000 1

00 10

00 11

0100

0101

0110

0111

SungKyunKwan Univ.

VADA Lab.

13

제안된 Extended Encoding Method (EEM)

•

•

•

BEM 방법은 세 가지 digits({ , 0,11 })를 사용하므로 면적, 속도 그리고

전력 소비 면에서 단점을 가지고 있다.

이러한 단점을 보안하기 위한 아래 식과 같은 새로운 Extended Encoding

Method(EEM)를 제안한다.

EEM은 Virtual MSB(

)를

s n - 1사용한 코딩 방식이다.

– 양수인 경우 (

Y =

s n - 1 =) 0

n-2

å

i=0

y i 2 i, 여기에서

yi Î {0,1}

s n - 1 )= 1

– 음수인 경우 (

n-2

, 여기에서

Y = - å yi 2 i

yi Î {0,1}

i=0

SungKyunKwan Univ.

VADA Lab.

14

제안된 Extended Encoding Method (EEM)

-예

•

4-bit 코딩의 예

양 수

음 수

0000

0001

0010

0011

0100

0101

0110

0111

1001

1010

1011

1100

1101

1110

1111

SungKyunKwan Univ.

VADA Lab.

15

Conversion 알고리즘

•

2의 보수의 제안된 EEM으로의 변환은 다음과 같다.

– 양수인 경우

[ y n - 2 L L y 0 ] 2 = [ y n - 2 L L y 0 ] SD, 여기에서

2

yi Î {0,1}

– 음수인 경우

[[ y n - 2 L L y 0 ] 2 ] 2 = [ y n - 2 L L y 0,]여기에서

SD 2

•

yi Î {0,1}

8 bits인 경우의 예

[ 0 0 1 1 1 0 1 0 ]2

[ 1 0 1 1 1 0 1 0 ]2

SungKyunKwan Univ.

convert

convert

[ 0 0 1 1 1 0 1 0 ]SD2

[ 1 1 0 0 0 1 1 0 ]SD2

VADA Lab.

16

Redundant Binary (RB) Booth 곱셈기

•

•

RB를 사용하여 Booth 새로운 인코더를 제안한다.

Recoded Digit ( s n - 1 = 0 )= Y2i-1 + Y2i -2Y2i+1 ( Y-1=0)

•

Receded Digit ( s n - 1 = 1 )= - ( Y2i-1 + Y2i -2Y2i+1) ( Y-1=0)

Recoded Digit의 생성과 역할

y2i-1

y2i

y2i+1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

Recoded Operation

Digit

on X

0

+1

+1

+2

-2

-1

-1

0

s n - 1 = 0 인 경우

SungKyunKwan Univ.

0X

+1X

+1X

+2X

-2X

-1X

-1X

0X

y2i-1

y2i

y2i+1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

Recoded Operation

Digit

on X

0

-1

-1

-2

+2

+1

+1

0

0X

-1X

-1X

-2X

+2X

+1X

+1X

0X

s n - 1 = 1 인 경우

VADA Lab.

17

Redundant Binary (RB) Booth 곱셈기

•

Example

Multiplicand (X)

[ 0

1

1

0

1

1

0

1 SD2

]

(+109)

Multiplier (Y)

[ 1

1

1

0

1

0

1

0 SD2

]

(-106)

1

0 SD2

]

[ 0

1

1

0

1

1

0

1

1

0

1

1

0

1 SD2

]

0

1

1

0

1 SD2

]

[ 0

[ 0

+

[ 0

•

1

1

[ 1

1

1

0

1

1

0

1

0 SD2

]

0

1

1

0

1

1

1

0

1

1

0

0

0

1

0 ]

SD2

Recoded

Digit

Multibit

+2

1 0 0

+1

1 0 1

+1

1 0 1

-2

0 1 1

(-11554)

제안된 알고리즘의 장점

– carry propagation이 발생하지 않는다.

– Sign extension 부분이 필요하지 않다.

– 4:2 compressor를 사용하지 않으면서도 시스템의 성능을 저하시키지 않는

다.

– 부분합을 생성하는 과정에서 area, speed 그리고 power를 최소화하였다.

SungKyunKwan Univ.

VADA Lab.

18

제안된 곱셈기의 Block Diagram

X

Converter

Y

Converter

Booth

Encoder

Booth

Selector

Carry-PropagationFree Adder

Product

Converter

P

SungKyunKwan Univ.

VADA Lab.

19

실험결과 - Area

Multiplier

Bits

DW02_mult

BW

PRB

8

633

1092

862

16

2760

5093

3955

24

6365

10760

9581

32

11647

20097

17151

AREA

25000

20000

15000

gates

BW

PRB

DW02_mult

10000

5000

0

8

16

24

32

bits

SungKyunKwan Univ.

VADA Lab.

20

실험결과 - Delay

Multiplier

Bits

DW02_mult

BW

PRB

8

56.20

44.59

31.84

16

114.92

93.87

46.63

24

164.50

121.468

64.96

32

283.03

195.636

79.48

DELAY

300

250

delay(ns)

200

150

BW

PRB

DW02_mult

100

50

0

8

16

24

32

bits

SungKyunKwan Univ.

VADA Lab.

21

실험결과 - Power Dissipation

Multiplier

Bits

DW02_mult

BW

PRB

8

158.9884

177.8834

110.6359

16

1284.2

684.4495

527.8419

24

4226.9

1312.4484

1218.3944

32

6028.4

2278.5924

2149.9752

POWER DISSIPATION

7000

power dissipation(uw)

6000

5000

4000

BW

PRB

DW02_mult

3000

2000

1000

0

8

16

24

32

bits

SungKyunKwan Univ.

VADA Lab.

22

결론 및 향후계획

•

본 논문에서는 Redundant Binary를 사용하여 고성능, 저전력의 Booth

곱셈 알고리즘을 제안하였다.

•

제안된 곱셈기의 특징은 다음과 같다.

– Booth 알고리즘을 사용하여 n/2개의 부분곱을 생성하므로 고속의 연산을 가

능하게 하였다.

– Redundant Binary수치계를 이용한 carry-propagation-free adder를 사용하

여 고속, 저전력을 실현하였다.

– 새로운 encoding 알고리즘을 제안하여 부분곱 생성과정에서 면적, 속도 그리

고 전력면에서 많은 이득을 얻을 수 있었다.

– Redundant Binary로 인하여 array 곱셈기보다는 면적의 증가가 있지만,

Wallace tree를 이용한 Booth 곱셈기보다는 면적의 감소가 있었다.

•

향후 제안된 곱셈기는 Digital Signal Processing(DSP)분야에 매우 효과

적으로 이용될 수 있을 것이다.

SungKyunKwan Univ.

VADA Lab.

23

References

• A. Chandrakasan and R. Brodersen, Low Power CMOS

Design Kluwer Academic Publishers, 1995.

• J. Rabaey and M. Pedram, Ed., 밚ow Power Design

Methodologies Kluwer Academic Publishers, 1995.

• Proceedings of the IEEE, Special Issue on Low Power,

April 1995.

SungKyunKwan Univ.

VADA Lab.

24

Modified Booth 곱셈기

• Multibit Recoding을 사용하여 부분합의 갯수를 1/2로 줄여 고속의

곱셈을 가능하게 한다.

• 피승수(multiplicand) : X , 승수(multiplier) : Y

Recoded digit = Y2i-1 + Y2i -2Y2i+1 ( Y-1=0 )

Y2i+1

0

0

0

0

1

1

1

1

Y2i

0

0

1

1

0

0

1

1

Y2I-1

0

1

0

1

0

1

0

1

Recoded

Digit

0

+1

+1

+2

-2

-1

-1

0

Operation

on X

0X

+1X

+1X

+2X

-2X

-1X

-1X

0X

Recoded Digit

Operation on X

0

:

Add 0 to the partial product

+1

:

Add X to the partial product

+2

:

Shift left X one position and add it

to the partial product

-1

:

Add two’s complement of X to the

partial product

-2

:

Take two’s complement of X and

shift left one position

< Generation and operation of recoded digit >

SungKyunKwan Univ.

VADA Lab.

Modified Booth 곱셈기 - 예

•

Example

sign

extension

(-107)

10010101 = X

(+105)

01101001 = Y

1111111110010101

00000011010110

000001101011

1100101010

Operation

Bits recoded

+1

-2

-1

+2

010

100

101

011

1101010000011101 = P (-11235)

SungKyunKwan Univ.

VADA Lab.

26

Wallace Tree - 4:2 Compressor

X7

Y7

..............

..............

X0

Y0

: Zero

: Bit jumping level

: partial product

: bit generated by

compressor

1st stage

2nd stage

Two summands to

be added

(a)

Y

1st stage

(block A)

1st stage

(block B)

2nd stage

(block C)

8

4*8 Partial Product generators

4

X3 , X2 , X1 , X0

8 4-2 compressors

4*8 Partial Product generators

4

X7 , X6 , X5 , X4

8 4-2 compressors

11 4-2 compressors

16-bit adder

P15

P0

(b)

SungKyunKwan Univ.

VADA Lab.

27

Multipliers - Area

•

16-bit Multiplier Area

2

Multiplier

type

Area(mm )

Gate count

Array

4.2

2,378

Wallace

8.1

2,544

Modified booth

8.5

3,375

SungKyunKwan Univ.

VADA Lab.

28

Multiplier - Delay

•

Average Power Dissipation (16-bit)

Multiplier

type

Power(mW)

Logic

transitions

Array

43.5

7,224

Wallace

32.0

3,793

Modified booth

41.3

3,993

SungKyunKwan Univ.

VADA Lab.

29

Multiplier - Power

•

Worst-Case Delay (16-bit)

Multiplier

type

Delay(ns)

Gate

delays

Array

92.6

50

Wallace

54.1

35

Modified booth

45.4

32

SungKyunKwan Univ.

VADA Lab.

30

Instruction Level Power Analysis

•

•

Estimate power dissipation of instruction sequences and power dissipation of a

program

Eb : base cost of individual instructions

Es : circuit state change effects

EM = Eb +Es

E b = åB i N i

•

Es =

åO i j N i j

,

,

EM : the overall energy cost of a program

Bi : the base cost of type i instruction

Ni : the number of type i instruction

Oi,j : the cost occurred when a type i instruction is followed by

a type j instruction

Ni,j : the number of occurrences when a type i instruction is

immediately followed by a type j instruction

SungKyunKwan Univ.

VADA Lab.

Instruction ordering

•

•

Develop a technique of operand swapping

Recoding weight : necessary operation cost of operands

W

to tal

= åW

i

i

W i =W

•

•

b

+W

in ter

Wtotal : total recoding weight of input operand

Wi : weight of individual recoded digit i in Booth Multiplier

Wb : base weight of an instruction

Winter : inter-operation weight of instructions

Therefore, if an operand has lower Wtotal , put it in the second

input(multiplier).

SungKyunKwan Univ.

VADA Lab.

RESULT

Instruction

Base

Name

cost

Circuit State Effects[pJ]

when switched

LOAD

1.46

ADD

0.86

2’s

0.77

0.18

cost

SHIFT

1.20

1.08

0.73

LOAD

3.25

0.31

0.49

0.61

ADD

1.91

0.27

0.34

2’s

1.72

LOAD

ADD

2’s

complement

SHIFT

0.40

2.67

2.38

1.63

0.58

1.11

1.44

0.55

0.78

[pJ]

complement

SHIFT

Base

Name

2’s

complement

ADD

[pJ]

LOAD

Instruction

Circuit State Effects[pJ]

when switched

complement

0.29

0.15

SHIFT

< 4 b y 4 m ultip lier >

0.65

0.38

< 8 b y 8 m ultip lier >

Circuit State Effects[pJ]

when switched

Instruction

Name

Base

cost

[pJ]

LOAD

ADD

2’s

complement

SHIFT

LOAD

4.81

0.59

3.96

3.57

2.40

ADD

2.83

1.02

1.63

2.12

2’s

complement

2.55

1.00

1.14

SHIFT

0.96

0.78

< 12 b y 12 m ultip lier >

SungKyunKwan Univ.

VADA Lab.

Conclusion

% of instances with

circuit states effects

9.0%

reduction

Power[pJ]

35

12

30

10

12bit

8bit

0

4bit

5

bits

SungKyunKwan Univ.

4

2

0

average

10

6

12bit

circuit

states

effects

considered

4.0%

reduction

8

8bit

20

15

circuit

states

effects not

considered

12.0%

reduction

4bit

25

bits

VADA Lab.

References

[1] Gary K. Yeap, "Practical Low Power Digital VLSI Design",

Kluwer Academic Publishers.

[2] Jan M. Rabaey, Massoud Pedram, "Low Power Design Methodologies",

Kluwer Academic Publishers.

[3] Abdellatif Bellaouar, Mohamed I. Elmasry, "Low-Power Digital VLSI Design

Circuits And Systems", Kluwer Academic Publishers.

[4] Anantha P. Chandrakasan, Robert W. Brodersen, "Low Power Digital CMOS

Design", Kluwer Academic Publishers.

[5] Dr. Ralph Cavin, Dr. Wentai Liu, "1996 Emerging Technologies : Designing

Low Power Digital Systems"

[6] Muhammad S. Elrabaa, Issam S. Abu-Khater, Mohamed I. Elmasry,

"Advanced Low-Power Digital Circuit Techniques",

Kluwer Academic Publishers.

SungKyunKwan Univ.

VADA Lab.

35

References

•

•

•

•

•

[BFKea94] R. Bechade, R. Flaker, B. Kaumann, and et. al. A 32b 66 mhz 1.8W

Microprocessor". In IEEE Int. Solid-State Circuit Conference, pages 208-209,

1994.

[BM95] Bohr and T. Mark. Interconnect Scaling - The real limiter to high

performance ULSI". In proceedings of 1995 IEEE international electron devices

meeting, pages 241-242, 1995.

[BSM94] L. Benini, P. Siegel, and G. De Micheli. Saving Power by Synthesizing

Gated Clocks for Sequential Circuits". IEEE Design and Test of Computers,

11(4):32-41, 1994.

[GH95] S. Ganguly and S. Hojat. Clock Distribution Design and Verification for

PowerPC Microprocessor". In International Conference on Computer-Aided

Design, page Issues in Clock Designs, 1995.

[MGR96] R. Mehra, L. M. Guerra, and J. Rabaey. Low Power Architecture

Synthesis and the Impact of Exploiting Locality". In Journal of VLSI Signal

Processing,, 1996.

SungKyunKwan Univ.

VADA Lab.

36