ppt

advertisement

ECE 368: CAD-Based Logic Design

Lecture Notes # 5

Sequential Circuit (Finite-State Machine) Design

SHANTANU DUTT

Department of ECE

University of Illinois, Chicago

Phone: (312) 355-1314: e-mail: dutt@ece.uic.edu

URL: http://www.ece.uic.edu/~dutt

1

Finite State Machine (FSM) Design

• FSMs are different from counters in the sense that they have external

I/Ps, and state transitions are dependent on these I/Ps and the current

state.

• Example : Problem Statement

There is a bit-serial I/P line. Design an FSM that outputs a ‘0’

if an even # of 1’s have been received on the I/P line and the

outputs a ‘1’ otherwise.

Note : If a synchronous sequential circuit is being designed, the counting

of the # of 1s occur every clock cycle.

x

O/p y

Sampling

FSM

Tlogic + Tsetup

instances

CLK

CLK

x

# of even

1s (0)

odd

(1)

even

(2)

odd

(3)

odd

(3)

2

Approach to determining states of an FSM:

• First determine the min # of useful information classes about past i/ps required to

solve the problem (requires analytical thinking about the problem)

• Each info class a potential state

• From this 1st cut at possible states, determine if there are well-defined transitions

from each state for all possible i/p values.

• If so then these states can be the final states; otherwise some states may need to be

refined into multiple states to achieve well-defined transitions (see FSM word prob. 1).

• In this problem, only 2 classes of information are reqd: whether an even # of 1s have

been received so far, or an odd # of 1s have been received so far & there are welldefined transitions between them. Thus these 2 classes become 2 states.

Solution 1: (Mealy)

Solution 2: (Moore)

0/0

Reset

Even

Transition

Arc

Reset

Odd

Even

Input

1/1

1/0

0

Output

Output

[0]

O/P is dependent

on current state and

input in Mealy

1

1

Odd

[1]

0

0/1

Mealy Machine: Output is associated with the

state transition, and appears before the state

transition is completed (by the next clock pulse).

Input

Output is

dependent only

on current state

Moore Machine: Output is associated

with the state and hence appears

after the state transition take place.

Determining a Reset State:

• A reset state is a state the the FSM (seq ckt) should be in when it is just powered on.

• In other words, a reset state is a state the FSM should be in, when it has recvd no i/ps

• Based on the above definition, decide if any of the states determined so far can be a

reset state. E.g., in the parity detector problem, the even state qualifies to be the reset

state, as in the reset state no i/ps recvd zero 1’s recvd even # of 1’s recvd it can

be the even state

• If not, then need to have a separate reset state, and have the correct transitions from

this state to the other states (depending on the problem solved by the FSM).

Solution 1: (Mealy)

Solution 2: (Moore)

0

0/0

Reset

Even

Odd

Even

Input

1/1

1/0

Transition

Arc

Reset

Output

Output

[0]

O/P is dependent

on current state and

input in Mealy

1

1

Odd

[1]

0/1

Mealy Machine: Output is associated

with the state transition, and appears

before the state transition is completed

(by the next clock pulse).

0

Input

Output is

dependent only

on current state

Moore Machine: Output is associated

with the state and hence appears

after the state transition take place. 4

External I/Ps

External O/Ps

m1

Comb.

Logic

n even

odd

Output

Logic

n

t+

n

CLK

External Outputs

Moore Machine Model

Mealy Machine Model

t

FFs

m2

CLK

Time t : Even I/P

Next State

Comb.

Logic

m2

FFs

n

External

I/Ps

m1

= propagation delay of logic of Mealy M/C

t+TCLK t+TCLK+2

Even

Odd O/P=1

O/P=1

x=1

(Moore)

(Mealy)

O/P=0

2 = propagation delay of O/P

logic unit of Moore M/C

5

State Transition Table

(Even-Parity Checker)

Even State: 0 ;

Present

State

Input

Odd State: 1;

Next

State

State Variable A

Moore

O/P

Mealy

O/P

D-FF

Excit.

y1

y2

DA

T-FF

Excit.

A

x

A+

0

0

1

0

1

0

0

1

1

0

0

1

0

1

1

0

1

1

0

1

0

1

1

0

1

0

0

1

Input variables

to comb. logic

DA= Ax (same for Moore

and Mealy);

TA= x (same for Moore

and Mealy);

y1 = A for Moore

y2 = Ax for Mealy

TA

Output functions

y2

x

N.S. & O/P

Logic

Q

A FF

x

N.S.

Logic

Or

Q

DA

CLK

A

O/P

Logic

FFs

DA

y1

6

Reset

State=0

Even

0

0/0

Reset

State=0

Even

[0]

1/1

1/0

1

1

State=1

Odd

N.S.

Logic

x

State=1

Odd

[1]

Q

0/1

Q

Mealy

0

D-

FF D

Moore

CLK

S.T. is complete.

Assume single bit state information stored in a D-FF

State Transition State Transition

is occurring

is occurring

S.T. is complete.

CLK

x

D

even

Q

odd

even

even

odd

odd

(state)

y2

(Mealy O/P)

7

y1

Moore

O/P)

DA= Ax ;

TA= x; y1 = A for Moore; y2 = Ax for Mealy

Moore M/C Implementation

a) D-FF

b) T-FF

x

0

D

x=1

Q

R

CLK

A

y2

T

CLK

Q

R

Q

A

y2

Q

Reset

Reset

Moore O/P is synchronized with clock.

Mealy M/C Implementation

y1

0

1

D

x=1

CLK

Q

R

x

T

A

CLK

Q

R

y1

Q

Q

Reset

a) D-FF

Mealy O/P is not

synchronized with clock.

Reset

b) T-FF

Note: Here Moore and Mealy state transition

8

function is the same. Will not always be the case.

Difference Between Mealy and Moore Machine

Mealy

(1) O/Ps depend on the present

state and present I/Ps

(2) The O/P changes asyn

-chronously with the

enabling clock edge

(3)

(4)

A counter is not a Mealy

machine

A Mealy machine will have

the same # or fewer states

than a Moore machine

Moore

O/Ps depend only on the

present state

Since the O/Ps change

when the state changes,

and the state change is

synchronous with the

enabling clock edge, O/Ps

change synchronously

with this clock edge

A counter is a Moore

machine

9

Behavioral FSM Descriptions in VHDL – 1st Cut

Moore machine

0

Reset

Even

[0]

x

Q

FFs

O/P

Logic

1

1

N.S.

C.S.

N.S.

Logic

Odd

[1]

0

y

• Simple very high-level behavioral

description w/o timing (no clock,

no delays)

• Checks only the high-level FSM

logic

• No parallelism

• If timing and/or parallelism of the

underlying hardware is desired we

need to introduce clocks, delays

and multiple processes

entity fsm1_1 is

port (x, reset:in bit; y: out bit:=`0’)

end entity fsm1_1

architecture behav of fsm1_1 is

type states is (even, odd);

begin

state_mc: process (x, reset) is

variable curr_state, next_state: states := even;

-- initial state is reset state

begin

if reset = ‘1’ then curr_state := even; y <= ‘0’;

else

case curr_state is

when even => y <=`0’; -- assert output

-- next determine transition based on input

if x=`1’ then next_state := odd;

else next_state := even; end if;

when odd => y <= `1’; -- assert output

if x=`1’ then next_state := even;

else next_state := odd; end if;

end case;

curr_state := next_state;

end if;

end process state_mc;

10

end architecture behav;

Behavioral FSM Descriptions in VHDL – 2nd Cut

Moore machine

Reset

0

Even

[0]

1

1

Odd

[1]

0

x

Q

FFs

O/P

Logic

N.S.

C.S.

N.S.

Logic

y

entity fsm1_2 is

port (x, clk, reset:in bit; y: out

bit:=`0’)

end entity fsm1_2

architecture behav of fsm1_2 is

type states is (even, odd);

begin

state_mc: process is

variable curr_state, next_state: states := even; -- reset state

begin

wait until (clk’event and clk=`1’) or (reset=`1’);

if reset = ‘1’ then curr_state := even; y <= `0’ after 2 ns;

else

-- note need of curr_state to be variable for immediate effect

case curr_state is

when even => y <=`0’ after 2 ns; -- assert outputs

-- next determine transition based on input

if x=`1’ then wait for 2 ns; next_state := odd;

else wait for 2 ns; next_state := even; end if;

when odd => y <= `1’ after 2 ns; -- assert outputs

if x=`1’ then wait for 2 ns; next_state := even;

else wait for 2 ns; next_state := odd; end if;

end case;

curr_state := next_state;

end if;

end process state_mc;

end architecture behav;

Problem w/ the description: The N.S. logic is simulated only on the clock edge. Actually, it should

be simulated anytime x or C.S. changes (note that the latter changes w/ some delay after the clock

edge, not @ the clock edge), and this does not happen in the code.

11

Behavioral FSM Descriptions in VHDL – Final Cut

General solution to behavioral description of a system (described in an arch) – when to have multiple

processes:

-- If a design has different components, each operating or triggered w/ different timing events, then

separate them into individual processes.

-- In other words a single process should not describe multiple components triggered by different timing

events

-- Furthermore if signal assignments to, say, signal X, in a process should affect the rest of the logic in it in

the current iteration and X cannot be made a variable (if it is also an o/p of the process, e.g., when it is an

i/p signal of another process), separate out the X-dependent logic as a separate process

-- In a Moore machine, we have 3 modules, FFs, N.S. logic and O/P logic. FF is triggered by the clock +ve

edge. Its o/p C.S. triggers the O/P logic; so it is also ultimately triggered by the clock. The N.S. logic is

triggered by C.S. and x, where x has no relation to the clock.

-- So a possible breakup is Process 1: FFs + O/P Logic and Process 2: N.S. Logic. But not a good idea as:

-- C.S. needs to be a signal i/p to the N.S. Logic and FF processes to communicate

-- Since the O/P Logic depends on C.S., if it is in the same process as the FF, there will not be any effect

from the FF to the O/P Logic modules in the current iteration (in other words, combined FF+O/P process

will need to be simulated more times (i.e., it has to be activated by more events) to propagate final values

to o/p of O/P module). So separate out the O/P Logic as a 3rd process

-- Large processes resulting from the above partitioning methodology may be further broken up

functionally (i.e., by functional modules, e.g., ALU and Register File in a Datapath process of a CPU)

and/or if some parallelism of the underlying hardware is desired to be simulated and/or communication

Process 2

between these modules need to be simulated x

X <= …..

Process B

Y <= X nand Z;

Q

FFs

Process3

O/P

Logic

N.S.

C.S.

Process A

N.S.

Logic

clock

y

12

Process 1

Behavioral FSM Descriptions in VHDL – Final Cut

architecture behav of fsm1_3 is

type states is (even, odd);

signal next_state, curr_state: states := even;

begin

Moore machine

0

Even

Reset

[0]

1

1

Odd

[1]

0

Process 2

C.S.

N.S.

Logic

Q

FFs

N.S.

x

clock

O/P

Process 1

y

Process3 Logic

Note: When all processes block, sim. time

is advanced by at least the fictitious delta

time or min. delay across signals when at

least one unblocks, resulting in some

assigned signal values (w/ the corresponding

delay) appearing and causing

corresponding processes to unblock (those

w/ wait statements dependent on these

signals).

entity fsm1_3 is

port (x, clk, reset:in bit; y: out

bit:=`0’)

end entity fsm1_3

ns_proc: process (curr_state, x) is

begin

case curr_state is

when even => if x=`1’ then next_state <= odd after 2 ns;

else next_state <= even after 2 ns; end if;

when odd => if x=`1’ then next_state <= even after 2 ns;

else next_state <= odd after 2 ns; end if;

end case;

end process ns_proc;

ff_proc: process is

begin

wait until (clk’event and clk=`1’) or (reset=`1’);

if reset = ‘1’ then curr_state <= even;

else curr_state <= next_state; end if;

end process ff_proc;

op_proc: process (curr_state) is

begin

case curr_state is

when even => y <=`0’ after 2 ns; -- assert outputs

when odd => y <= `1’ after 2 ns;

end case;

end process op_proc;

13

end architecture behav;

Behavioral FSM Descriptions in VHDL– First Cut

Mealy Machine

0/0

Reset

Even

1/1

1/0

Odd

Transition

Arc

0/1

y2

x

N.S. & O/P

Logic

Q

C.S. FF

N.S.

CLK

entity fsm2_1 is

port (x, clk, reset:in bit; y: out bit:=‘0’)

end entity fsm2_1

architecture behav of fsm2_1 is

type states is (even, odd);

begin

state_mc: process is

variable next_state, curr_state: states := even; -- reset state

begin

wait until (clk’event and clk=`1’) or (reset=`1’);

if reset = ‘1’ then curr_state := even;

else curr_state := next_state; end if;

case curr_state is

when even => if x=`1’ then y <= `1’ after 2 ns;

wait for 2 ns; next_state := odd;

else y <= `0’ after 2 ns;

wait for 2 ns; next_state := even after 2 ns; end if;

-- note: above times are arbitrary; just for e.g.

when odd => if x=`1’ then y <=`0’ after 2 ns;

wait for 2 ns; next_state := even after 2 ns;

else y <= `1’ after 2 ns;

wait for 2 ns; next_state := odd after 2 ns;

end if;

end case;

end process state_mc;

end architecture behav;

Problem w/ the description: The N.S. & O/P logic is simulated only on the

clock edge. Actually, it should be simulated anytime x or C.S. changes. The

latter happens but not the former.

14

Behavioral FSM Descriptions in VHDL– Final Cut

Mealy Machine

0/0

Reset

Even

1/1

1/0

Odd

Transition

Arc

0/1

y2

x

N.S. & O/P

Logic

Q

C.S. FF

N.S.

CLK

entity fsm2_2 is

port (x, clk, reset:in bit;

y: out bit:=‘0’)

end entity fsm2_2

architecture behav of fsm2_2 is

type states is (even, odd);

signal next_state, curr_state: states := even;

begin

ns_op_proc: process (x, curr_state) is

begin

case curr_state is

when even => if x=`1’ then y <= `1’ after 2 ns;

next_state <= odd after 2 ns;

else y <= `0’ after 2 ns; next_state <= even after 2 ns;

end if;

-- note: above times are arbitrary; just for e.g.

when odd => if x=`1’ then y <=`0’ after 2 ns;

next_state <= even after 2 ns;

else y <= `1’ after 2 ns; next_state <= odd after 2 ns;

end if;

end case;

end process ns_op_proc;

ff_proc: process is

begin

wait until (clk’event and clk=`1’) or (reset=`1’);

if reset = ‘1’ then curr_state <= even;

else curr_state <= next_state; end if;

end process ff_proc;

end architecture behav;

15

Another example: A simple vending machine

Here is how the control is supposed to work. The vending machine delivers

a package of gum after it has received 15 cents in coins. The machine has a single

coin slot that accepts nickels and dimes, one coin at a time. A mechanical sensor

indicates to the control whether a dime or a nickel has been inserted into the coin slot.

The controller’s output causes a single package of gum to be released down a chute

to the customer.

One further specification: We will design our machine so it does not give

change. A customer who pays with two dimes is out 5 cents!

Coin

Sensor

CLK

Vending

Machine

FSM

Open

Gum

Release

Mechanism

Reset (ext.)

OR time_outTimer

Vending Machine block diagram

States:

0C

5C

10C

15C

16

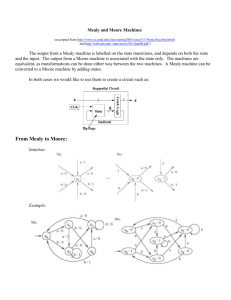

— The figure below show the Moore and Mealy machine state transition diagrams.

( N D Reset )/0

0 cent

[0]

Reset

ND

0 cent

Reset / 0

N D /0

N/0

N

5 cent

[0]

D

( N D Reset )/0

Reset / 0

Reset

D/0

D

N

10 cent

[0]

Moore machine

D/1

N/0

ND

10 cent

N D /0

N+D

15 cent

[1]

5 cent

N+D/1

Reset

15 cent

Reset / 1

Mealy machine

Moore and Mealy machine state diagrams for the vending machine FSM

17

Behavioral VHDl description of Moore vending machine controller

statement

timer: process is

wait until open1 = `1’;

time_out = `1’ after 20 sec;

wait for 20 sec;

time_out = `0’ after 10 ns;

-- timeout signal is high for 10 ns;

if open1 = `1’ then wait until open1 = `0’;

end process timer;

(N D

N

Reset

Reset

)/0

0 cent

D

[0]

ext_reset

ND

N

5 cent

Reset

[0]

D

N

ND

D 10 cent

[0]

open1

N+D

15 cent

Moore

Reset

[1]

machine

ff_proc: process is

begin

wait until (clk’event and clk=‘1’) or (

reset=`1’);

if reset = ‘1’ then curr_state <= S0 after 1

ns;

else curr_state <= next_state after 1 ns;

end if;

end process ff_proc;

op_proc: process (curr_state) is

begin

case curr_state is

when S0 => open1 <=` 0’ after 2 ns;

when S5 => open1 <= `0’ after 2 ns;

when S10 => open1 <=` 0’ after 2 ns;

when S15 => open1 <= `1’ after 2 ns;

end case;

end process op_proc;

entity vend_moore

reset <= ext_ reset or

time_out after 2 ns;

NS logic

process

time_out

Timer

proc

o/p logic

open1 proc

reset

curr_state

entity vend_moore is

port(N, D, ext_reset, clk: in bit;

open1:inout bit);

end entity vend_moore;

architecture behav of vend_moore is

type states is (S0, S5, S10, S15);

signal next_state, curr_state: states :=

even;

signal reset, time_out : bit := `0’;

begin

reset <= ext_ reset or time_out after 2

ns;

-- concurrent signal assignment

next_state

FF

proc Arch. behav

clk

18

Behavioral VHDl description of Moore vending machine controller

Reset

Reset

(N D

Reset)/0

0 cent

[0]

ND

Moore

machine D

N

5 cent

[0]

D

N

10 cent

[0]

ND

N+D

15 cent Reset

[1]

ns_proc: process (N, D, curr_state) is

case curr_state is

when S0 =>

if N=1 then next_state <= S5 after 2 ns; elsif

D=1 next_state <= 10 after 2 ns;

else next_state <= S0 after 2 ns;

end if;

when S5 =>

if N=1 then next_state <= S10 after 2 ns; elsif

D=1 next_state <= S15 after 2 ns;

else next_state <= S5 after 2 ns;

end if;

when S10 =>

if N=1 or D=1 then next_state <= S15 after 2

ns;

else next_state <= S10 after 2 ns;

end if;

when S15 =>

next_state <= S15 after 2 ns;

end case;

end process ns_proc;

end architecture behav;

19

—State transition table for Moore and Mealy M/C.(Next state also gives D-FF

excitation).

Present State

Q1 Q2

0 0

0 1

1 0

1 1

Inputs

D

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

N

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Next State

Q1+

0

0

1

x

0

1

1

x

1

1

1

x

1

1

1

x

Q2+

0

1

0

x

1

0

1

x

0

1

1

x

1

1

1

x

Moore Output Mealy Output

Open

0

0

0

x

0

0

0

x

0

0

0

x

1

1

1

x

Open

0

0

0

x

0

0

1

x

0

1

1

x

1

1

1

x

Q+ = D

Q Q+

0 0

0 1

1 0

1 1

Encoded vending machine state transition table. Note: Do not have to design

for the reset input if FFs have a direct reset inputs. Make sure though that reset state is

encoded as all 0’s if possible; otherwise need FFS w/ asynch. reset as well as set inputs

D

0

1

0

1

20

Implementation using D-FFs

Q1Q0

Q1Q0

00

01

11

10

00

0

0

1

1

01

0

1

1

11

x

x

10

1

1

DN

Q1Q0

00

01

11

10

00

0

1

1

0

1

01

1

0

1

x

x

11

x

x

1

1

10

0

1

K-map for D1

DN

00

01

11

10

00

0

0

1

0

1

01

0

0

1

0

x

x

11

x

x

x

x

1

1

10

0

0

1

0

DN

K-map for Open (Moore)

K-map for D0

Q1Q0

D1 = Q1 + D + Q0·N

D0 N Q0 Q0 N Q1 N Q1 D

OPEN = Q1·Q0

Moore OPEN = Q1·Q0 + D·Q0 + D·Q1 + N·Q1

00

01

11

10

00

0

0

1

0

01

0

0

1

1

DN

11

x

x

x

x

10

0

1

1

1

Mealy

K-map for Open (Mealy)

21

Q1

D1

D

D

Q0

N

Q1

CLK

Q

R

Q1

Q

OPEN

Reset

N

Q0

Q0

D0

N

Q1

D

CLK

Q

R

Q

Similarly,

a Mealy

implementation;

only the OPEN

function changes.

Q0

Q0

N

Reset

Q1

D

Vending machine FSM implementation based on D flip-flops(Moore).

22

Implementation using J-K FFS

J-K Excitation

D N

Q 1+ Q2+

J1 K 1 J0 K 0

Q Q+

0 0

0

0

0 x

0 x

0 1

0

1

0 x

1 x

0 0

1 0

1

0

1 x

0 x

0 1

1 1

x

x

x x

x x

1 0

0 1

0 0

0

1

0 x

x 0

1 1

0 1

1

0

1 x

x 1

1 0

1

1

1 x

x 0

1 1

x

x

x x

x x

1 0

0 0

1

0

x 0

0 x

0 1

1

1

x 0

1 x

1 0

1

1

x 0

1 x

1 1

x

x

x x

x x

1 1

0 0

1

1

x 0

x 0

0 1

1

1

x 0

x 0

1 0

1

1

x 0

x 0

1 1

x

x

x x

x x

Remapped next-state functions for the vending machine example.

Q1 Q2

0 0

J

0

1

x

x

23

K

x

x

1

0

Q1Q0

00

01

11

10

00

0

0

x

x

01

0

1

x

11

x

x

10

1

1

DN

Q1Q0

00

01

11

10

00

x

x

0

0

x

01

x

x

0

0

x

x

11

x

x

x

x

x

x

10

x

x

0

0

DN

K-map for J1

K-map for K1

Q1Q0

Q1Q0

00

DN

00

01

0

1

01

11

10

x

x

0

x

x

1

00

01

11

10

00

x

0

0

x

01

x

1

0

x

DN

11

x

x

x

x

11

x

x

x

x

10

0

x

x

1

10

x

0

0

x

K-map for J0

K-map for K0

K-maps for J-K flip-flop implementation of vending machine.

J1 = D + Q0·N

J 0 Q0 N Q1 D

K1 = 0

K 0 Q1 N

24

N

Q0

CLK

D

Q0

J

Q

K R

Q

Q1

Q1

OPEN

N

Q1

D

CLK

Q1

J

Q

K R

Q

Q0

Q0

N

Reset

J-K flip-flop implementation for the vending machine example (Moore).

Similarly, a Mealy implementation; only the OPEN function changes.

25

Basic Steps in the FSM Design Procedure

1. Understand the problem and the different information classes (minimal

number) required to solve it. Also make sure there are well-defined transitions

possible between these classes; otherwise break down some or all classes into

smaller classes to get well-defined transitions.

2a. Convert these information classes into distinct states, and determine the state

transition diagram of the FSM. Determine reset state.

2b Optional: Perform state minimization

3a. Encode states in binary, and obtain state transition table and FF excitation (for

desired FF type).

3b Optional: Perform state assignment for minimizing logic.

4. Minimize the FF excitation functions and output functions (using K-Maps, for

example) and implement the FSM using these FFs and logic gates (or MUXes,

PLAs, etc.) that implement the output and FF excitation functions.

26

FSM Word Problem 1:

• Design a system that outputs a ‘1’ whenever it receives a multiple

of 3 # of 1’s (i.e., 0, 3, 6, 9, etc. # of 1’s) on a serial input line x.

— Relevant information classes needed to solve the problem:

(A) A multiple of 3 # is received.

(B) A non-multiple of 3 # is received.

Questions to consider:

(1) How do we go from (A)(B)

Ans.: If a ‘1’ is received

(2) How do we go from (B)(A)

Ans.: Not clear. Need to split up (B) further into

(B1): 3y+1 # of 1’s received.

Where y is an integer 0.

(B2): 3y+2 # of 1’s received.

27

Note: (A): is 3y+0 = 3y # of 1’s received.

• Now the transitions between the3 classes of information is clear:

(A) (B1) (B2) (A)

1 received

1 received

1 received

• Hence these classes of information can be considered states of

the required as states of the required FSM:

These 3 states can be represented by 3y+I, i = 0,1,2

00

Reset

0/1

i=0

0

Output

Input

Reset

i=0

[1]

0/0

1/0

1/1

10

01

i=1

1/0

i=2

0/0

Mealy Machine

1

1

0

i=1

[0]

i=2

[0]

1

0

Moore Machine

28

FSM Word Problem 2:

• Design a system that outputs a ‘1’ whenever it receives:

(a) A multiple of 3 # of 1’s AND (b) A non-zero even # of 0’s

# of 1’s

E.g., ((0,2) , (3,2) , (3,4) , (6,2) ,···)

# of 0’s

— Relevant classes of information:

- For # of 1’s: 3y+i, i = 0,1,2

[3 classes]

- For # of 0’s: 2z+j, j = 0,1

For j = 0, we need to distinguish between zero (z = 0)

and non-zero (z > 0) # of 0’s

- Thus we have 3 classes:

2z+0, z = 0 ( 0 )

2z+0, z > 0 ( non-zero even )

2z+1

( odd )

29

The relevant # of 1’s can be represented by i = { 0, 1, 2 }

( # of 1’s = 3y+i )

— The relevant # of 0’s can be represented by j= { 00 , 0>0 , 1 }

( # of 0’s = 2z+j ) where the subscript of the 0 indicates whether

z=0 or z>0.

— Since at any point time, a certain # of 1’s and # of 0’s will have

been received, the state of the system will be given by

a combination of relevant # of 1’s and # of 0’s.

— There are 9 combinations:

{ 0, 1, 2, } X { 00, 0>0, 1 } = (0,00), (0,0>0), (0,1), (1,00), (1,0>0),

(1,1), (2,00), (2,0>0), (2,1)

# of 1’s

# of 0’s

Cartesian

Product

30

(0,00)

(0,0>0)

(1,00)

(0,1)

(2,00)

(1,1)

(2,1)

(1,0>0)

(2,0>0)

31

Note: 0>0 2z+j, j = 0

z>0

Reset

(0,00)

1/0

0/0

1/0

(0,0>0)

(1,00)

1/0

0/0

0/0

0/1

1/0

(0,1)

(2,00)

0/0

(1,1)

0/0

1/0

1/0

0/0

(2,1)

(1,0>0)

1/1

0/0

1/0

0/0

(2,0>0)

1/0

32