Chapter #8: Finite State Machine Design

advertisement

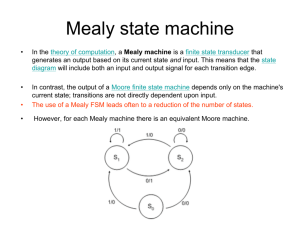

Contemporary Logic Design Finite State Machine Design Chapter #8: Finite State Machine Design 8.3 Alternative State Machine Representations 8.4 Mealy and Moore Machines Design © R.H. Katz Transparency No. 15-1 8.3 Alternative State Machine Representations Contemporary Logic Design Finite State Machine Design Why State Diagrams Are Not Enough Not flexible enough for describing very complex finite state machines Not suitable for gradual refinement of finite state machine Do not obviously describe an algorithm: that is, well specified sequence of actions based on input data algorithm = sequencing + data manipulation separation of control and data Gradual shift towards program-like representations: • Algorithmic State Machine (ASM) Notation • Hardware Description Languages (e.g., VHDL) © R.H. Katz Transparency No. 15-2 Contemporary Logic Design Finite State Machine Design Alternative State Machine Representations Algorithmic State Machine (ASM) Notation Three Primitive Elements: • State Box • Decision Box • Output Box State Machine in one state block per state time Single Entry Point Unambiguous Exit Path for each combination of inputs Outputs asserted high (.H) or low (.L); Immediate (I) or delayed til next clock State Entry Path State Code * State Name State Output Lis t T *** State Box Condition Condition Box Conditional Output Lis t F ASM Block Output Box Exits to other ASM Blocks © R.H. Katz Transparency No. 15-3 Contemporary Logic Design Finite State Machine Design Alternative State Machine Representations ASM Notation Condition Boxes: Ordering has no effect on final outcome Equivalent ASM charts: A exits to B on (I0 • I1) else exit to C A A 010 I0 T 010 F I1 T F I1 F F I0 T T B C B C © R.H. Katz Transparency No. 15-4 Alternative State Machine Representations Example: Odd Parity Checker Contemporary Logic Design Finite State Machine Design Input X, Output Z Even 0 Nothing in output list implies Z not asserted Z asserted in State Odd F X T Odd 1 H. Z F X T Trace paths to derive state transition tables © R.H. Katz Transparency No. 15-5 Contemporary Logic Design Finite State Machine Design Alternative State Machine Representations Symbolic State Table: Present Next Input State State Output F — Even Even T — Even Odd F A Odd Odd T A Odd Even A - asserted Encoded State Table: Present Next Input State State Output 0 0 0 0 1 0 0 1 0 1 1 1 1 1 1 0 © R.H. Katz Transparency No. 15-6 Contemporary Logic Design Finite State Machine Design Alternative State Machine Representations ASM Chart for Vending Machine 0¢ 00 10¢ T D 10 T D F F F F N N T 5¢ T 15¢ 01 11 H.Open T N F F D Reset F T T 0¢ © R.H. Katz Transparency No. 15-7 8.4 Moore and Mealy Machine Design Procedure Contemporary Logic Design Finite State Machine Design Definitions Mealy Machine Xi Inputs Zk Outputs Combinational Logic for Outputs and Next State State Register Clock Outputs depend on state AND inputs Input change causes an immediate output change State Feedback Asynchronous outputs State Register Xi Inputs Zk Outputs Clock state feedback Moore Machine Comb. Logic for Outputs Combinational Logic for Next State (Flip-flop Inputs) Outputs are function solely of the current state Outputs change synchronously with state changes © R.H. Katz Transparency No. 15-8 Contemporary Logic Design Finite State Machine Design Moore and Mealy Machines State Diagram Equivalents for Vending Machine FSM Moore Machine N D + R eset Reset (N D + Reset)/0 Reset/0 0¢ 0¢ Mealy Machine [0] Reset N Reset/0 N/ 0 5¢ N D 5¢ D [0] N D/0 D/ 0 N N/ 0 10¢ 10¢ D [0] N+D N D D/ 1 N D/0 N+D/ 1 15¢ 15¢ [1] Reset Reset/1 Outputs are associated with State Outputs are associated with Transitions © R.H. Katz Transparency No. 15-9 Contemporary Logic Design Finite State Machine Design Moore and Mealy Machines Ex. FSM asserts the single output whenever its input string has at least two 1’s in sequence. States vs. Transitions Mealy Moore 0 Same I/O behavior 0/0 0 0 [0] Different # of states 0 0 1 Equivalent ASM Charts 1/0 0/0 1 1 1/1 [0] 1 2 S0 00 S0 0 [1] F IN S1 01 T S2 IN MOORE IN Mealy Machine typically has fewer states than Moore Machine for same output sequence 1 F T 10 H.OUT F T S1 F IN F IN 1 H.OUT T MEALY © R.H. Katz Transparency No. 15-10 Contemporary Logic Design Finite State Machine Design Moore and Mealy Machines Timing Behavior of Moore Machines Ex. 1 -- Reverse engineer the Moore Machine X X \B J Q C KR Q F Fa A Input X Output Z State A, B Z=B \A \R eset Master-Slave J-K Flip Flops Clk X X \A J Q C KR Q F Fb Z \B \R eset Two Techniques for Reverse Engineering: • Ad Hoc: Try input combinations to derive transition table • Formal: Derive transition by analyzing the circuit © R.H. Katz Transparency No. 15-11 Contemporary Logic Design Finite State Machine Design Moore and Mealy Machines Ad Hoc Reverse Engineering Behavior in response to input sequence 1 0 1 0 1 0: 100 X Clk A B/Z \Reset Reset X=1 X=0 X=1 X=0 X=1 X=0 X=0 AB = 00 AB = 00 AB = 11 AB = 11 AB = 10 AB = 10 AB = 01 AB = 00 Partially Derived State Transition Table A B 0 0 0 1 1 0 1 1 Signal tracing is acceptable for small FSM, but becomes untraceble for more complex FSM. X 0 1 0 1 0 1 0 1 A+ ? 1 0 ? 1 0 1 1 B+ ? 1 0 ? 0 1 1 0 Z 0 0 1 1 0 0 1 1 © R.H. Katz Transparency No. 15-12 Moore and Mealy Machines Formal Reverse Engineering Contemporary Logic Design Finite State Machine Design Derive transition table from next state and output combinational functions presented to the flipflops! Ja = X Jb = X Ka = X • B Kb = X xor A Z=B FF excitation equations for J-K flipflop: Q+ = JQ’ + K’Q A+ = Ja • A + Ka • A = X • A + (X + B) • A B+ = Jb • B + Kb • B = X • B + (X • A + X • A) • B Next State K-Maps: A+ State 00, Input 0 -> State 00 State 01, Input 1 -> State 11 B+ © R.H. Katz Transparency No. 15-13 Contemporary Logic Design Moore and Mealy Machines Finite State Machine Design Complete ASM Chart for the Mystery Moore Machine 00 S0 11 S3 H. Z 0 1 X 0 X 1 S1 01 S2 10 H. Z 0 X 1 1 X 0 Note: All Outputs Associated With State Boxes No Separate Output Boxes — Intrinsic in Moore Machines © R.H. Katz Transparency No. 15-14 Moore and Mealy Machines Ex. 2 -- Reverse Engineering a Mealy Machine One D flip-flop and one master/slave J-K flip flop Contemporary Logic Design Finite State Machine Design Clk D Q DA C A \A X \A R \X Q J C K \Reset A X B Q R Q \B \Reset DA \X B B Z \X X A Input X, Output Z, State A, B State register consists of D FF and J-K FF © R.H. Katz Transparency No. 15-15 Contemporary Logic Design Finite State Machine Design Moore and Mealy Machine Ad Hoc Method Signal Trace of Input Sequence 101011: 100 Note glitches in Z! X Clk Outputs valid at following falling clock edge A B Z \Res et Reset AB=00 Z =0 X =1 AB=00 Z =0 X =0 AB=00 Z =0 X =1 AB=01 Z =0 X =0 AB=11 Z=1 A B 0 0 Partially completed state transition table based on the signal trace 0 1 1 0 1 1 X 0 1 0 1 0 1 0 1 X =1 AB=10 Z =1 A+ 0 0 ? 1 ? 0 1 ? X =1 AB=01 Z =0 B+ 1 0 ? 1 ? 1 0 ? Z 0 0 ? 0 ? 1 1 ? © R.H. Katz Transparency No. 15-16 Contemporary Logic Design Finite State Machine Design Moore and Mealy Machines Formal Method A+ = B • (A + X) = A • B + B • X B+ = Jb • B + Kb • B = (A xor X) • B + X • B =A•B•X + A•B•X + B•X Z =A•X + B•X A+ Missing Transitions and Outputs: State 01, Input 0 -> State 01, Output 1 State 10, Input 0 -> State 00, Output 0 State 11, Input 1 -> State 11, Output 1 B+ Z © R.H. Katz Transparency No. 15-17 Contemporary Logic Design Finite State Machine Design Moore and Mealy Machines ASM Chart for Mystery Mealy Machine S0 = 00, S1 = 01, S2 = 10, S3 = 11 S0 1 H. Z 00 10 S2 0 X 0 S1 X 1 H. Z S3 01 11 H. Z 0 X 1 1 X 0 NOTE: Some Outputs in Output Boxes as well as State Boxes This is intrinsic in Mealy Machine implementation © R.H. Katz Transparency No. 15-18 Contemporary Logic Design Finite State Machine Design Moore and Mealy Machines Synchronous Mealy Machine Breaks the direct connection between inputs and outputs by introducing storage elements. Prevents glitches as seen in Mealy Machine example. Clock Xi Inputs Zk Outputs Combinational Logic for Outputs and Next State State Register Output FFs Clock state feedback latched state AND outputs avoids glitchy outputs! © R.H. Katz Transparency No. 15-19 HW #15 -- Section 8.3 & 8.4 Contemporary Logic Design Finite State Machine Design © R.H. Katz Transparency No. 15-20