IMPACT_Litho_RT_SUM_..

advertisement

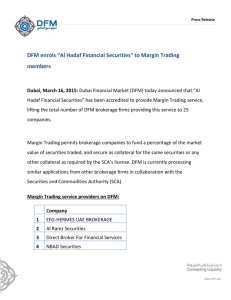

IMPACT Internal Document for

IMPACT Participants Only

Summary

IMPACT Roundtable

Lithography + DfM

Dialog on industry challenges and university

research activities among technologists from

Participating Companies, Students and Faculty

Held at SanDisk, Milpitas

September 24, 2008

For further dialog contact the IMPACT faculty:

Puneet Gupta, Andrew Kahng, Andy Neureuther,

Kameshwar Poolla, Costas Spanos

09/24/2008

University of

1

California • Berkeley • San Diego • Los Angeles

IMPACT UC Discovery Industry Team –

Thanks!

09/24/2008

University

of California • Berkeley

• San

IMPACT • Lithography/DfM

• Roundtable

2 Diego • Los

Roundtable Approach

Objective: guide research in the IMPACT program

understand litho & DfM challenges in industry

understand research capabilities in universities

what are issues that are relevant and timely to

industry and academic in nature

Format:

2 hours of presentations (8 industry, 5 faculty)

– Summarized by speaker suggestions

2 hours of dialog 45 participants (30 ind.15 univ.)

– Summarized by topics (DfM, Variability, Physics)

IMPACT • Lithography/DfM • Roundtable 3

09/24/2008

Speakers

Industry

University of California

Lars Liebmann, IBM, ASIC

Andrew Kahng, UCSD

Chandu Gorla, Flash Memory, San Disk

Vivek Singh, Microprocessors, Intel

Zhenhai Zhu, Double Patterning, Cadence

DfM tools

Puneet Gupta, UCLA

DfM tools

Huixiong Dai, thin-films for pattern transfer, Kameshwar Poolla, UCB

AMAT

Algorithms

Mamoru Miyawaki, Exposure tools, Canon Costas Spanos, UCB

variability and assignment

Bob Socha, Exposure tools, ASML

of causes

Stan Stokowski, Inspection, KLA-T

Andy Neureuther, UCB

fast-CAD, electrical test,

EM

IMPACT • Lithography/DfM • Roundtable 4

09/24/2008

Main Points

DfM is all about knowing how much performance to leave on the table

to make the IC manufacturable.

– DfM (or computational Lith., etc.) is expected to provide a full generation now

that lithography is no longer scaling.

– DfM is time-changing as DfM results acted on in the fab improve the process but

design requires models extrapolated to the future improvement at tapeout date.

DfM helps manage complexity

– Support playing what-if games at macro or product level

– Need to make tolerance consequences and budgets visible

– Scaling layouts to the next generation no longer works - requires design

Double patterning technology is nearly here for the 22nm node (logic

and flash) and 32nm node (memory) as a necessary reality.

–

–

–

–

–

The choice of DP method depends on product and tolerances including overlay

DP methods require rethinking layout concepts and metal layers in design

Thick mask EM effects must be mitigated

Need better models of all physical processes including 3D effects

Simulated assisted metrology is required

IMPACT • Lithography/DfM • Roundtable 5

09/24/2008

Lars Liebmann, IBM

Challenge: DfM needs to reflect the improvement of process with time.

Once actionable, modeled, systematic sources of variation are

found through statistical methods (of DfM) they may be corrected in

either Fab or Design.

What the designer wants is not a current but a future model of

process maturity at the tapeout date for their product.

Research Suggestions: (Some of these are detailed in later slides)

Process Variation Analysis, Decomposition, and Correlation

that would facilitate more focused process or layout optimization

More Rigorous Approximation to Mask EMF Effects including highNA and parallelized codes

Extension of fast first principle predictive modeling solutions to

etch, CMP, implant, anneal

Simulation Assisted Metrology for understanding inspection and

improving extraction of meaningful metrics

Mechanical Models for Long Range Stress Effects

IMPACT • Lithography/DfM • Roundtable 6

09/24/2008

Chandu Gorla, SanDisk

Challenge: In Flash memory generations are only 12 months apart

Immersion is in production, spacer pattern doubling is nearly

here, and EUV and Imprint are just around the corner

Suggestions:

Materials for double patterning: freeze or multiple exposure;

single layer double exposure

Overlay

Odd and even pattern dependence: understanding and

modeling the interaction between litho and etch

DfM needs to be flexible to include novel integration schemes

and their tolerances

EUV and Imprint need study

IMPACT • Lithography/DfM • Roundtable 7

09/24/2008

Vivek Singh, Intel

Comment: The following suggestions emphasize modeling and

algorithms. Topics that are theoretical are easy to transfer

quickly to industry.

Suggestions:

Recovering the lost 3rd dimension (resist thickness and mask

edge effects). Litho effects lost in the popularity of OPC with

only 2D effects

Mask scattering to include ‘thick-mask’ effects at advanced

nodes

Inverse Lithography that is fast and not too fragmented

Optimization algorithms that are fast for sizeable numbers of

discrete variables

Litho/Etch coupled models with innovation in fast formulations

for the complex physics of etch.

IMPACT • Lithography/DfM • Roundtable 8

09/24/2008

Zenhai Zhu, Cadence

Challenge: Splitting a layout for double patterning is not just a

tapeout problem

Scaling often requires going back into the design for contacts,

redundant vias, etc

Restricted Design Rules are often ridiculously restricting

Suggestions:

Automated netlist to physical layout

Single-contact process (Reliable litho, deposition,

electroplating of small holes)

IMPACT • Lithography/DfM • Roundtable 9

09/24/2008

Huixiong Dai, Applied

Challenge: Double patterning is the only feasible solution for 32nm HP

and beyond before 2012.

Meeting NAND Spec (+/-10%) for 32nm and 29nm Half-Pitch

26nm and 22nm is limited by resist LWR

Suggestions:

Sidewall Spacer Double Patterning with non-gridded Design

requires Design Evolution for Logic

Highly regular gridded designs are promising for 44 nm pitch but a

greater patterning concern is the isolated slots

Resist LWR is an industry wide challenge and it interplays with the

core and space tolerances

IMPACT • Lithography/DfM • Roundtable 10

09/24/2008

Mamoru Miyawaki, Canon

Challenge: Future nodes such as 22 nm require very careful

examination of techniques and tolerance budgets.

Suggestions:

Verification methodology to reproduce the actual experimental

data by DfM software. (How many parameters? Accuracy for

each?)

DFM provide a system for understand every aspect of the

whole process and error budgets

Methods for monitoring very low lens aberrations and assuring

that aberrations have virtually zero effect on lithography.

IMPACT • Lithography/DfM • Roundtable 11

09/24/2008

Bob Socha, ASML

Challenge: DPT for the 22nm node (logic) and 32nm node

(memory) is a necessary reality

Suggestions:

Overlay is critical in double patterning and in vertical scaling

(3D layout)

Illumination source and Mask Optimization needs to interact

with designers, fab, and scanner vendor

How can this interaction knowledge be included in the design

library and in the place and route CAD tools

IMPACT • Lithography/DfM • Roundtable 12

09/24/2008

Stan Stokowski, K-T

Challenge: It is not just a matter of seeing the variation but rather

how this information can be used to optimize all of the settings

Suggestions:

Understand IC process control on a broader basis and

determine what to measure and inspect for controlling the

process

Lithography simulation of mask 3D effects at the wafer

Identify issues in EUV in advance

Identify issues in Imprint in advance

IMPACT • Lithography/DfM • Roundtable 13

09/24/2008

DFM Wishlist Discussion 1 (Gupta, Kahng)

#1. Accurate, quick map from design rules to product quality (area, power, frequency,

yield, (COO)) (Rob Aitken, ARM)

–

–

need an infrastructure within which to play such what-if games at macro or product level (Lars

Liebmann)

Framed by SPICE/ITRS parameters, or TCAD, or process knobs?

– physical parameters (Lg) preferred to electrical (Vt) for informing process (Vivek Singh, Lars Liebmann)

#2. New ways for design to ease required process control capability (Zhilong Rao,

AMAT)

#3. Design flow integration of systematic variation models

–

Orthogonality of designs to systematic variations (related to above #1, #2)

–

But, aren’t big systematic issues solved in the fab? (Lars Liebmann)

–

Wafer-level systematic variation is less well-addressed than die/field-level where OPC, PPC have

had success (Costas Spanos)

– + Metrology to support

random variations increasing in significance (JL de Jong, Xilinx)

#4. Research on DPL ‘bimodal’ problem

–

–

Xilinx: already study mismatch; assume have to extend to DPL context

ASML / Socha: feel this is valuable work; make sure to cover overlay as well as CD

–

IBM (Lars): bimodal problem is unacceptable, and hence uninterested in this process if such a

problem exists(!) assume that this is controlled

Interconnects also of interest (Lars); ongoing at UCLA, UT, …

N.B.: even if distributions perfectly matched, still lose spatial correlation

Solving a single-layer formulation may be irrelevant ! (Apo, Cadence)

University solvers: transferability of code is of interest (IBM, ASML, ...)

–

–

–

–

– DPL flavor: bimodal distribution of space, vs. bimodal distribution of width

IMPACT • Lithography/DfM • Roundtable 14

09/24/2008

DFM Wish list Discussion 2 (Gupta, Kahng)

#5. Layout automation for fixed pitch / fixed orientation (JL de Jong, Xilinx)

–

–

–

–

#6. Miyawaki-san (Canon) comment: How do I determine my budget out of a

“DFM” tool?

–

–

–

–

May be beyond capabilities of university research? (Lars)

But, prototypes of new ideas possible? (Andy)

IMPACT can at least help industry make a decision

Cf. Rob Aitken wishlist #1

Issue today: electrical budgets not necessarily well-aligned to process budgets

Cf. LEE rule / taper shape / leakage-area correlation of metrics – UCLA/UCSD

Can you even establish yield impact of a litho hotspot? (Lars)

Can you tell me the exact yield impact of double-cut vs. single-cut vias? (Lars)

– (Berkeley work (Spanos, Poolla) is responsive to these types of questions...)

#7. (Huixiong Dai, AMAT) Have you looked at layout that is specifically

directed at spacer double-patterning?

– UCLA is starting to look at this a bit (e.g., M1 patterning) – maybe some insights within a

few months

General comments

– Time horizon?

– Tractability to students?

– Nature of application/specific research: artifactual, less generalizable or impactful than a

new framework or theory? (Vivek)

– Ultimately, DFM tools must become more integrated into overall process planning and

budgeting (Andy)

IMPACT • Lithography/DfM • Roundtable 15

09/24/2008

Metrology and Algorithms Wish list Discussion

3 (Poolla and Spanos)

#1 Uncertainty in Circuit Simulation

Is there a need to go beyond the 4 corner model of spread in performance? (Yes)

Is there a need to propagate uncertainty through models that are nonlinear (max)?

How are results of uncertainty characterization reinserted into design flow?

Does not matter as both design and process have limitations. This is

parametric loss

Understanding robustness to estimation errors.

#2 Accuracy of Circuit modeling

Are all the models under zero variability conditions that go into tool sufficiently

accurate to be predictive of circuit performance.

SPICE 15% to 20% (but derivative is more accurate.)

Voltage and temp may dominate corner speed estimates more than process

Designers might choose devices with low variability (fixed pitch price) this

needs to be included in Circuit simulation options in SPICE) Tool to help make

a decision before a layout exists. Interaction between design models and

layout and need to include and quantify other factors such as temp.

Corners assume convex hull but possibility that worst situation may be in the

middle (temp).

IMPACT • Lithography/DfM • Roundtable 16

09/24/2008

Metrology and Algorithms Wish list Discussion

4 (Poolla and Spanos)

#3 What is DfM?

DfM is all about how much you leave on the table to make it manufacturable and knowing

how much that is.

Looking for us to estimate the performance benefit of the best possible variation reduction.

(How much faster would the circuit run?)

Alternatively to modeling uncertainty DfM is about reducing variation and could use the 5

tools described.

If wavelength gap had not increase would we have had a need for DfM? How much is Litho

Today?

#4 DfM Scope

Does place and route use models? Real data driven used upstream in design?

Need layout checked afterward. Monte Carlo is slow is there sampling ways to speed it up.

#5 Roles for DfM

At 90 nm processes are well characterized yet full process aware design might result to the

improvement of a full generation.

The next generation plans to get the realizable speed extrapolation from the previous

generation but process discontinuities (metal or new foundry) require a new guess.

–

–

–

This is a challenge for data driven modeling.

A solution is to keep layout and recalibrate on 10% structures, group and see effects, and focus on possible

causes at length scale.

Apply machine learning to translate existing (SEMs) to changes in process

IMPACT • Lithography/DfM • Roundtable 17

09/24/2008

Litho Wish list Wish list Discussion 5 (Neureuther)

#1 Sources of Variation:

Methods for identifying variations due to illumination in addition to focus and dose

Masks: More Rigorous Approximation to EMF Effects

Overlay and propagation in 3D

Methods for aberration measurements and assurance of zero contribution to patterning

#2 Process Modeling

Extension of Process Modeling

{Litho 3D, Fast Image {ideas from other fields}, Etch, Anneal, CMP}

Mechanical Models for Long Range Stress Effects on wafer distortion

Simulation Assisted Metrology

–

–

CD SEM is uncaligbrated compared to artifact (10 nm uncertainty)

3rd Dimension is lost here as well

#3 Future

Process {equivalent of negative resist?}

Look ahead to understand issues in EUV and IMPRINT

3D Integration

–

–

–

–

Double patterning (reach through, CMP, resistance of contact both yield and circuit performance)

Some work on stacking but not being pursued yet

Fixed pitch small circuits study on how well work and how much leave on table (EDA Ind)

Need automatic tool to relate to 3D configuration (EDA ind)

IMPACT • Lithography/DfM • Roundtable 18

09/24/2008

Liebmann: Process Variation Analysis,

Decomposition, and Correlation

Given sets of empirical data taken across multiple lots, wafers,

chips, and field locations, collected after various process steps

(e..g. resist, etch, anneal) by various means (e.g. sem,

electrical) – establish frequency, process, and layout

correlations that would facilitate more focused process or

layout optimization.

The goal would be to develop an analysis and visualization

software platform that combines layout information, process

simulations over different length scales, and data analysis to

pinpoint error sources.

Detailed understanding of correlation distances may also

improve incremental layout optimization (e.g. cell-level, macrolevel, chip-level).

IMPACT • Lithography/DfM • Roundtable 19

09/24/2008

Liebmann: More Rigorous Approximation to EMF Effects

Need sufficiently accurate EMF calculations to

incorporate into iterative optimizations.

Accuracy of domain decomposition is being

questioned at ultra-high NA and extreme illumination

angles.

Code should focus on extreme parallelization,

potentially running on supercomputing systems

such as CCNI.

Also, need to make Tempest 7.0 available.

IMPACT • Lithography/DfM • Roundtable 20

09/24/2008

Liebmann: Extension of Process Modeling

Build fast first principle modeling solutions for

processes other than lithography (e.g. etch, cmp,

implant, anneal).

Models should be physical enough to allow accurate

predictive modeling.

IMPACT • Lithography/DfM • Roundtable 21

09/24/2008

Liebmann: Simulation Assisted Metrology

Build models to gain first principle understanding of

metrology image collection and data extraction to

improve accuracy against meaningful metrics (e.g.

top-width, bottom-width, sidewall angle).

IMPACT • Lithography/DfM • Roundtable 22

09/24/2008

IMPACT Lithography/DfM Roundtable

Thanks to All

Speakers

Technologists

Students

SanDisk

Changrui Yin

for preparing comments

for your comments and

interactions

for doing the hard work !

for hosting and Starleigh Arce

for local arrangements

for web site posting and

reservations

Reminder: IMPACT Workshop, Wed. October 29th at

the AMD Commons Building, Santa Clara

IMPACT • Lithography/DfM • Roundtable 23

09/24/2008