File - Engr.Zakir Shaikh

advertisement

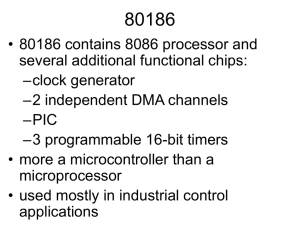

AX AH AL BX BH BL CX CH CL DX DH DL SP BP SI IP D E C O D E R Fetch & store code bytes in C O PIPELINE D E O U T PIPELINE (or) QUEUE C O D E I N CS DS ES SS IP BX DI DI SP BP SI DI FLAGS ALU Timing control Default Assignment The Architecture Of 8086 Includes: Arithematic Logic Unit (ALU) Flags General Registers Instruction Byte Queue Segment Registers 8086 Has Been Partitioned Into Two Functional Blocks: 1. Execution Unit (EU) 2. Bus Interface Unit (BIU) The Execution Unit (EU) Has: Conrtol Unit. Instruction Decoder. Arithematic And Logical Unit (ALU). General Registers. Flag Register. Pointers. Index Registers. Execution unit contains the complete infrastructure required to . execute an instruction. . EU is responsible for executing the instructions of the programs and to carry out the required processing. Control Unit Control unit is responsible for the co-ordination of all other units of the processor Instruction Decoder The instruction decoder translates the instructions fetched from the memory into a series of actions that are carried out by the EU Arithematic And Logical Unit (ALU) ALU performs various arithmetic and logical operations over the data General Registers General registers are used for temporary storage and manipulation of data and instructions General Registers Are: Accumulator Register Base Register Count Register Data Register Accumulator Register 16-bit register AX; 8-bit registers [AL+AH]. Accumulator can be used for I/O operations and string manipulation Base register 16-bit register BX; 8-bit registers [BL+BH]. BX register usually contains a data pointer used for based, based indexed or register indirect addressing. Count Register 16-bit register CX; 8-bit registers [CL+CH]. Count register can be used as a counter in string manipulation and shift/rotate instructions Data Register 16-bit register DX; 8-bit registers [DL+DH]. Data register can be used to hold 16 bit result in 32-bit operations. Flag Register (16-bit) A flag is a flip flop which indicates some conditions produced by the execution of an instruction or controls certain operations of the EU. 9 of the 16 are active flags and remaining 7 are undefined. Active Flags; 6 flags indicates some conditions- Status Flags 3 flags –Control Flags U U U U OF DF IF TF SF ZF Sign Over flow U - Unused Direction Interrupt Trap U AF U PF Auxiliary Zero U CF Carry Parity Carry Flag (CF) - set if there was a carry from or borrow to the most significant bit during last result calculation Parity Flag (PF) - set if parity (the number of "1" bits) in the low-order byte of the result is even. Auxiliary Carry Flag (AF) - set if there was a carry from or borrow to bits 0-3 in the AL register. Zero Flag (ZF) - set if the result is zero. Sign Flag (SF) - set if the most significant bit of the result is one Overflow Flag (OF) - set if the size of the exceeds the capacity of the destination location. Single-step Flag (Trap F) – put 8086 in the single step mode Interrupt-enable Flag (IF) - setting this bit enables maskable interrupts . When IF=0, all maskable interrupt are disable Direction Flag (DF) – It is used with string operations. When set , it causing string instructions to auto – decrement or to process strings from right to left. Pointers And Index Registers Keep offset addresses Used in various forms of memory addressing Stack Pointer (SP) is a 16-bit register pointing to program stack Base Pointer (BP) is a 16-bit register pointing to data in stack segment. BP register is usually used for based, based indexed or register indirect addressing. Source Index (SI) is a 16-bit register. SI is used for indexed, based indexed and register indirect addressing, as well as a source data addresses in string manipulation instructions. Destination Index (DI) is a 16-bit register. DI is used for indexed, based indexed and register indirect addressing, as well as a destination data addresses in string manipulation instructions. The Bus Interface Unit (BIU) Has: 6-byte Instruction Queue The Segment Registers The Instruction Pointer The Address Summing Block The BIU handles all transactions of data and addresses on the buses for EU. The BIU uses a mechanism known as an instruction stream queue to implement a Pipeline Architecture. The queue permits pre-fetch of up to 6 bytes of instruction code. EU reads the instruction byte from the queue. These pre-fetching instructions are held in its FIFO queue. A byte is loaded at the input end of the queue, it automatically shifts up through the FIFO to the empty location nearest the output. The EU accesses the queue from the output end. Physical Memory 00000 Code segment (64KB) To access memory outside of 64 KB the CPU uses special Segment Registers to specify where the 64 KB segments are positioned within 1 MB of memory. FFFFF Data segment (64KB) Extra segment (64KB) Stack segment (64KB) 1 MB The total addressable memory size is 1MB Most of the processor instructions use 16-bit pointers; the processor can effectively address only 64 KB of memory Code Segment (CS) Register contains initial address of code segment with processor instructions. The processor uses CS for all accesses to instructions. Data Segment (DS) Register contain address of current data segment with program data. By default, the processor assumes that all data referenced by General Registers (AX, BX, CX, DX) and Index Register (SI, DI) is located in the Data Segment . Extra Segment (ES) Register contains address of extra segment, usually with program data. By default, the processor assumes that the DI register references the ES in string manipulation instructions. Stack Segment (SS) Register contains address of stack segment with program stack. By default, the processor assumes that all data referenced by the Stack Pointer (SP) and Base Pointer (BP) registers is located in the Stack Segment. Instruction Pointer contains 16-bit offset address of next instruction The value of the instruction pointer is incremented after executing every instruction. To form a 20bit address of the next instruction, the 16 bit address of the IP is added to the address contained in the CS , which has been shifted four bits to the left and this is done by the Summing Block. AD0-AD15 (Bidirectional) Address/Data bus Low order address bus; these are multiplexed with data. When AD lines are used to transmit memory address the symbol A is used instead of AD, for example A0-A15. When data are transmitted over AD lines the symbol D is used in place of AD, for example D0-D7, D8-D15 or D0- D15. A16/S3, A17/S4, A18/S5, A19/S6 Address/status High order address bus. These are multiplexed with status signals. When AS lines are used to transmit memory address the symbol A is used instead of As, for example A16-A19. S lines are indicating status signals. S3 and S4 indicates which segment register is being used. S5 updates interrupt enable flag at start of each cycle. S6 is always low. BHE (Active Low)/S7 (Output) Bus High Enable/Status It is used to enable data onto the most significant half of data bus, D8-D15. 8-bit device connected to upper half of the data bus use BHE (Active Low) signal. It is multiplexed with status signal S7. MN/ MX MINIMUM / MAXIMUM This pin signal indicates what mode the processor is to operate in. RD (Read) (Active Low) The signal is used for read operation. It is an output signal. It is active when low. Test Test input is tested by the ‘wait’ instruction. 8086 will enter a wait state after execution of the wait instruction and will resume execution only when the test is made low by an active hardware. This is used to synchronize an external activity to the processor internal operation READY This is the acknowledgement from the slow device or memory that they have completed the data transfer. The signal made available by the devices is synchronized by the 8284A clock generator to provide ready input to the 8086. The signal is active high. RESET (Input) Causes the processor to immediately terminate its present activity. The signal must be active HIGH for at least four clock cycles. CLK The clock input provides the basic timing for processor operation and bus control activity. Its an asymmetric square wave with 33% duty cycle. INTR [Interrupt Request] This is a triggered input. This is sampled during the last clock cycles of each instruction to determine the availability of the request. If any interrupt request is pending, the processor enters the interrupt acknowledge cycle. This signal is active high and internally synchronized. Hold Input signal to the processor from the bus masters as a request to grant the control of bus. Usually used by dma controller to get the control of the bus. Hlda Hold acknowledge Acknowledge signal by the processor to the bus master requesting the control of the bus through hold. The acknowledge is asserted high, when the processor accepts hold. Rq/gt0 and rq /gt1 bus request/ bus grant These requests are used by other local bus masters to force the processor to release the local bus at the end of the processor’s current bus cycle. These pins are bidirectional. The request gt0 will have higher priority than gt1. Wr Write control signal; asserted low whenever processor writes data to memory or i/o port. Lock an output signal activated by the lock prefix instruction. Remains active until the completion of the instruction prefixed by lock. The 8086 output low on the lock pin while executing an instruction prefixed by lock to prevent other bus masters from gaining control of the system bus. m/io Used to differentiate memory access and i/o access. For memory reference instructions, it is high. For in and out instructions, it is low. Dt/r Data transmit/receive Output signal from the processor to control the direction of data flow through the data transceivers. Den Data enable Output signal from the processor used as output enable for the transceivers. S0, s1, s2 Status signals Used by the 8086 bus controller to generate bus timing and control signals. Ale Address latch enable Used to demultiplex the address and data lines using external latches. Inta Interrupt acknowledge When the interrupt request is accepted by the processor, the output is low on this line. NMI NON-MASKABLE INTERRUPT: an edge triggered input which causes an interrupt request to the processor. A subroutine is vectored to via an interrupt vector lookup table located in system memory. NMI is not maskable internally by software. Qs0, qs1 Queue status The processor provides the status of queue in these lines. The queue status can be used by external device to track the internal status of the queue in 8086. The set of mechanisms by which an instruction can specify how to obtain its operands is known as Addressing Modes. Addressing Modes In 8086: 1. Register Addressing 2. Immediate Addressing 3. Direct Addressing 4. Register Indirect Addressing 5. Based Relative Addressing 6. Indexed Relative Addressing 7. Based Indexed Relative Addressing Register Addressing Mode The operand to be accessed is specified as residing in an internal register. Example: MOV AX , BX Immediate Addressing Mode The operand is part of the instruction instead of the contents of a register or memory. Example: MOV AL , 015H Direct Addressing Mode The operand is the combination of effective address and data segment register. It gives the physical address of the operand. Example: MOV CX , BETA Register Indirect Addressing Mode The operand is the combination of effective address and data segment register. The offset is specified, as effective address resides either in pointer register or index register. Example: MOV AX , [SI] Based Addressing Mode The operand is the addition of direct or indirect displacement of contents of either Base Register or Base Pointer Register and value in DS and SS respectively. Example: MOV [BX] . BETA , AL Indexed Addressing Mode The operand is the addition of direct or indirect displacement of contents of Index Registers. Example MOV AL , ARRAY [SI] Based Indexed Addressing Mode Combination of based addressing mode and the indexed addressing mode. Example: MOV AH , [BX] . BETA [SI] The entire group of instructions that a microprocessor supports is called Instruction Set. 8086 has more than 20,000 instructions. Data Transfer Instructions Arithematic Instructions Bit Manipulation Instructions Program Execution Transfer Instructions String Instructions Process Control Instructions MOV Des, Src: Source operand can be register, memory location or immediate operand. Destination can be register or memory operand. Both Source and Destination cannot be memory location at the same time. Example: MOV CX, 037A H MOV AL, BL MOV BX, [0301 H] PUSH Operand: It pushes the operand into top of stack. Example: PUSH BX POP Destination: It pops the operand from top of stack to Destination. Destination can be a general purpose register, segment register (except CS) or memory location. Example: POP AX XCHG Des, Src: This instruction exchanges Source with Destination. It cannot exchange two memory locations directly. Example: XCHG DX, AX IN Accumulator, Port Address: It transfers the operand from specified port to accumulator register. Example: IN AX, 0028 H OUT Port Address, Accumulator: It transfers the operand from accumulator to specified port. Example: OUT 0028 H, AX LEA Register, Src: It loads a 16-bit register with the offset address of the data specified by the Source. Example: LEA BX, [DI] LDS Des, Src: It loads 32-bit pointer from memory source to destination register and DS. The offset is placed in the destination register and the segment is placed in DS. To use this instruction the word at the lower memory address must contain the offset and the word at the higher address must contain the segment. Example: LDS BX, [0301 H] LES Des, Src: It loads 32-bit pointer from memory source to destination register and ES. The offset is placed in the destination register and the segment is placed in ES. This instruction is very similar to LDS except that it initializes ES instead of DS. Example: LES BX, [0301 H] LAHF: It copies the lower byte of flag register to AH. SAHF: It copies the contents of AH to lower byte of flag register PUSHF: Pushes flag register to top of stack. POPF: Pops the stack top to flag register. ADD Des, Src: It adds a byte to byte or a word to word. It effects AF, CF, OF, PF, SF, ZF flags. Example: ADD AL, 74H ADD DX, AX ADD AX, [BX] ADC Des, Src: It adds the two operands with CF. It effects AF, CF, OF, PF, SF, ZF flags. Example: ADC AL, 74H ADC DX, AX ADC AX, [BX] SUB Des, Src: It subtracts a byte from byte or a word from word. It effects AF, CF, OF, PF, SF, ZF flags. For subtraction, CF acts as borrow flag. Example: SUB AL, 74H SUB DX, AX SUB AX, [BX] SBB Des, Src: It subtracts the two operands and also the borrow from the result. It effects AF, CF, OF, PF, SF, ZF flags. Example: SBB AL, 74H SBB DX, AX SBB AX, [BX] INC Src: It increments the byte or word by one. The operand can be a register or memory location. It effects AF, OF, PF, SF, ZF flags. CF is not effected. Example: INC AX DEC Src: It decrements the byte or word by one. The operand can be a register or memory location. It effects AF, OF, PF, SF, ZF flags. CF is not effected. Example: DEC AX NEG Src: It creates 2’s complement of a given number. That means, it changes the sign of a number. CMP Des, Src: It compares two specified bytes or words. The comparison is done simply by internally subtracting the source from destination. The value of source and destination does not change, but the flags are modified to indicate the result. MUL Src: It is an unsigned multiplication instruction. It multiplies two bytes to produce a word or two words to produce a double word. AX = AL * Src DX : AX = AX * Src This instruction assumes one of the operand in AL or AX. Source can be a register or memory location. IMUL Src: It is a signed multiplication instruction. DIV Src: It is an unsigned division instruction. It divides word by byte or double word by word. The operand is stored in AX, divisor is Source and the result is stored as: AH = remainder AL = quotient IDIV Src: It is a signed division instruction. CBW (Convert Byte to Word): This instruction converts byte in AL to word in AX. The conversion is done by extending the sign bit of AL throughout AH. CWD (Convert Word to Double Word): This instruction converts word in AX to double word in DX : AX. The conversion is done by extending the sign bit of AX throughout DX. NOT Src: It complements each bit of Source to produce 1’s complement of the specified operand. The operand can be a register or memory location. AND Des, Src: It performs AND operation of Destination and Source. CF and OF become zero after the operation. PF, SF and ZF are updated. OR Des, Src: It performs OR operation of Destination and Source. CF and OF become zero after the operation. PF, SF and ZF are updated. XOR Des, Src: It performs XOR operation of Destination and Source. CF and OF become zero after the operation. PF, SF and ZF are updated. SHL Des, Count: It shift bits of byte or word left, by count. It puts zero(s) in LSBs. MSB is shifted into carry flag. If the number of bits desired to be shifted is 1, then the immediate number 1 can be written in Count. However, if the number of bits to be shifted is more than 1, then the count is put in CL register. SHR Des, Count: It shift bits of byte or word right, by count. It puts zero(s) in MSBs. LSB is shifted into carry flag. If the number of bits desired to be shifted is 1, then the immediate number 1 can be written in Count. However, if the number of bits to be shifted is more than 1, then the count is put in CL register. ROL Des, Count: It rotates bits of byte or word left, by count. MSB is transferred to LSB and also to CF. If the number of bits desired to be shifted is 1, then the immediate number 1 can be written in Count. However, if the number of bits to be shifted is more than 1, then the count is put in CL register. ROR Des, Count: It rotates bits of byte or word right, by count. LSB is transferred to MSB and also to CF. If the number of bits desired to be shifted is 1, then the immediate number 1 can be written in Count. However, if the number of bits to be shifted is more than 1, then the count is put in CL register. CALL Des: This instruction is used to call a subroutine or function or procedure. The address of next instruction after CALL is saved onto stack. RET: It returns the control from procedure to calling program. Every CALL instruction should have a RET. JMP Des: This instruction is used for unconditional jump from one place to another. Jxx Des (Conditional Jump): All the conditional jumps follow some conditional statements or any instruction that affects the flag. Mnemonic Meaning Jump Condition JA Jump if Above CF = 0 and ZF = 0 JAE Jump if Above or Equal CF = 0 JB Jump if Below CF = 1 JBE Jump if Below or Equal CF = 1 or ZF = 1 JC Jump if Carry CF = 1 JE Jump if Equal ZF = 1 JNC Jump if Not Carry CF = 0 JNE Jump if Not Equal ZF = 0 JNZ Jump if Not Zero ZF = 0 JPE Jump if Parity Even PF = 1 JPO Jump if Parity Odd PF = 0 JZ Jump if Zero ZF = 1 Loop Des: This is a looping instruction. The number of times looping is required is placed in the CX register. With each iteration, the contents of CX are decremented. ZF is checked whether to loop again or not. CMPS Des, Src: It compares the string bytes or words. SCAS String: It scans a string. It compares the String with byte in AL or with word in AX. MOVS / MOVSB / MOVSW: It causes moving of byte or word from one string to another. In this instruction, the source string is in Data Segment and destination string is in Extra Segment. SI and DI store the offset values for source and destination index. REP (Repeat): This is an instruction prefix. It causes the repetition of the instruction until CX becomes zero. Example: REP MOVSB STR1, STR2 It copies byte by byte contents. STC: It sets the carry flag to 1. CLC: It clears the carry flag to 0. CMC: It complements the carry flag. STD: It sets the direction flag to 1. If it is set, string bytes are accessed from higher memory address to lower memory address. CLD: It clears the direction flag to 0. If it is reset, the string bytes are accessed from lower memory address to higher memory address. Be thankful for what you have; you’ll end up having more. If you concentrate on what you don’t have, you will never, ever have enough. OprahWinfrey