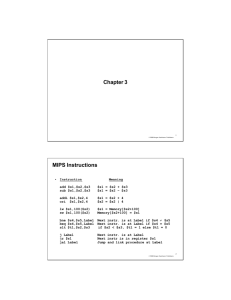

Instructions

advertisement

Chapter 2

Instructions: Language of the Computer

2004 Morgan Kaufmann Publishers

1

2004 Morgan Kaufmann Publishers

2

Outline

•

•

•

•

•

•

•

•

•

•

•

•

2.1 Introduction

2.2 Operations of the Computer Hardware

2.3 Operands of the Computer Hardware

2.4 Representing Instructions in the Computer

2.5 Logical Operations

2.6 Instructions for Making Decisions

2.7 Supporting Procedures in Computer Hardware

2.8 Communicating with People

2.9 MIPS Addressing for 32-Bits Immediates and Addresses

2.10 Translating and Starting a Program

2.16 Real Stuff: IA-32 Instructions

Summary

2004 Morgan Kaufmann Publishers

3

2.1 Introduction

2004 Morgan Kaufmann Publishers

4

Four design principles guide

•

•

•

•

Simplicity favors regularity

Smaller is faster

Make the common case fast

Good design demands good

compromises

2004 Morgan Kaufmann Publishers

5

Instructions:

•

•

Language of the Machine

We’ll be working with the MIPS instruction set architecture

– similar to other architectures developed since the 1980's

– Almost 100 million MIPS processors manufactured in 2002

– used by NEC, Nintendo, Cisco, Silicon Graphics, Sony, …

1400

1200

Other

SPARC

Hitachi SH

1100

PowerPC

1300

1000

Motorola 68K

900

MIPS

IA-32

800

ARM

700

600

500

400

300

200

100

0

1998

1999

2000

2001

2002

2004 Morgan Kaufmann Publishers

6

Instruction set: The vocabulary of

commands understood by a given

architecture.

Stored-Program Concept : The idea that

instructions and data of many types can be

stored in memory as numbers, leading to

the stored program computer.

2004 Morgan Kaufmann Publishers

7

2.2 Operations of the Computer Hardware

2004 Morgan Kaufmann Publishers

8

MIPS arithmetic

•

•

All instructions have 3 operands

Operand order is fixed (destination first)

Example:

C code:

a = b + c

MIPS ‘code’:

add a, b, c

(we’ll talk about registers in a bit)

“The natural number of operands for an operation like addition is

three…requiring every instruction to have exactly three operands, no

more and no less, conforms to the philosophy of keeping the

hardware simple”

2004 Morgan Kaufmann Publishers

9

Four design principles guide

•

•

•

•

Simplicity favors regularity

Smaller is faster

Make the common case fast

Good design demands good

compromises

2004 Morgan Kaufmann Publishers

10

FIGURE 2.1 MIPS architecture revealed in section 2.2.

MIPS assembly language

Category

Instruction

Example

Meaning

Comments

Arithmetic

add

add a, b, c

a=b+c

Always three operands

subtract

sub a, b, c

a=b-c

Always three operands

2004 Morgan Kaufmann Publishers

11

f = (g+h) - (i+j);

add t0, g, h

add t1, I, j

sub f, t0, t1

2004 Morgan Kaufmann Publishers

12

MIPS arithmetic

•

•

Design Principle: simplicity favors regularity.

Of course this complicates some things...

C code:

a = b + c + d;

MIPS code:

add a, b, c

add a, a, d

•

•

Operands must be registers, only 32 registers provided

Each register contains 32 bits

•

Design Principle: smaller is faster.

Why?

2004 Morgan Kaufmann Publishers

13

f = (g+h) - (i+j);

$s0, $s1, $s2, $s3, $s4

add t0, $s1, $s2

add t1, $s3, $s4

sub $s0, t0, t1

2004 Morgan Kaufmann Publishers

14

2.3 Operands of the Computer Hardware

2004 Morgan Kaufmann Publishers

15

Data transfer instruction: a command

that moves data between memory and

registers.

Address: A value used to delineate the

location of a specific data element

within a memory arry.

Alignment restriction : A requirement

that data be aligned in memory on

natural boundaries.

2004 Morgan Kaufmann Publishers

16

Registers vs. Memory

•

•

•

Arithmetic instructions operands must be registers,

— only 32 registers provided

Compiler associates variables with registers

What about programs with lots of variables

Control

Input

Memory

Datapath

Processor

Output

I/O

2004 Morgan Kaufmann Publishers

17

Four design principles guide

•

•

•

•

Simplicity favors regularity

Smaller is faster

Make the common case fast

Good design demands good

compromises

2004 Morgan Kaufmann Publishers

18

Memory Organization

•

•

•

Viewed as a large, single-dimension array, with an address.

A memory address is an index into the array

"Byte addressing" means that the index points to a byte of memory.

0

1

2

3

4

5

6

...

8 bits of data

8 bits of data

8 bits of data

8 bits of data

8 bits of data

8 bits of data

8 bits of data

2004 Morgan Kaufmann Publishers

19

Memory Organization

•

•

•

•

•

Bytes are nice, but most data items use larger "words"

For MIPS, a word is 32 bits or 4 bytes.

0 32 bits of data

4 32 bits of data

Registers hold 32 bits of data

32

bits

of

data

8

12 32 bits of data

...

232 bytes with byte addresses from 0 to 232-1

230 words with byte addresses 0, 4, 8, ... 232-4

Words are aligned

i.e., what are the least 2 significant bits of a word address?

2004 Morgan Kaufmann Publishers

20

FIGURE 2.2 Memory addresses and contents of

memory at those locations.

2004 Morgan Kaufmann Publishers

21

FIGURE 2.3 Actual MIPS memory addresses and

contents of memory for those words.

2004 Morgan Kaufmann Publishers

22

g = h + A[8]

lw $t0, 8($s3)

add $s1, $s2, $t0

2004 Morgan Kaufmann Publishers

23

Instructions

•

•

•

•

•

Load and store instructions

Example:

C code:

A[12] = h + A[8];

MIPS code:

lw $t0, 32($s3)

add $t0, $s2, $t0

sw $t0, 48($s3)

Can refer to registers by name (e.g., $s2, $t2) instead of number

Store word has destination last

Remember arithmetic operands are registers, not memory!

Can’t write:

add 48($s3), $s2, 32($s3)

2004 Morgan Kaufmann Publishers

24

Our First Example

•

Can we figure out the code?

swap(int v[], int k);

{ int temp;

temp = v[k]

v[k] = v[k+1];

v[k+1] = temp;

swap:

}

muli $2, $5, 4

add $2, $4, $2

lw $15, 0($2)

lw $16, 4($2)

sw $16, 0($2)

sw $15, 4($2)

jr $31

2004 Morgan Kaufmann Publishers

25

So far we’ve learned:

•

MIPS

— loading words but addressing bytes

— arithmetic on registers only

•

Instruction

Meaning

add $s1, $s2, $s3

sub $s1, $s2, $s3

lw $s1, 100($s2)

sw $s1, 100($s2)

$s1 = $s2 + $s3

$s1 = $s2 – $s3

$s1 = Memory[$s2+100]

Memory[$s2+100] = $s1

2004 Morgan Kaufmann Publishers

26

addi $s3, $s4, 4

# $s3 = $s3 +4

2004 Morgan Kaufmann Publishers

27

Four design principles guide

•

•

•

•

Simplicity favors regularity

Smaller is faster

Make the common case fast

Good design demands good

compromises

2004 Morgan Kaufmann Publishers

28

FIGURE 2.4 MIPS architecture revealed through

section 2.3.

MIPS operands

Name

32 registers

230memory

words

Example

Comments

$s0, $s1, ……

Fast locations for data. In MIPS, data must be in registers to perform arithmetic.

$t 0, $t 1, ……

Memory[0],

Accessed only by data transfer instructions in MIPS. MIPS uses byte addresses, so

Memory[4], …,

sequential word addresses differ by 4. Memory holds data structures arrays, and

Memory[4294967292]

spilled registers.

MIPS assembly language

Category

Arithmetic

Instruction

Example

Meaning

Comments

add

add $s1, $s2, $s3

$s1 = $s2 + $s3

Three operands; data in registers

subtract

sub $s1, $s2, $s3

$s1 = $s2 - $s3

Three operands; data in registers

add immediate

addi $s1, $s2, 100

$s1 = $s2 + 100

Used to add constants

load word

lw $s1, 100($s2)

$s1 = Memory [$s2 + 100]

Data from memory to register

store word

sw $s1, 100 ($s2)

Memory [$s2 + 100] = $s1

Data from register to memory

Data transfer

2004 Morgan Kaufmann Publishers

29

2.4 Representing Instructions in the

Computer

2004 Morgan Kaufmann Publishers

30

Binary digit Also called binary bit. One of

the two numbers in base 2, 0 or 1, that are

the components of information.

Machine language: Binary representation

used for communication within a computer

system.

Instruction format: A form of representation

of an instruction composed of fields of

binary numbers.

2004 Morgan Kaufmann Publishers

31

Machine Language

•

Instructions, like registers and words of data, are also 32 bits long

– Example: add $t1, $s1, $s2

– registers have numbers, $t1=9, $s1=17, $s2=18

•

Instruction Format:

000000 10001

op

•

rs

10010

rt

01000

rd

00000

100000

shamt

funct

Can you guess what the field names stand for?

2004 Morgan Kaufmann Publishers

32

Machine Language

•

•

•

•

Consider the load-word and store-word instructions,

– What would the regularity principle have us do?

– New principle: Good design demands a compromise

Introduce a new type of instruction format

– I-type for data transfer instructions

– other format was R-type for register

Example: lw $t0, 32($s2)

35

18

9

op

rs

rt

32

16 bit number

Where's the compromise?

2004 Morgan Kaufmann Publishers

33

op: Opcode

rs: the first register source operand.

rt: the second register source operand.

rd: the destination operand.

shamt: Shift amount.

funct: Function (function code).

2004 Morgan Kaufmann Publishers

34

Four design principles guide

•

•

•

•

Simplicity favors regularity

Smaller is faster

Make the common case fast

Good design demands good

compromises

2004 Morgan Kaufmann Publishers

35

Stored Program Concept

•

•

Instructions are bits

Programs are stored in memory

— to be read or written just like data

Processor

•

Memory

memory for data, programs,

compilers, editors, etc.

Fetch & Execute Cycle

– Instructions are fetched and put into a special register

– Bits in the register "control" the subsequent actions

– Fetch the “next” instruction and continue

2004 Morgan Kaufmann Publishers

36

Control

•

Decision making instructions

– alter the control flow,

– i.e., change the "next" instruction to be executed

•

MIPS conditional branch instructions:

bne $t0, $t1, Label

beq $t0, $t1, Label

•

Example:

if (i==j) h = i + j;

bne $s0, $s1, Label

add $s3, $s0, $s1

Label: ....

2004 Morgan Kaufmann Publishers

37

Control

•

MIPS unconditional branch instructions:

j label

•

Example:

if (i!=j)

h=i+j;

else

h=i-j;

•

beq $s4, $s5, Lab1

add $s3, $s4, $s5

j Lab2

Lab1: sub $s3, $s4, $s5

Lab2: ...

Can you build a simple for loop?

2004 Morgan Kaufmann Publishers

38

So far:

•

•

Instruction

Meaning

add $s1,$s2,$s3

sub $s1,$s2,$s3

lw $s1,100($s2)

sw $s1,100($s2)

bne $s4,$s5,L

beq $s4,$s5,L

j Label

$s1 = $s2 + $s3

$s1 = $s2 – $s3

$s1 = Memory[$s2+100]

Memory[$s2+100] = $s1

Next instr. is at Label if $s4 ≠ $s5

Next instr. is at Label if $s4 = $s5

Next instr. is at Label

Formats:

R

op

rs

rt

rd

I

op

rs

rt

16 bit address

J

op

shamt

funct

26 bit address

2004 Morgan Kaufmann Publishers

39

FIGURE 2.7 MIPS architecture revealed through

section 2.4

MIPS operands

Name

32 registers

230memory

words

Example

Comments

$s0, $s1, …, $s7

Fast locations for data. In MIPS, data must be in registers to perform arithmetic.

$t 0, $t 1, …, $t 7

Registers $s0 - $s7 map to 16-23 and $t0 - $t7 map to 8-15.

Memory[0],

Accessed only by data transfer instructions in MIPS. MIPS uses byte addresses, so

Memory[4], …,

sequential word addresses differ by 4. Memory holds data structures arrays, and

Memory[4294967292]

spilled registers.

MIPS assembly language

Category

Arithmetic

Instruction

Example

Meaning

Comments

add

add $s1, $s2, $s3

$s1 = $s2 + $s3

Three operands; data in registers

subtract

sub $s1, $s2, $s3

$s1 = $s2 - $s3

Three operands; data in registers

load word

lw $s1, 100($s2)

$s1 = Memory [$s2 + 100]

Data from memory to register

store word

sw $s1, 100 ($s2)

Memory [$s2 + 100] = $s1

Data from register to memory

Data transfer

2004 Morgan Kaufmann Publishers

40

FIGURE 2.7 MIPS architecture revealed through

section 2.4

MIPS machine language

Name

Format

Example

Comments

add

R

0

18

19

17

0

32

add $s1, $s2, $s3

sub

R

0

18

19

17

0

34

sub $s1, $s2, $s3

addi

I

8

18

17

100

addi $s1, $s2, 100

lw

I

35

18

17

100

lw $s1, 100($s2)

sw

I

43

18

17

100

sw $s1, 100 ($s2)

6 bits

5 bits

5 bits

5 bits

5 bits

6 bits

ALL MIPS instructions 32 bits

rd

shamt

funct

Arithmetic instruction format

Field size

R-format

R

op

rs

rt

I-format

I

op

rs

rt

address

Data transfer format

2004 Morgan Kaufmann Publishers

41

FIGURE 2.8 The stored-program concept.

2004 Morgan Kaufmann Publishers

42

Control Flow

•

•

We have: beq, bne, what about Branch-if-less-than?

New instruction:

if $s1 < $s2 then

$t0 = 1

slt $t0, $s1, $s2

else

$t0 = 0

•

Can use this instruction to build "blt $s1, $s2, Label"

— can now build general control structures

Note that the assembler needs a register to do this,

— there are policy of use conventions for registers

•

2004 Morgan Kaufmann Publishers

43

2.5

Logical Operations

2004 Morgan Kaufmann Publishers

44

FIGURE 2.9 C and JAVA logical operators and their

corresponding MIPS instructions.

Logical operations

C operators

JAVA operators

MIPS instructions

Shift left

<<

<<

sll

Shift right

>>

>>>

srl

Bit-by-bit AND

&

&

and, andi

Bit-by-bit OR

|

|

or, ori

Bit-by-bit NOT

~

~

nor

2004 Morgan Kaufmann Publishers

45

FIGURE 2.10 MIPS architecture revealed thus far.

MIPS operands

Name

Example

Comments

32 registers

$s0, $s1, …, $s7

$t 0, $t 1, …, $t 7

Fast locations for data. In MIPS, data must be in registers to perform arithmetic.

Registers $s0 - $s7 map to 16-23 and $t0 - $t7 map to 8-15.

Memory[0],

Memory[4], …,

Memory[4294967292]

Accessed only by data transfer instructions in MIPS. MIPS uses byte addresses, so

sequential word addresses differ by 4. Memory holds data structures arrays, and

spilled registers.

230memory

words

2004 Morgan Kaufmann Publishers

46

MIPS assembly language

Category

Arithmetic

Logical

Data

transfer

Instruction

Example

Meaning

Comments

add

add $s1, $s2, $s3

$s1 = $s2 + $s3

Three operands; Overflow detected

subtract

sub $s1, $s2, $s3

$s1 = $s2 - $s3

Three operands; Overflow detected

add immediate

addi $s1, $s2, 100

$s1 = $s2 + 100

+constant; overflow detected

and

add $s1, $s2, $s3

$s1 = $s2 & $s3

Three reg. operands; bit-by-bit AND

or

or

$s1, $s2, $s3

$s1 = $s2 | $s3

Three reg. operands; bit-by-bit OR

nor

nor

$s1, $s2, $s3

$s1 = ~($s2 | $s3)

Three reg. operands; bit-by-bit NOR

and immediate

andi $s1, $s2, 100

$s1 = $s2 & 100

Bit-by-bit AND reg with constant

or immediate

ori

$s1, $s2, 100

$s1 = $s2 | 100

Bit-by-bit OR reg with constant

shift left logical

sll

$s1, $s2, 10

$s1 = $s2 << 10

Shift left by constant

shift right

logical

srl

$$s1, $s2, 10

$s1 = $s2 >> 10

Shift right by constant

load word

lw

$s1, 100($s2)

$s1 = Memory [$s2 + 100]

Word from memory to register

store word

sw

$s1, 100 ($s2)

Memory [$s2 + 100] = $s1

Word from register to memory

2004 Morgan Kaufmann Publishers

47

2.6 Instructions for Making Decisions

2004 Morgan Kaufmann Publishers

48

Conditional branch: An Instruction that

requires the comparison of two values and

that allows for a subsequent transfer of

control to a new address in the program

based on the outcome of the comparison.

Basic block: A sequence of instructions

without branches and without branch

targets or branch labels.

Jump address table also called jump table.

A table of addresses of alternative

instruction sequences.

2004 Morgan Kaufmann Publishers

49

FIGURE 2.11 Illustration of the options in the IF

statement above.

2004 Morgan Kaufmann Publishers

50

Compiling if-then-else into Conditional Branches

if (i==j) f=g+h; else f=g-h;

bne $s3, $s4, Else

add $s0, $s1, $s2

j Exit

Else: sub $s0, $s1, $s2

Exit:

2004 Morgan Kaufmann Publishers

51

Compiling a while loop in C

while (save[i]==k)

i+=1;

Loop: sll $t1, $s3,2

add $t1, $t1, $s6

lw $t0, 0($t1)

bne $t0, $s5, Exit

add $s3, $s3, 1

j Loop

Exit:

2004 Morgan Kaufmann Publishers

52

The MIPS instruction is called set on less than

slt $t0, $s3, $s4

means that register $t0 is set to 1 if the

value in register $s3 is less than the value

in register $s4; otherwise, register $t0 is set

to o.

slti $t0, $s2, 10

2004 Morgan Kaufmann Publishers

53

FIGURE 2.12 MIPS architecture revealed through

section 2.6

MIPS operands

Name

Example

Comments

32 registers

$s0, $s1, …, $s7

$t 0, $t 1, …, $t 7

$zero

Fast locations for data. In MIPS, data must be in registers to perform arithmetic.

Registers $s0 - $s7 map to 16-23 and $t0 - $t7 map to 8-15. MIPS register $zero

always equals 0.

Memory[0],

Memory[4], …,

Memory[4294967292]

Accessed only by data transfer instructions in MIPS. MIPS uses byte addresses, so

sequential word addresses differ by 4. Memory holds data structures arrays, and

spilled registers.

230memory

words

2004 Morgan Kaufmann Publishers

54

FIGURE 2.13 MIPS machine language revealed

through section 2.6.

MIPS machine language

Name

Format

Example

Comments

add

R

0

18

19

17

0

32

add $s1, $s2, $s3

sub

R

0

18

19

17

0

34

sub $s1, $s2, $s3

lw

I

35

18

17

100

lw

$s1, 100($s2)

sw

I

43

18

17

100

sw

$s1, 100 ($s2)

and

R

0

18

19

17

0

36

and $s1, $s2, $s3

or

R

0

18

19

17

0

37

or

$s1, $s2, $s3

nor

R

0

18

19

17

0

39

nor

$s1, $s2, $s3

andi

I

12

18

17

100

andi $s1, $s2, 100

ori

I

13

18

17

100

ori

$s1, $s2, 100

sll

R

0

0

18

17

10

0

sll

$s1, $s2, 10

srl

R

0

0

18

17

10

2

srl

$s1, $s2, 10

beq

I

4

17

18

25

beq $s1, $s2, 100

bne

I

5

17

18

25

bne $s1, $s2, 100

slt

R

0

18

19

j

J

2

Field size

17

0

42

2500

slt

$s1, $s2, $s3

j 10000 (see Section 2.9)

6 bits

5 bits

5 bits

5 bits

5 bits

6 bits

ALL MIPS instructions 32 bits

rd

shamt

funct

Arithmetic instruction format

R-format

R

op

rs

rt

I-format

I

op

rs

rt

address

Data transfer, branch format

2004 Morgan Kaufmann Publishers

56

Policy of Use Conventions

Name Register number

$zero

0

$v0-$v1

2-3

$a0-$a3

4-7

$t0-$t7

8-15

$s0-$s7

16-23

$t8-$t9

24-25

$gp

28

$sp

29

$fp

30

$ra

31

Usage

the constant value 0

values for results and expression evaluation

arguments

temporaries

saved

more temporaries

global pointer

stack pointer

frame pointer

return address

Register 1 ($at) reserved for assembler, 26-27 for operating system

2004 Morgan Kaufmann Publishers

57

Constants

•

•

•

Small constants are used quite frequently (50% of operands)

e.g.,

A = A + 5;

B = B + 1;

C = C - 18;

Solutions? Why not?

– put 'typical constants' in memory and load them.

– create hard-wired registers (like $zero) for constants like one.

MIPS Instructions:

addi $29, $29, 4

slti $8, $18, 10

andi $29, $29, 6

ori $29, $29, 4

•

Design Principle: Make the common case fast.

Which format?

2004 Morgan Kaufmann Publishers

58

How about larger constants?

•

•

We'd like to be able to load a 32 bit constant into a register

Must use two instructions, new "load upper immediate" instruction

lui $t0, 1010101010101010

1010101010101010

•

filled with zeros

0000000000000000

Then must get the lower order bits right, i.e.,

ori $t0, $t0, 1010101010101010

1010101010101010

0000000000000000

0000000000000000

1010101010101010

1010101010101010

1010101010101010

ori

2004 Morgan Kaufmann Publishers

59

Assembly Language vs. Machine Language

•

•

•

•

Assembly provides convenient symbolic representation

– much easier than writing down numbers

– e.g., destination first

Machine language is the underlying reality

– e.g., destination is no longer first

Assembly can provide 'pseudoinstructions'

– e.g., “move $t0, $t1” exists only in Assembly

– would be implemented using “add $t0,$t1,$zero”

When considering performance you should count real instructions

2004 Morgan Kaufmann Publishers

60

Other Issues

•

Discussed in your assembly language programming lab:

support for procedures

linkers, loaders, memory layout

stacks, frames, recursion

manipulating strings and pointers

interrupts and exceptions

system calls and conventions

•

Some of these we'll talk more about later

•

We’ll talk about compiler optimizations when we hit chapter 4.

2004 Morgan Kaufmann Publishers

61

Overview of MIPS

•

•

•

•

•

simple instructions all 32 bits wide

very structured, no unnecessary baggage

only three instruction formats

R

op

rs

rt

rd

I

op

rs

rt

16 bit address

J

op

shamt

funct

26 bit address

rely on compiler to achieve performance

— what are the compiler's goals?

help compiler where we can

2004 Morgan Kaufmann Publishers

62

FIGURE 2.13 MIPS machine language revealed

through section 2.6.

MIPS machine language

Name

Format

Example

Comments

add

R

0

18

19

17

0

32

add $s1, $s2, $s3

sub

R

0

18

19

17

0

34

sub $s1, $s2, $s3

lw

I

35

18

17

100

lw

$s1, 100($s2)

sw

I

43

18

17

100

sw

$s1, 100 ($s2)

and

R

0

18

19

17

0

36

and $s1, $s2, $s3

or

R

0

18

19

17

0

37

or

$s1, $s2, $s3

nor

R

0

18

19

17

0

39

nor

$s1, $s2, $s3

andi

I

12

18

17

100

andi $s1, $s2, 100

ori

I

13

18

17

100

ori

$s1, $s2, 100

sll

R

0

0

18

17

10

0

sll

$s1, $s2, 10

srl

R

0

0

18

17

10

2

srl

$s1, $s2, 10

beq

I

4

17

18

25

beq $s1, $s2, 100

bne

I

5

17

18

25

bne $s1, $s2, 100

slt

R

0

18

19

j

J

2

Field size

17

0

42

2500

slt

$s1, $s2, $s3

j 10000 (see Section 2.9)

6 bits

5 bits

5 bits

5 bits

5 bits

6 bits

ALL MIPS instructions 32 bits

rd

shamt

funct

Arithmetic instruction format

R-format

R

op

rs

rt

I-format

I

op

rs

rt

address

Data transfer, branch format

2004 Morgan Kaufmann Publishers

63

2.7 Supporting Procedures in Computer

Hardware

2004 Morgan Kaufmann Publishers

64

Procedure: A stored subroutine that performs a

specific task based on the parameters with which it

is provided.

Jump-and-link instruction: An instruction that

jumps to an address and simultaneously saves the

address of the following instruction in a register

($ra in MIPS)

Return address: A link to the calling site that allows

a procedure to return to the proper address; in

MIPS it is stored in register $ra.

Program Counter (PC): The register containing the

address of the instruction in the program being

executed.

2004 Morgan Kaufmann Publishers

65

Caller: The program that instigates a procedure and

provides the necessary parameter values.

Callee: A procedure that executes a series of stored

instructions based on parameters provided by the

caller and then returns control to the caller.

Stack: A data structure for spilling registers

organized as a last-in-first-out queue.

Stack pointer: A value denoting the most recently

allocated address in a stack that shows where

registers should be spilled or where old register

values can be found.

2004 Morgan Kaufmann Publishers

66

Addresses in Branches and Jumps

•

•

Instructions:

bne $t4,$t5,Label

beq $t4,$t5,Label

$t5

j Label

Formats:

op

I

J

•

op

rs

Next instruction is at Label if $t4 ° $t5

Next instruction is at Label if $t4 =

Next instruction is at Label

rt

16 bit address

26 bit address

Addresses are not 32 bits

— How do we handle this with load and store instructions?

2004 Morgan Kaufmann Publishers

67

Addresses in Branches

•

•

Instructions:

bne $t4,$t5,Label

beq $t4,$t5,Label

Formats:

I

•

•

Next instruction is at Label if $t4≠$t5

Next instruction is at Label if $t4=$t5

op

rs

rt

16 bit address

Could specify a register (like lw and sw) and add it to address

– use Instruction Address Register (PC = program counter)

– most branches are local (principle of locality)

Jump instructions just use high order bits of PC

– address boundaries of 256 MB

2004 Morgan Kaufmann Publishers

68

To summarize:

MIPS operands

Name

32 registers

Example

Comments

$s0-$s7, $t0-$t9, $zero, Fast locations for data. In MIPS, data must be in registers to perform

$a0-$a3, $v0-$v1, $gp,

arithmetic. MIPS register $zero always equals 0. Register $at is

$fp, $sp, $ra, $at

reserved for the assembler to handle large constants.

Memory[0],

30

2

Accessed only by data transfer instructions. MIPS uses byte addresses, so

memory Memory[4], ...,

words

and spilled registers, such as those saved on procedure calls.

add

MIPS assembly language

Example

Meaning

add $s1, $s2, $s3

$s1 = $s2 + $s3

Three operands; data in registers

subtract

sub $s1, $s2, $s3

$s1 = $s2 - $s3

Three operands; data in registers

$s1 = $s2 + 100

$s1 = Memory[$s2 + 100]

Memory[$s2 + 100] = $s1

$s1 = Memory[$s2 + 100]

Memory[$s2 + 100] = $s1

Used to add constants

Category

Arithmetic

sequential words differ by 4. Memory holds data structures, such as arrays,

Memory[4294967292]

Instruction

addi $s1, $s2, 100

lw $s1, 100($s2)

sw $s1, 100($s2)

store word

lb $s1, 100($s2)

load byte

sb $s1, 100($s2)

store byte

load upper immediate lui $s1, 100

add immediate

load word

Data transfer

Conditional

branch

Unconditional jump

$s1 = 100 * 2

16

Comments

Word from memory to register

Word from register to memory

Byte from memory to register

Byte from register to memory

Loads constant in upper 16 bits

branch on equal

beq

$s1, $s2, 25

if ($s1 == $s2) go to

PC + 4 + 100

Equal test; PC-relative branch

branch on not equal

bne

$s1, $s2, 25

if ($s1 != $s2) go to

PC + 4 + 100

Not equal test; PC-relative

set on less than

slt

$s1, $s2, $s3

if ($s2 < $s3) $s1 = 1;

else $s1 = 0

Compare less than; for beq, bne

set less than

immediate

slti

jump

j

jr

jal

jump register

jump and link

$s1, $s2, 100 if ($s2 < 100) $s1 = 1;

Compare less than constant

else $s1 = 0

2500

$ra

2500

Jump to target address

go to 10000

For switch, procedure return

go to $ra

$ra = PC + 4; go to 10000 For procedure call

2004 Morgan Kaufmann Publishers

69

The six steps of the execution of a procedure

1. Place parameter in a place where the procedure

can access them.

2. Transfer control to the procedure

3. Acquire the storage resources needed for the

procedure.

4. perform the desired task.

5. place the result value in a place where the calling

program can access it.

6. Return control to the point of origin, since a

procedure can be called from several points in a

program.

2004 Morgan Kaufmann Publishers

70

Registers for procedure calling:

• $a0-$a3: four argument registers in which to

pass parameters

• $v0-$v1: two value registers in which to

return values

• $ra: one return address register to return to

the point of origin

• $t0-$t9: 10 temporary registers that are not

preserved by the callee on a procedure call

• $s0-$s7: 8 saved registers that must be

preserved on a procedure call

2004 Morgan Kaufmann Publishers

71

Compiling a C procedure(Doesn’t Call Another)

Int leaf_example (int g, int h, int i, int j)

{ int f:

f=(g+h)-(i+j);

return f;}

leaf_example:

addi $sp, $sp, -12

sw $t1, 8($sp)

sw $t0, 4($sp)

sw $s0, 0($sp)

add $t0, $a0, $a1

add $t1, $a2, $a3

sub $s0, $t0, $t1

add $v0, S0, $zero

lw $s0, 0($sp)

lw $t0, 4($sp)

lw $t1, 8($sp)

addi $sp, $sp, 12

jr $ra

2004 Morgan Kaufmann Publishers

72

Compiling a Recursive C Procedure

Int fact (int n)

{

if (n<1) return (1);

else return (n*fact(n-1));}

fact:

addi $sp, $sp, -8

sw $ra, 4($sp)

sw $a0, 0($sp)

slti $t0, $a0, 1

beq $t0, $zero, L1

addi $v0, $zero, 1

addi $sp, $sp, 8

jr $ra

L1: addi $a0, $a0, -1

jalfact

lw $a0, 0($sp)

lw $ra, 4($sp)

addi $sp, $sp, 8

mul $v0, $a0, $v0

jr $ra

2004 Morgan Kaufmann Publishers

73

FIGURE 2.14 The values if the stack pointer and the stack

(a) before, (b) during, and (c) after the procedure call

2004 Morgan Kaufmann Publishers

74

FIGURE 2.15 What is and what is not preserved across a

procedure call.

Preserved

Not preserved

Saved registers: $s0 - $s7

Temporary registers: $t 0-$t 9

Stack pointer register: $sp

Argument registers: $a0 - $a3

Return address register: $ra

Return value registers: $v0 - $v1

Stack above the stack pointer

Stack below the stack pointer

2004 Morgan Kaufmann Publishers

75

FIGURE 2.16 Illustration of the stack allocation (a)

before, (b) during, and (c) after the procedure call.

2004 Morgan Kaufmann Publishers

76

FIGURE 2.17 The MIPS memory allocation for program

and data.

2004 Morgan Kaufmann Publishers

77

FIGURE 2.18 MIPS register conventions.

Name

Preserved on

call?

Register number Usage

$zero

0

the constant value 0

n.a.

$v0-$v1

2-3

values for results and expression evaluation

no

$a0-$a3

4-7

arguments

no

$t0-$t7

8-15

temporaries

no

$s0-$s7

16-23

saved

yes

$t8-$t9

24-25

more temporaries

no

$gp

28

global pointer

yes

$sp

29

stack pointer

yes

$fp

30

frame pointer

yes

$ra

31

return address

yes

2004 Morgan Kaufmann Publishers

78

FIGURE 2.19 MIPS architecture revealed through

section 2.7.

MIPS operands

Name

Example

Comments

32 registers

$s0-$s7, $t 0- $t 9,

$zero, $a0-a3, $v0-$v1,

$gp, $fp, $sp, $ra

Fast locations for data. In MIPS, data must be in registers to perform arithmetic.

MIPS register $zero always equals 0. $gp (28) is the global pointer, $sp (29) is the

stack pointer, $fp (30) is the frame pointer, and $ra (31) is the return address.

30memory

2

words

Memory[0],

Memory[4], …,

Memory[4294967292]

Accessed only by data transfer instructions in MIPS. MIPS uses byte addresses, so

sequential word addresses differ by 4. Memory holds data structures, arrays, and

spilled registers, such as those saved on procedure calls.

2004 Morgan Kaufmann Publishers

79

MIPS assembly language

Category

Instruction

Example

Meaning

Comments

add

add $s1, $s2, $s3

$s1 = $s2 + $s3

Three operands; Overflow detected

subtract

sub $s1, $s2, $s3

$s1 = $s2 - $s3

Three operands; Overflow detected

load word

lw

$s1, 100($s2)

$s1 = Memory [$s2 + 100]

Data from memory to register

store word

sw

$s1, 100 ($s2)

Memory [$s2 + 100] = $s1

Data from register to memory

and

add $s1, $s2, $s3

$s1 = $s2 & $s3

Three reg. operands; bit-by-bit AND

or

or

$s1, $s2, $s3

$s1 = $s2 | $s3

Three reg. operands; bit-by-bit OR

nor

nor

$s1, $s2, $s3

$s1 = ~($s2 | $s3)

Three reg. operands; bit-by-bit NOR

and immediate

andi $s1, $s2, 100

$s1 = $s2 & 100

Bit-by-bit AND reg with constant

or immediate

ori

$s1, $s2, 100

$s1 = $s2 | 100

Bit-by-bit OR reg with constant

shift left logical

sll

$s1, $s2, 10

$s1 = $s2 << 10

Shift left by constant

shift right logical

srl

$$s1, $s2, 10

$s1 = $s2 >> 10

Shift right by constant

branch on equal

beq $s1, $s2, L

if ($s1 == $s2) go to L

Equal test and branch

branch on not

equal

bne $s1, $s2, L

if ($s1 != $s2) go to L

Not equal test and branch

set on less than

slt

$s1, $s2, $s3

if ($s2 < $s3) $s1 = 1;

else $s1 = 0

Compare less than; used with beq,

bne

set on less than

immediate

slt

$s1, $s2, 100

if ($s2 < 100) $s1 = 1;

else $s1 = 0

Compare less than immediate; used

with beq, bne

jump

j

L

go to L

Jump to target address

jump register

jr

$ra

go to $ra

For procedure return

jump and link

jal

L

$ra = PC + 4; go to L

For procedure

callKaufmann Publishers

2004 Morgan

Arithmetic

Data transfer

Logical

Condition

al branch

Unconditi

onal jump

80

FIGURE 2.20 MIPS machine language revealed

through section 2.7.

Name

Format

Example

Comments

add

R

0

18

19

17

0

32

add $s1, $s2, $s3

sub

R

0

18

19

17

0

34

sub $s1, $s2, $s3

lw

I

35

18

17

100

lw

$s1, 100($s2)

sw

I

43

18

17

100

sw

$s1, 100 ($s2)

and

R

0

18

19

17

0

36

and $s1, $s2, $s3

or

R

0

18

19

17

0

37

or

$s1, $s2, $s3

nor

R

0

18

19

17

0

39

nor

$s1, $s2, $s3

andi

I

12

18

17

100

andi $s1, $s2, 100

ori

I

13

18

17

100

ori

$s1, $s2, 100

sll

R

0

0

18

17

10

0

sll

$s1, $s2, 10

srl

R

0

0

18

17

10

2

srl

$s1, $s2, 10

beq

I

4

17

18

25

beq $s1, $s2, 100

bne

I

5

17

18

25

bne $s1, $s2, 100

slt

R

0

18

19

j

J

2

jr

R

0

jal

J

3

Field size

17

0

42

2500

31

0

0

slt

$s1, $s2, $s3

j 10000 (see Section 2.9)

0

8

2500

jr

$ra

jal

10000 (see section 2.9)

6 bits

5 bits

5 bits

5 bits

5 bits

6 bits

ALL MIPS instructions 32 bits

rd

shamt

funct

Arithmetic instruction format

R-format

R

op

rs

rt

I-format

I

op

rs

rt

address

Data transfer,

branch

formatPublishers

2004

Morgan Kaufmann

81

2.8

Communicating with People

2004 Morgan Kaufmann Publishers

82

Instructions to move bytes

lb $t0, 0($sp); Loads a bytes from

memory, placing it in the rightmost 8

bits of a register.

sb $t0, 0($gp); Stores a bytes from the

rightmost 8 bits of a register, placing it

to memory.

2004 Morgan Kaufmann Publishers

83

FIGURE 2.21 ASCII representation of characters.

ASCII

value

Character

ASCII

value

Character

ASCII

value

Character

ASCII

value

Character

ASCII

value

Character

ASCII

value

Character

32

space

48

0

64

@

80

P

96

`

112

p

33

!

49

1

65

A

81

Q

97

a

113

q

34

“

50

2

66

B

82

R

98

b

114

r

35

#

51

3

67

C

83

S

99

c

115

s

36

$

52

4

68

D

84

T

100

d

116

t

37

%

53

5

69

E

85

U

101

e

117

u

38

&

54

6

70

F

86

V

102

f

118

v

39

‘

55

7

71

G

87

W

103

g

119

w

40

(

56

8

72

H

88

X

104

h

120

x

41

)

57

9

73

I

89

Y

105

I

121

y

42

*

58

:

74

J

90

Z

106

j

122

z

43

+

59

;

75

K

91

[

107

k

123

{

44

,

60

<

76

L

92

\

108

l

124

|

45

-

61

=

77

M

93

]

109

m

125

}

46

.

62

>

78

N

94

^

110

n

126

~

47

/

63

?

79

O

95

_

111

o

127

DEL

2004 Morgan Kaufmann Publishers

84

2.9 MIPS Addressing for 32-Bits Immediates

and Addresses

2004 Morgan Kaufmann Publishers

85

FIGURE 2.23 The effect of the lui instruction.

The machine language version of lui $t0, 255

001111

00000

01000

# $t0 is register 8:

0000000011111111

Contents of register $t0 after executing lui $t0, 255:

0000 0000 1111 1111

0000000011111111

2004 Morgan Kaufmann Publishers

86

Loading a 32-bit Constant

Load 0000 0000 0011 1101 0000 1001 0000

0000 to register $s0

lui $s0, 61 #61 decimal = 0000 0000 0011 1101

ori $s0, $s0, 2304 #2304 decimal = 0000 1001

0000 0000

2004 Morgan Kaufmann Publishers

87

MIPS Addressing Mode Summary

1. Register addressing,

2. Base or displacement addressing,

3. Immediate addressing,

4. PC-relative addressing,

5. Pseudodirect addressing,

2004 Morgan Kaufmann Publishers

88

FIGURE 2.24 Illustration of the five MIPS addressing modes.

1. Immediate addressing

op

rs

rt

Immediate

2. Register addressing

op

rs

rt

rd

...

funct

Registers

Register

3. Base addressing

op

rs

rt

Memory

Address

+

Register

Byte

Halfword

Word

4. PC-relative addressing

op

rs

rt

Memory

Address

PC

+

Word

5. Pseudodirect addressing

op

Address

PC

Memory

Word

2004 Morgan Kaufmann Publishers

89

FIGURE 2.25 MIPS instruction encoding

Op (31:26)

28-26

31-29

0(000)

1(001)

2(010)

0(000) R-format

Bltz/gez

jump

1(001) add

immediate

addiu

2(010) TLB

FLPt

3(011)

5(101)

6(110)

branch

eq

branch

blez

bgtz

set less

sltiu

than imm.

andi

ori

xori

load upper

imm

lbu

lhu

lwr

Jump &

link

4(100)

7(111)

3(011)

4(100) load byte

load half

lw1

load word

5(101) store byte

store half

sw1

store word

6(110)

lwc0

lwc1

7(111)

swc0

swc1

swr

2004 Morgan Kaufmann Publishers

90

Op (31:26)=010000 (TLB), rs(25:21)

23-21

25-24

0(00)

0(000)

mfc0

1(001)

2(010)

cfc0

3(011)

4(100)

mtc0

5(101)

6(110)

7(111)

ctc0

1(01)

2(10)

3(11)

2004 Morgan Kaufmann Publishers

91

Op (31:26)=000000 (R-format), funct(5:0)

2-0

5–3

0(000)

1(001)

0(000) shift left

logical

2(010)

shift right

logical

3(011)

sra

1(001) jump reg.

jalr

2(010) mfhi

mthi

mflo

mtlo

3(011)

mult

multu

div

divu

4(100) add

addu

subtract

subu

set l . t .

sltu

5(101)

4(100)

5(101)

sllv

syscall

break

and

or

6(110)

7(111)

srlv

srav

xor

not or (nor)

6(110)

7(111)

2004 Morgan Kaufmann Publishers

92

FIGURE 2.26 MIPS instruction formats in Chapter 2.

Name

Field size

Fields

6 bits 5 bits 5 bits 5 bits

Comments

5 bits

6 bits

ALL MIPS instructions 32 bits

shamt

funct

Arithmetic instruction format

R-format

op

rs

rt

rd

I-format

op

rs

rt

address/immediate

J-format

op

target address

Transfer, brance, imm. format

jump instruction format

2004 Morgan Kaufmann Publishers

93

FIGURE 2.27 MIPS assembly language revealed in

Chapter 2.

MIPS operands

Name

Example

Comments

32 registers

$s0-$s7, $t 0- $t 9,

$zero, $a0-a3, $v0-$v1,

$gp, $fp, $sp, $ra, $at

Fast locations for data. In MIPS, data must be in registers to perform arithmetic.

MIPS register $zero always equals 0. Register $at is reserved for the assembler to

handle large constants.

memory

words

Memory[0],

Memory[4], …,

Memory[4294967292]

Accessed only by data transfer instructions in MIPS. MIPS uses byte addresses, so

sequential word addresses differ by 4. Memory holds data structures, arrays, and

spilled registers, such as those saved on procedure calls.

2004 Morgan Kaufmann Publishers

94

MIPS assembly language

Category

Arithmetic

Data transfer

Logical

Instruction

Example

Meaning

Comments

add

add $s1, $s2, $s3

$s1 = $s2 + $s3

Three operands; Overflow detected

subtract

sub $s1, $s2, $s3

$s1 = $s2 - $s3

Three operands; Overflow detected

add immediate

addi $s1, $s2, 100

$s1 = $s2+ 100

Used to add constants

load word

lw

$s1, 100($s2)

$s1 = Memory [$s2 + 100]

Word from memory to register

store word

sw

$s1, 100 ($s2)

Memory [$s2 + 100] = $s1

Word from register to memory

load half

lh

$s1, 100($s2)

$s1 = Memory [$s2 + 100]

Halfword memory to register

store half

sh

$s1, 100 ($s2)

Memory [$s2 + 100] = $s1

Halfword register to memory

load byte

lb

$s1, 100($s2)

$s1 = Memory [$s2 + 100]

Byte from memory to register

store byte

sb

$s1, 100 ($s2)

Memory [$s2 + 100] = $s1

Byte from register to memory

load upper immed.

lui

$s1, 100

$s1 = 100 * 2^16

Loads constant in upper 16 bits

and

add $s1, $s2, $s3

$s1 = $s2 & $s3

Three reg. operands; bit-by-bit AND

or

or

$s1, $s2, $s3

$s1 = $s2 | $s3

Three reg. operands; bit-by-bit OR

nor

nor

$s1, $s2, $s3

$s1 = ~($s2 | $s3)

Three reg. operands; bit-by-bit NOR

and immediate

andi $s1, $s2, 100

$s1 = $s2 & 100

Bit-by-bit AND reg with constant

or immediate

ori

$s1, $s2, 100

$s1 = $s2 | 100

Bit-by-bit OR reg with constant

shift left logical

sll

$s1, $s2, 10

$s1 = $s2 << 10

Shift left by constant

shift right logical

srl

$$s1, $s2, 10

$s1 = $s2 >> 10

Shift right by constant

2004 Morgan Kaufmann Publishers

95

Continue..

Condition

al branch

Unconditi

onal jump

branch on equal

beq $s1, $s2, 25

if ($s1 == $s2) go to

PC+4+100

Equal test; PC-relative branch

branch on not

equal

bne $s1, $s2, 25

if ($s1 != $s2) go to L

PC+4+100

Not equal test; PC-relative

set on less than

slt

$s1, $s2, $s3

if ($s2 < $s3) $s1 = 1;

else $s1 = 0

Compare less than; for beq, bne

set on less than

immediate

slt

$s1, $s2, 100

if ($s2 < 100) $s1 = 1;

else $s1 = 0

Compare less than constant

jump

j

2500

go to 10000

Jump to target address

jump register

jr

$ra

go to $ra

For procedure return

jump and link

jal

2500

$ra = PC + 4; go to 10000

For procedure call

2004 Morgan Kaufmann Publishers

96

2.10 Translating and Starting a Program

2004 Morgan Kaufmann Publishers

97

• Pseudoinstruction: A common variation of assembly

language instructions often treated as if it were an instruction

in its own right.

• Symbol table: A table that matches names of labels to the

addresses of the memory words that instructions occupy.

• Linker Also called link editor: A systems program that

combines independtly assembled machine language

programs and resolves all undefined labels into an

executable file.

• Executable file: A functional program in the format of an

object file that contains no unresolved references, relocation

information, symbol table, or debugging information.

• Loader: A systems program that places an object program in

main memory so that it is ready to execute.

2004 Morgan Kaufmann Publishers

98

FIGURE 2.28 A translation hierarchy for C.

2004 Morgan Kaufmann Publishers

99

FIGURE 2.29 Dynamically linked library via lazy

procedure linkage.

2004 Morgan Kaufmann Publishers

100

FIGURE 2.30 A translation hierarchy for JAVA.

2004 Morgan Kaufmann Publishers

101

2.16 Real Stuff: IA-32 Instructions

2004 Morgan Kaufmann Publishers

102

Alternative Architectures

•

Design alternative:

– provide more powerful operations

– goal is to reduce number of instructions executed

– danger is a slower cycle time and/or a higher CPI

–“The path toward operation complexity is thus fraught with peril.

To avoid these problems, designers have moved toward simpler

instructions”

•

Let’s look (briefly) at IA-32

2004 Morgan Kaufmann Publishers

103

IA - 32

•

•

•

•

•

•

•

•

•

•

•

1978: The Intel 8086 is announced (16 bit architecture)

1980: The 8087 floating point coprocessor is added

1982: The 80286 increases address space to 24 bits, +instructions

1985: The 80386 extends to 32 bits, new addressing modes

1989-1995: The 80486, Pentium, Pentium Pro add a few instructions

(mostly designed for higher performance)

1997: 57 new “MMX” instructions are added, Pentium II

1999: The Pentium III added another 70 instructions (SSE)

2001: Another 144 instructions (SSE2)

2003: AMD extends the architecture to increase address space to 64 bits,

widens all registers to 64 bits and other changes (AMD64)

2004: Intel capitulates and embraces AMD64 (calls it EM64T) and adds

more media extensions

“This history illustrates the impact of the “golden handcuffs” of compatibility

“adding new features as someone might add clothing to a packed bag”

“an architecture that is difficult to explain and impossible to love”

2004 Morgan Kaufmann Publishers

104

IA-32 Overview

•

•

Complexity:

– Instructions from 1 to 17 bytes long

– one operand must act as both a source and destination

– one operand can come from memory

– complex addressing modes

e.g., “base or scaled index with 8 or 32 bit displacement”

Saving grace:

– the most frequently used instructions are not too difficult to

build

– compilers avoid the portions of the architecture that are slow

“what the 80x86 lacks in style is made up in quantity,

making it beautiful from the right perspective”

2004 Morgan Kaufmann Publishers

105

IA-32 Registers and Data Addressing

•

Registers in the 32-bit subset that originated with 80386

Name

Use

31

0

EAX

GPR 0

ECX

GPR 1

EDX

GPR 2

EBX

GPR 3

ESP

GPR 4

EBP

GPR 5

ESI

GPR 6

EDI

GPR 7

EIP

EFLAGS

CS

Code segment pointer

SS

Stack segment pointer (top of stack)

DS

Data segment pointer 0

ES

Data segment pointer 1

FS

Data segment pointer 2

GS

Data segment pointer 3

Instruction pointer (PC)

Condition codes

2004 Morgan Kaufmann Publishers

106

IA-32 Register Restrictions

•

Registers are not “general purpose” – note the restrictions below

2004 Morgan Kaufmann Publishers

107

IA-32 Typical Instructions

•

Four major types of integer instructions:

– Data movement including move, push, pop

– Arithmetic and logical (destination register or memory)

– Control flow (use of condition codes / flags )

– String instructions, including string move and string compare

2004 Morgan Kaufmann Publishers

108

IA-32 instruction Formats

•

Typical formats: (notice the different lengths)

a. JE EIP + displacement

4

4

8

CondiDisplacement

tion

JE

b. CALL

8

32

CALL

Offset

c. MOV

6

MOV

EBX, [EDI + 45]

1 1

8

d w

r/m

Postbyte

8

Displacement

d. PUSH ESI

5

3

PUSH

Reg

e. ADD EAX, #6765

4

3 1

32

ADD Reg w

f. TEST EDX, #42

7

1

TEST

w

Immediate

8

32

Postbyte

Immediate

2004 Morgan Kaufmann Publishers

109

Summary

•

•

•

Instruction complexity is only one variable

– lower instruction count vs. higher CPI / lower clock rate

Design Principles:

– simplicity favors regularity

– smaller is faster

– good design demands compromise

– make the common case fast

Instruction set architecture

– a very important abstraction indeed!

2004 Morgan Kaufmann Publishers

110