Document

advertisement

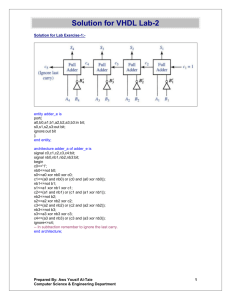

Department of Electrical and Computer Engineering COEN 6501 Dec. 14, 2009 Answer all Questions. All Questions carry equal marks Exam Duration 3 hour No books or papers are allowed. Lecturer: Asim J. Al-Khalili =============================================================== Question 1 a) Explain what we mean by Anti-Fuse in a FPGA. b) Implement function F1 using minimum number of 2:1 MUXs only. All inputs should be of non-inverting type. F1(A,B,C,D) = A+B+ A.C.D c) Implement F1 using Look_up Table. Show the content of the Look-Up table. Question 2 Design the fastest circuit to implement the following function: F=2N2 – 2 N is an integer -2 ≤ N ≤ 2 ie, ( -2, -1, 0, 1, 2 ). Evaluate your circuit in terms of gate delays and gate counts. Question 3 A digital system has a clock generator that produces pulses at a frequency of 80 MHz. design a circuit that provides a clock with a cycle time of 50 ns. Question 4 a) Show the IEEE 754 scheme of rounding to nearest even. b) Add the two operands A= -0.5, B= 17.25 using the IEEE 754 floating point addition. Show all the required addition steps clearly. Question 5 a. Determine maximum speed of operation at typical conditions for the circuit shown in Fig. below, taking into consideration the fan-out loading only. Timing parameters for all components are listed in Table 1. b. At the maximum speed of operation, determine the slack time for the setup time and hold time at the D-input of Flip-Flop D1. c. The circuit is implemented on a die which is packaged in a ceramic DIP with a thermal resistance of 30oC/W. Calculate the drop in maximum speed of operation if the die dissipates a power of 2Watts at an ambient temperature of 40oC. D1 Q CLK Q J JK FF D2 Q K Q CLK CLK Component Tp (ns) Input Loading (UL) K1 Inverter 0.15 1 0.1 AND/NOR(2input) 0.24 2 0.05 XOR (3 input) 0.4 1.5 0.12 Flip Flop, ↑, (CLK to Q) 1.5 2 0.1 ns/UL Tsu=1 ns, th = 0.5ns Td = (Tp K1 Ni K 2 ML) * K ' , T2 KT = 1.5 , T1 K’ = KT * KV *K TJ = Tamb + Φ Ja * Pd , KV = 1 1 0.01 * fV Question 6 a)Write a “process” VHDL Code for a Full_Adder. The inputs are a,b, and c-in and the outputs are S and C-out , KP = 1+ 0.01 * fP b) Draw the circuit given by following the VHDL code below. Identify all nodes with their corresponding names clearly. entity compare_N is port(x,y: in BIT_VECTOR (7 downto 0) ; a_in: in BIT_VECTOR (1 downto 0); a_out: out BIT_VECTOR (1 downto 0) ); end compare_N; architecture behave of compare_N is begin component compare is port(x,y, a_in, b_in: in BIT ; a_out, b_out: out BIT ) ; end component; signal s1, s2: BIT_VECTOR(7 downto 1); begin for i in 7 downto 0 generate if (i=7) generate comp7: compare port map (x(i), y(i), a_in(1), a_in(0), s1(i), s2(i) ); end generate; -- First bit case f (i<= 6 and i>= 1) generate compx: compare port map (x(i), y(i) s1(i+1), s2(i+1) s1(i), s2(i) ); if (i=0) generate comp0: port map (x(i), y(i),s1(i+1) s2(i+1), a_out(1), a_out(0); end generate; -- Normal Case end generate; -- End Case end behave Answers Q1 A 0 0 0 0 0 0 0 0 1 a) The anti fuse in FPGA, refers to programming methodology of the interconnect. There are two types: Poly to diffusion and metal to metal. The anti fuse is the area between two metals or poly and diffusion separated by thin oxide. During programming, high current is passed though the electrodes melting the thin oxide thus permanently connecting the electrodes. The metal / metal process, has lower resistance/capacitance in comparison to Poly / diffusion process. b) F1(A,B,C,D) = A+B+ACD =A+B =(A+A’)(A+B) =A+A’B Content c) of LUT B C D F1 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 1 F1 0 0 0 1 1 1 1 1 1 1 1 0 0 0 1 1 1 1 0 1 1 0 0 1 1 1 0 1 0 1 0 1 1 1 1 1 1 1 1 D A B C D LUT OR LUT OR LUT OR F1 2 bit implementation AB 0 1 1 1 C B A AB, CD Q2 Sign = S N N= -2 -1 0 0 1 2 0 1 1 1 Using sign and magnitude representation F 6 0 -2 – Extreme point -2 -2 ≤ F ≤ 6 0 6 – Extreme point S is 2 bit signed number S N1N0 F is 3 bit signed number SF2F1F0 S N1 N0 Fs F2 F1 F0 0 0 0 1 0 1 0 0 0 1 0 0 0 0 0 1 0 0 1 1 0 0 1 1 x x x x 1 0 0 1 0 1 0 CD 0 0 0 0 1 1 1 0 1 1 1 0 0 0 0 0 0 1 1 0 1 x x x x F0= 0 F1= B’ F2= A F3= (A+B)’ S N1 F0 F1 F2 N0 Fs Costly alternative 2nd alternative: for N2the result is always positive then we can represent N by a 2 bit where the sign bit is ignored (using sign and magnitude). -2= couplet(010)+1=101+1=110 Now shift N2 by 2 bits to the left and Add -2 No 1+ Full adder can be replaced with inverter *If you use sign number multiplication then use booth or bough woody etc. *If 2’ Complement is used then Booth, Bough woody or XOR can be used N2N1N0 N2N1N0 N2N0 0 N2N0 N1N1 LUT N1 N0 0 0 0 1 1 0 1 1 1 0 0 x 1 0 1 x 1 0 1 x 0 0 1 x N0 N1 Q3 T= 1/(80MHz) = 10-6/80 = 10-9*1000/80 = 100/8 = 12.5 ns Transfer a 4 state counter at the Clock of 80dMHz will produce the output Using D Flip Flops 00 11 01 10 Present State Next State Z Y1 Y0 Y1+ Y0+ 0 0 0 1 0 0 1 1 0 0 1 0 1 1 0 1 1 0 0 1 Using D Flip-Flops Y1+= Y1’Y0+Y1Y0’ Y0+= Y0’ Z= Y1Y0 = D1 =D0 Q4 a) The IEEE 745 scheme of rounding the nearest even is shown below M0 R S Error X 0 0 0 X0 0 X 0 0 1 X0 -¼ X 0 1 0 X0 -¼ X 0 1 1 X0 +¼ M0 R S X 1 0 0 X1 X 1 0 1 X1 X 1 1 0 X1 + 1 X 1 1 1 X1 + 1 Error 0 -¼ -½ +¼ i.e. when R(M0+S) is true Assuming equal 0 and 1 distribution error=0 b) Packing operand A=-.5 S=1 e=127-1=126 Mantissa 0000 A 1 0 1 1 1 1 1 1 0 0 0 0 0 Packing Operand B=17.25 S=0 e=127+4 M=00010100 B 0 1 0 0 0 0 0 1 1 0 0 0 1 0 1 0 0 Exponent difference e2-e1 = 5 bits Shift A by 5 positions 1 1 0 0 0 0 0 1 1 0 0 0 0 1 0 0 A shifted by e1-e2=5bits Component A+1 then add to B 11.111110 +01.000010 01.000011 No rounding required since M0 R S are all 0 Pack the results 0 1 0 0 0 0 0 1 1 0 0 0 0 1 1 0 0 Result in decimal 1.0000*24 = 10000.11= 16.75 Q5 a) There are 7 paths D1 AND – JK FF Pah1 D2 XORD1 FF Path2 D2 NOR – JK FF Path3 D1 NOR JK FF Path4 D1 XOR D1 Path5 JK XOR D1 Path6 D1 XOR D1 Path1 & Path4 are the same Path5 is shorter than 1 Path2 & 3 are shorter than Path1 Critical Path So we choose to evaluate Path1 as the critical path. Path1 TCQ=1.5ns, TCL=(2+2+1.5)*.1 +.4+2*.12=1.19ns Tsu=1ns T = TCQ+TCL+Tsu= 1.5+1.19+1= 3.69ns At typical conditions the maximum frequency is 271 MHz b) For FF D1, at maximum speed of operation the slack time = 0 For hold time tn<tCQmin +TCLmin TCLmin is the path JK FF XOR D1 TDL min=1.5ns +1ns+1.5*.1 + .4 + 2*.1 = .7 tn <1.5 +.79 = 2.29 fastest Then hold time slack is 2.29 - .5 = 1.79ns c) KT= (40+2*30+273)/(40+273) = (373/313)=1.3 The main frequency with new condition is 271/1.3=208MHz Q6 The question has many solutions. This is one: entity Full_Adder is Port(a, b, c_in: in std_logic, s, c_out: out std_logic); end entity; architecture behav of Full_Adder is begin Process(a, b, c_in) Begin S<= a XOR b XOR c_in; C_out <= (a and b) or (c_in and (a XOR b)) End Process; end behav x y b) Component: a_in a_out Compare b_out b_in x(7) a_in(0) b_in(0) y(7) Compare 7 x(6) S1(7) a_out(7) b_out(7) S2(7) y(6) Compare 6 x(0) y(0) S1(6) S2(6) a_out(0) b_out(0)