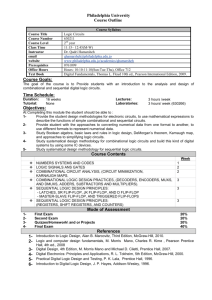

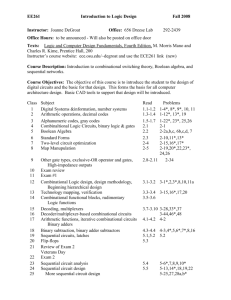

Lecture 11: Sequential Introduction

advertisement

Sequential System Synthesis -- Introduction Outline Combinational Circuits vs. Sequential Circuits Flip-Flop Binary cell that can store one bit of information. Basic Flip-Flop Circuit Common Types of Flip-Flops: RS, JK, D, T. Mealy Machine and Moore Machine Design Flow of Sequential System Synthesis and Optimization Examples ENEE 644 2 Combinational Circuits A circuit is combinational if it computes a function which depends only on the current inputs applied to the circuit; for every input set of values, there is a unique output set of values. Acyclic circuits are necessarily combinational Cyclic circuits can be combinational • in fact, there are combinational circuits whose minimal implementation must have cycles [Kautz 1970] ENEE 644 3 Sequential Circuits In a sequential circuit, the output values may be different for the same set of input values; the output depends on the current contents of memory elements as well. Feedback (cyclic) is a necessary condition for a circuit to be sequential. Synthesis of sequential circuits is not as well developed as combinational. (only small circuits) Sequential synthesis techniques are not really used in commercial software (except maybe retiming). ENEE 644 4 Logic Circuits Combinational x0 x1 xn Combinational Logic Circuit z0 z1 zm Sequential inputs outputs Combinational Logic Circuit Memory Elements Sequential Logic Circuit ENEE 644 5 Basic Flip-Flop Two Output (Q and Q’) Various Ways to Feed Flip-Flops NAND Gate Flip-Flops NOR Gate Flip-Flops R 1 Q S 1 Q S 2 Q’ R 2 Q’ S R Q Q’ S R Q Q’ 1 0 1 0 1 0 0 1 0 0 1 0 1 1 0 1 0 1 0 1 0 1 1 0 0 0 0 1 1 1 1 0 ENEE 644 6 RS Flip-Flop S 3 Q 1 S > CP R 4 Q’ 2 R Q Q’ Three Inputs: Clock Pulse: additional input to control when state is changing. S(et) input R(eset) input Four States: Set state: Reset state: Indetermined: No change: S=1, R=0, CP=1 S=0, R=1, CP=1 S=1, R=1, CP=1 S=0, R=0, CP=1 ENEE 644 (Q=1, Q’=0) (Q=0, Q’=1) (Q=1, Q’=1) 7 RS Flip-Flop (cont’d) Characteristic Equation: Q(t+1) = F(Q(t), S(t+1), R(t+1)) = S + R’Q SR = 0 Characteristic Table: S R Q Q(t+1) 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 i.d. 1 1 1 i.d. ENEE 644 8 JK Flip-Flop K 3 Q 1 CP J J > 4 Q’ 2 Three Inputs: CP: Clock Pulse J: Set input K:Reset input K Q Q’ Four States: Set state: Reset state: No change: Complement: ENEE 644 J=1, K=0, CP=1 J=0, K=1, CP=1 J=0, K=0, CP=1 J=1, K=1, CP=1 9 JK Flip-Flop (cont’d) Characteristic Equation: Q(t+1) = F(Q(t), J(t+1), K(t+1)) = JQ’ + K’Q Characteristic Table: ENEE 644 J K Q Q(t+1) 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 0 10 D Flip-Flop D 3 Q 1 CP D 4 Two Inputs: CP: Clock Pulse D: Set input D’: Reset input Q’ 2 > Q Q’ Two States: Set state: Reset state: D=1, CP=1 D=0, CP=1 Characteristic Equation: Q(t+1) = F(Q(t), D(t+1)) = D ENEE 644 11 T Flip-Flop T 3 Q 1 T > CP 4 Q’ 2 Q Q’ One input JK flip-flop Two States: No Change: T=0, CP=1 Complement: T=1, CP=1 Characteristic Equation: Q(t+1) = F(Q(t), T(t+1)) = TQ’+T’Q ENEE 644 12 Excitation Table Excitation table: the reverse of characteristic table, indicates how we should change flip-flop inputs to make the required state transition. S 0 0 0 0 R 0 0 1 1 Q 0 1 0 1 Q(t+1) 1 0 0 0 0 1 1 0 1 1 characteristic table 1 1 0 i.d. 1 i.d. 1 Q(t+1) S R 0 0 0 x 0 1 1 0 1 0 0 1 table x 0 0 1 1 Q(t) 1excitation 1 ENEE 644 13 Flip-Flop Excitation Tables Q(t) Q(t+1) S R Q(t) Q(t+1) D 0 0 0 x 0 0 0 0 1 1 0 0 1 1 1 0 0 1 1 0 0 1 1 x 0 1 1 1 Q(t) Q(t+1) J K Q(t) Q(t+1) T 0 0 0 x 0 0 0 0 1 1 x 0 1 1 1 0 x 1 1 0 1 1 1 x 0 1 1 0 ENEE 644 14 State, State Reduction and Assignment A state of a sequential circuit is defined by the binary information stored in the memory elements (e.g. flip-flop). One flip-flop stores one bit, so m flip-flops can define at most 2m states. Two states are equivalent if for any input, they produce the same outputs and move to the same or equivalent states. State Reduction problem: reduce the number of flip-flops in a sequential circuit. State Assignment problem: assign binary values to states such that the cost of the flip-flop input functions is reduced. ENEE 644 15 Mealy and Moore Models A sequential system is of Mealy type if output values depend on both present states and inputs. Recall that a state is a combination of the memory element’s content. A sequential system is of Moore type if output values depend only on the present states. This does not mean that output is independent of the inputs. Instead, the impact is through memory units. ENEE 644 16 Sequential Circuit Design Given: system description Goal: logic diagram, Boolean function expression 1. 2. 3. 4. 5. 6. 7. 8. System specification State table/transition graph construction State reduction/minimization State assignment/encoding Flip-flop selection Excitation/output table derivation Logic simplification/minimization Logic diagram drawing ENEE 644 17 Example: Sequential System Design System spec. → state transition table/graph Design a circuit with one input x and three outputs A,B,C. An external source feeds x one bit per clock cycle, when x=0, the outputs remain no change; otherwise, they repeat the binary sequence: 0,1,3,7,6,4, one at a time. next state current state x=0 x=1 A B C A B C A B C 0 0 0 0 0 0 0 0 1 0 0 1 0 0 1 0 1 1 0 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 0 1 1 0 1 0 0 1 0 0 1 0 0 0 0 0 ENEE 644 S1 0/000 1/001 0/001 1/011 S2 0/100 1/100 S3 1/111 1/000 S6 0/011 S5 0/110 1/110 S4 0/111 18 Example: Sequential System Design State Minimization/Reduction Recall that two states are equivalent if for any input, they produce the same outputs and move to the same or equivalent states. We need only one state for all its equivalent states. Therefore, redundant states can be removed and hardware (e.g. flip-flops) can be saved. 1/1 1/1 00 10 00 0/1 0/0 01 01 0/1 1/1 1/0 1/0 = 10 0/0 1/0 01 11 1/1 0/1 0/0 ENEE 644 11 0/0 19 Example: Sequential System Design State Assignment/Encoding The goal is to assign binary values, each bit will be implemented by one flip-flop, to states. Sequential binary assignment: S1=001, S2=010, S3=011 S4=100, S5=101, S6=110 Average bits to be changed: [(0+2)+(0+1)+(0+3)+(0+1)+ (0+2)+(0+3)]/12 = 1 Ad hoc binary assignment: S1 0/000 1/001 0/001 1/011 S2 1/100 S1=000, S2=001, S3=011 S4=111, S5=110, S6=100 0/100 Average bits to be changed: [(0+1)+(0+1)+(0+1)+(0+1)+(0+1)+(0+1)]/12 = 0.5 ENEE 644 S3 1/111 1/000 S6 0/011 S5 0/110 1/110 S4 0/111 20 Example: Sequential System Design System spec. 1/1 00 0/1 0/1 1/0 0/0 01 1/0 10 1/1 11 0/0 → state transition table/graph → state minimization/encoding → flip-flop selection → excitation/output table derivation Current State Next State In Flip-flop inputs Out A B x A B TA TB y 0 0 0 0 1 0 1 0 0 0 1 0 0 0 0 1 0 1 0 1 0 1 1 1 0 1 1 1 1 1 0 0 1 0 0 0 0 1 0 1 1 0 1 0 1 1 1 0 Q(t) Q(t+1) T 0 0 0 0 1 1 1 0 1 1 1 0 1 1 0 0 0 1 1 0 1 1 1 1 0 0 1 1 ENEE 644 21 Example: Sequential System Design System spec. 1/1 00 0/1 0/1 1/0 0/0 01 1/0 10 1/1 11 → state transition table/graph → state minimization/encoding → flip-flop selection → excitation/output table derivation → logic simplification/minimization → logic diagram drawing 0/0 Flip-flop input functions: TA = A B TB = (Ax)’ Output: y = ABx CP x ENEE 644 T > Q Q’ A T > Q Q’ B y 22