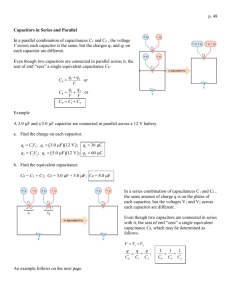

Junction Capacitances

advertisement

EE466: VLSI Design Lecture 02 Non Ideal Effects in MOSFETs Outline • Junction Capacitances – Parasitic capacitances • Velocity Saturation • Channel length modulation • Threshold Voltage – Body effect – Subthreshold conduction Junction Capacitances • The n+ regions forms a number of planar pn-junctions with the surrounding p-type substrate numbered 1-5 on the diagram. • Planar junctions 2, 3 and 4 are surrounded by the p+ channel stop implant. • Planar junction 1 is facing the channel while the bottom planar junction 5 is facing the p-type substrate with doping NA. • The junction types will be n+/p, n+/p+, n+/p+ n+/p+ and n+/p. Junction Capacitances • The voltage dependent source-substrate and drainsubstrate junction capacitances are due to depletion charge surrounding the source or drain diffusion regions embedded in the substrate. • The source-substrate and drain-substrate junctions are reverse biased under normal operating conditions. • The amount of junction capacitance is a function of applied terminal voltages Vgs = 0 + - g + - s d n+ n+ p-type body b Vgd Junction Capacitances • All junctions are assumed to be abrupt. • Given that the depletion thickness is xd we can compute the depletion capacitance of a reverse biased abrupt pn-junction. • Where NA and ND are the ntype and p-type doping densities respectively, V is the negative reverse bias voltage. • The built-in junction potential is: xd 2 Si N A N D 0 V q NAND kT N A N D 0 ln q ni2 Junction Capacitances • The junction is forward biased for a positive voltage V and reverse biased for a negative voltage V. • The depletion region charge stored in this area in terms of xd is • A stands for the junction area. • The junction capacitance associated with the depletion region is defined as: N N N N Q j Aq A D xd A 2 Si q A D 0 V NA ND NA ND Cj • If we differentiate the equation describing Qj with respect to the bias voltage we get Cj. dQ j dV Junction Capacitances • We can write the junction capacitance Si q N A N D C j V A 2 N A N D 0 V • If the zero bias capacitance is: • in a more general form as • m is the gradient coefficient and is 0.5 for abrupt junctions and 1/3 for linearly graded junction profiles • The value of the junction capacitance ultimately depends on the external bias voltage applied across the pnjunction. C j0 1 Si q N A N D 1 2 N A N D 0 C j (V ) AC j 0 V 1 0 m Junction Capacitances • The sidewalls of a typical MOSFET source or drain diffusion region are surrounded by a p+ channel stop implant having a higher doping density than the substrate doping density NA. • The sidewall zero bias capacitance is Cj0sw and will be different from the previously discussed junction capacitance. • The zero-bias capacitance per unit area can be found as follows: C j 0 sw Si q N A( sw) N D 1 2 N A( sw) N D 0( sw) • Where NA(sw) is the sidewall doping density, 0(sw) is the builtin potential of the sidewall junctions. • All sidewalls in a typical diffusion structure have approximately the same junction depth xj. • The zero bias sidewall junction capacitance per unit length is: C jsw C j 0 sw x j MOS Capcitances • Beyond the steady state behavior of the MOS transistor. • In order to examine the transient (AC) response of MOSFETs the digital circuits consisting of MOSFETs we have to determine the nature and amount of parasitic capacitances associated with the MOS transistor. • On chip capacitances found on MOS circuits are in general complicated functions of the layout geometries and the manufacturing processes. • Most of these capacitances are not lumped but distributed and their exact calculations would usually require complex three dimensional nonlinear chargevoltage models. • A lumped representation of the capacitance can be used to analyze the dynamic transient behavior of the device. • The capacitances can be classified as oxide related or junction capacitances and we will start the analysis with the oxide related capacitances. MOS Capacitances Cgb D Cdb Cgd G B Csb Cgs S • Masks result in some regions having overlaps, for example the gate electrode overlaps both the source and drain regions at the edges. • Two overlap capacitances arise as a result. • These are Cgs and Cgd respectively. • If both the source and drain regions have the same width (W), the overlap capacitance becomes: Cgs=CoxWLD and Cgd=CoxWLD. • These overlap capacitances are voltage dependent. • Cgs, Cgd and Cgb are voltage dependent and distributed • They result from the interaction between the gate voltage and the channel charge. MOS Capacitance Model • Simply viewed as parallel plate capacitor • Gate-Oxide-Channel • C = Cg = oxWL/tox = CoxWL • Define – Cpermicron = CoxL = oxL/tox MOS Oxide Capacitances • The gate-to-source capacitance is actually the gate-to-channel capacitance seen between the gate and the source terminals. • The gate-to-drain capacitance is actually the gate-to-channel capacitance seen between the gate and the drain terminals. • In Cut-off mode the surface is not inverted and there is no conducting channel linking the surface to the source and to the drain. • The gate-to-source and gate-todrain capacitances are both equal to zero (Cgs=Cgd=0). • The gate-to-substrate capacitance can be approximated by: Cgb=CoxWL • In linear mode the inverted channel extends across the MOSFET between the source and drain. This conducting inversion layer on the surface effectively shields the substrate from the gate electric field making it Cgb=0. MOSFET Oxide Capacitance • In linear mode the distributed gate-to-channel capacitance maybe viewed as being shared equally between the source and the drain leading to: Cgs=Cgd=0.5CoxWL • If the MOSFET is operating in saturation mode the inversion layer on the surface does not extend to the drain, but is pinched off. • The gate-to-drain capacitance in therefore zero (Cgd=0). • The source is however still linked to the conducting channel. It shields the gate from the channel leading to Cgb of zero. • The distributed gate-to-channel capacitance as seen between the gate and the source is approximated by: Cgs2/3CoxWL. MOS Gate Capacitances Cap Cutoff Linear Saturation Cgb C0 0 0 Cgs 0 C0/2 2/3C0 Cgd 0 C0/2 0 Cg=Cgs+Cgd+Cgb C0 C0 2/3C0 Velocity Saturation • Ideal carrier velocity relation: – v = mE – E = Vds/L • In reality velocity does not increase forever with applied field • For high values of Applied field, E ~ 10000V/cm – v= mE/(1+E/Esat) Velocity Saturation and Mobility Degradation • Recall ideal current equation V I ds Vgs Vt dsat 2 2 Vgs Vt V dsat 2 • With velocity saturated at v=vsat I ds C oxW (V gs Vt )v sat Velocity Saturated Current Modeling • Cutoff – Ids = 0: Vgs<Vt • Linear – Ids = IdsatVds/Vdsat: Vds<Vdsat • Saturation – Ids = Idsat: Vds>Vdsat • Modeling with empirical parameters – α between 2(ideal) to 1(compeletely velocity saturated I dsat Pc 2 (V gs Vt ) Vdsat Pv (Vgs Vt ) / 2 Velocity Saturation • • • • • The critical E-field at which scattering effects occur depends on the doping levels and the vertical electric field applied. Velocity saturation effects are less pronounced in pMOS devices. By increasing VDS the electrical field in the channel ultimately reaches the critical value and the carriers at the drain become velocity saturated. Further increasing VDS does not result in increased ID. The current saturates at IDSAT The behavior of the MOS transistor is better understood by analysis of the IV curves.