Effect of MOS Device Parameters on its Parasitic Capacitances

advertisement

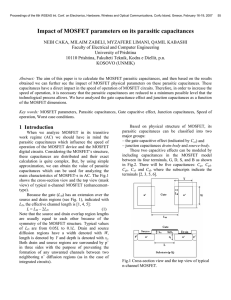

Effect of MOS Device Parameters on its Parasitic Capacitances Ankush Chunn National Institute of technology, Jalandhar ankushchunn@gmail.com Harsh Sohal CURIN,Chitkara University, Punjab harsh.sohal@chitkara.edu.in Abstract:The parasitic capacitances directly affect the performance of CMOS circuit. In this paper the parasitic MOS capacitors are calculated and the effect of physical parameters is analyzed for these capacitances. This analysis help the designers to minimize the necessary parameters permitted by technologly process to hasten the performance of vlsi circuits. The parasitic capacitance are analyzed as a fuction of dimension of MOS device. The parasitic capacitances are mainly classified as gate capacitances and juction or diffusion capacitances. These capacitances are shown in Fig.2 using a lumped representation of MOS model. The various capacitance between the MOS terminals (G,D,S,B) are illustrated as Cgd, Cgs, Cgb, Csb and Cdb where the subscript denotes the two different terminals of device. 1. Introduction While designing any VLSI circuit, the parasitic capacitances states the timing requirements for the circuit. These capacitances are distributed over the length of MOS device and the exact estimation is not possible. However, using approximation the values of different parasitic capacitances can be obtained. These values help in getting the exact characteristics of MOS devices working under different biasing conditions. Fig.1 shows the cross-sectional view and top view of an enhancement n-channel MOSFET . The effective channel length LD reduces due to overlapping of source and drain region and is given by : L LM 2 LD (1) It is to be noted that drain and source overlapping regions are almost equal to each other due to symmetrical MOS structure. Typical LD varies from 0.05 L to 0.1 L. The width of drain and source region (W), length of drain and source region (Y) and depth of drain and source regions (xj) defines the magnitude of parasitic capacitances. The drain and source regions are enclosed on sides by p+ diffusion to avoid formation of any channel between two adjacent n+ diffusion regions. Fig.1 n-channel MOSFET cross-sectional and top view. parasitic capacitances Cgs,Cgd and Cgb are voltage dependent and their value vary under different biasing conditions. This is explained in the table given below. In the triode region, the channel is considered as uniformly distributed from drain to source 1 C gs C gd WLCox and C gb 0 therefore 2 (5) In the saturation region, the channel is tapered due to pinch off voltage at drain. Threrefore the trapezoidal shape is approximated as 2 C gs WLCox and Cgb Cgd 0 3 (6) In the cutoff region, the channel is not formed, the capacitance is given by C gs Cgd 0 C gb WLCox (7) Fig. 2 Parasitic MOSFET capacitances model. 2. The gate capacitive effect The gate capacitance is a byproduct of interaction of gate terminal to source, drain and bulk electrode under different biasing conditions. The overlap capacitance (2) CGSOv CoxWLD is given Now as seen above the sum of all the parasitic capacitances has maximum value WLCox and minimum value 0.66 WLCox , which vary with the biasing gate voltage. It can be inferred from figure 3, that gate capacitive effect is directly proportional to the size of the area & inversely proportional to the thickness of oxide layer. by (3) where Cox indicates CGDOv CoxWLD the oxide capacitance per unit area. Cox ox tox (4) ox is the dielectric constant of Si02, where ox 3.97 0 and tox is the thickness of oxide layer. Overlapping capacitances are voltage independent and do not vary with the bias conditions. Overlapping gate to body capacitance is very small. Whereas the Fig3. The gate capacitance variation with area S and gate oxide. Therefore, when the value of W*L is low, we get less minimum capacitance & when the value of thickness is lowered, the value of capacitance increases but thickness also effects the threshold voltage value. 3. Junction capacitances. There is formation of parasitic capacitance between the source-body and drain-body regions due to reverse polarization in active operating region of MOSFET. Figure 4 below explains a 3-D shape of MOSFET with pn Junctions on five planes around the P-type substrate labelled from 1 to 5. The depletion region capacitance of a reverse biased abrupt pn-junction can be calculated with some assumptions. Let’s consider depletion region thickness as xd . Let the ntype and p-type doping densities be given by N A and N D respectively. Let the reverse bias voltage is given by V .Now the depletion region thickness is given by the formula xd 2 si N A N D . .( V ) … (8) q N A ND Where the Junction potential is given by 0 N N kT ln A 2 D (9) q ni Where k is boltzman’s constant, T is-the temperature given in Kelvin, q is the charge of electron and ni is the intrinsic carrier concentration of Si. Fig 4. 3D view for device with diffusion regions on substrate In MOSFET models these parasitic capacitances are calculated one by one according to their Junctions & they are lumped together. To reduce the calculations, let’s assume that n is rectangular in shape with width as W length as & depth as The pnjunction profile is assumed to be abrupt for simplification. The table 1 shows the different junctions along with area Table 1 N N A. 2. si q A D (o V ) (10) N A ND Where A indicates the area of junction The junction capacitance of depletion region is dQ j given by C j (11) dV Differentiating 10, by voltage V, the expression for capacitance is given by C j v A Junction AREA TYPE 1 W xj n ƒ p 2 Y xj n ƒ p 3 W xj n ƒ p 4 Y xj n ƒ p 5 W Y n ƒ p Normally the Pn-junctions are reverse biased and the change stored in depletion region is N N given by Q j A q A D xd N A ND s q N A N D 1 2 N A N D (o V ) i (12) This expression is C jo C j v A (13) m V 1 0 simplified as m is grading coefficient which is equal to 1/2 for abrupt profile functions & 1/3 for linearly graded profile junctions. The value of terminal voltages changes during the operation of MosFET. So, to find out exact value of junction capacitance is quite complicated. The 4. calculated value of junction capacitance (13) is valid only in small signal model. If we want to calculate the junction capacitance under changing bias conditions, then large signal average junction capacitance is to be calculated as in case of logic circuits. The large signal model can be given as V2 Q Q j V2 Q j V1 1 Ceq C j V dV V V2 V1 V2 V1 V1 (14) Substituting (13) into (14) gives V 1m V 1m Ceq 1 2 1 1 (V2 V1 ) 1 m 0 0 (15) A C jo 0 Assuming abrupt profile junction, m = 1/2 , we have Ceq V V 1 2 1 1 (16) V0 (V2 V1) V0 2C jo0 Taking a dimension coefficient keq as follows keq 2 o V2 V1 o V2 o V1 (17) Ceq A C jo keq where value of keq varies from 0 to 1. Figure 5 shows the relation between parasitic capacitance and the dimension of the drain region. The large dimensions results in higher values of parasitic capacitances. Conclusion The results shown in figure 3 and figure 5 shows the relation between the dimension of MOSFET and both gate and junction capacitances. Thus to conclude, the value of gate capacitance can be minimized by using small channel devices (W and L) according to process specifications. Also, junction parasitic capacitances are smaller if the drain and source dimensions are reduced. Thus, dimensions should always be smaller to obtain higher speed. 5. References [1] Allen, P. E. and E. Sanchez-Sinencio, Switched- Capacitor Circuits, New York: Van Nostrand Reinhold, 1984. [2] Kang, S. M. and Y. Leblebici, CMOS Digital Integrated Circuits, 3th edition, McGraw-Hill, 2003. [3] Neamen, D. A. Electronic Circuit Analysis and Design, 2th edition, New York: McGrawHill, 2001. [4] Sedra, A. C. and K. C. Smith, Microelectronic Circuits, 5th edition, Oxford University Pres 2004 [5] Tsividis, Y. P., Operation and Modeling of the MOS Transistor , New York: Oxford University Press, 1999.