A Test-Wrapper

advertisement

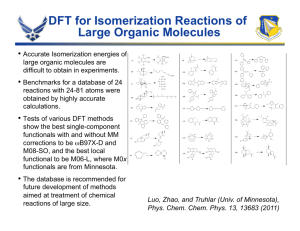

Mixed-Signal Test and DFT Vishwani D. Agrawal Agere Systems, Murray Hill, NJ 47974 va@agere.com http://cm.bell-labs.com/cm/cs/who/va May 17, 2001 May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 1 VLSI Realization Process Customer’s need Determine requirements Write specifications Design synthesis and Verification Test development Fabrication Manufacturing test Chips to customer May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 2 Costs of Testing Design for testability (DFT) Chip area overhead and yield reduction Performance overhead Software processes of test Test generation and fault simulation Test programming and debugging Manufacturing test Automatic test equipment (ATE) capital cost Test center operational cost May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 3 Cost of Manufacturing Testing in 2000AD 0.5-1.0GHz, analog instruments,1,024 digital pins: ATE purchase price = $1.2M + 1,024 x $3,000 = $4.272M Running cost (five-year linear depreciation) = Depreciation + Maintenance + Operation = $0.854M + $0.085M + $0.5M = $1.439M/year Test cost (24 hour ATE operation) = $1.439M/(365 x 24 x 3,600) = 4.5 cents/second May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 4 Testing Principle May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 5 Characterization Test Worst-case test Choose test that passes/fails chips Select statistically significant sample of chips Repeat test for every combination of 2+ environmental variables Plot results in Schmoo plot Diagnose and correct design errors Continue throughout production life of chips to improve design and process to increase yield May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 6 Manufacturing Test Determines whether manufactured chip meets specs Must cover high % of modeled faults Must minimize test time (to control cost) No fault diagnosis Tests every device on chip Test at speed of application or speed guaranteed by supplier May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 7 Burn-in or Stress Test Process: Subject chips to high temperature & overvoltage supply, while running production tests Catches: Infant mortality cases – these are damaged chips that will fail in the first 2 days of operation – causes bad devices to actually fail before chips are shipped to customers Freak failures – devices having same failure mechanisms as reliable devices May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 8 Test Specifications & Plan Test Specifications: Functional Characteristics Type of Device Under Test (DUT) Physical Constraints – Package, pin numbers, etc. Environmental Characteristics – supply, temperature, humidity, etc. Reliability – acceptance quality level (defects/million), failure rate, etc. Test plan generated from specifications Type of test equipment to use Types of tests Fault coverage requirement May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 9 Automatic Test Equipment Components Consists of: Powerful computer Powerful 32-bit Digital Signal Processor (DSP) for analog testing Test Program (written in high-level language) running on the computer Probe Head (actually touches the bare or packaged chip to perform fault detection experiments) Probe Card or Membrane Probe (contains electronics to measure signals on chip pin or pad) May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 10 ADVANTEST Model T6682 ATE May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 11 LTX FUSION HF ATE May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 12 Test Process Summarized Parametric tests – determine whether pin electronics system meets digital logic voltage, current, and delay time specs Functional tests – determine whether internal logic/analog sub-systems behave correctly ATE Cost Problems Pin inductance (expensive probing) Multi-GHz frequencies High pin count (1024) ATE Cost Reduction Multi-Site Testing DFT methods like Built-In Self-Test May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 13 Mixed-Signal Testing Problem May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 14 Differences from Digital Testing Size not a problem – at most 100 components Much harder analog device modeling No widely-accepted analog fault model Infinite signal range Tolerances depend on process and measurement error Tester (ATE) introduces measurement error Digital / analog substrate coupling noise Absolute component tolerances +/- 20%, relative +/- 0.1% Multiple analog fault model mandatory No unique signal flow direction May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 15 Present-Day Analog Testing Methods Specification-based (functional) tests Main method for analog – tractable and does not need an analog fault model Intractable for digital -- # tests is huge Structural ATPG – used for digital, just beginning to be used for analog (exists) Separate test for functionality and timing not possible in analog circuit Possible in digital circuit May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 16 DSP Tester Concept May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 17 Waveform Synthesis Needs sin x / x (sinc) correction – Finite sample width May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 18 Waveform Sampling Sampling rate > 100 ks/s May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 19 A/D and D/A Test Parameters A/D -- Uncertain map from input domain voltages into digital value (not so in D/A) Two converters are NOT inverses Transmission parameters affect multi-tone tests Gain, signal-to-distortion ratio, intermodulation distortion, noise power ratio, differential phase shift, envelop delay distortion Intrinsic parameters – Converter specifications Full scale range (FSR), gain, # bits, static linearity (differential and integral), maximum clock rate, code format, settling time (D/A), glitch area (D/A) May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 20 Ideal Transfer Functions A/D Converter May 17, 2001 D/A Converter Mixed-Signal Test and DFT: va@agere.com 21 Offset Error May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 22 Gain Error May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 23 D/A Transfer Function Non-Linearity Error May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 24 Differential Linearity Error Differential linearity function – How each code step differs from ideal or average step (by code number), as fraction of LSB Subtract average count for each code tally, express that in units of LSBs Repeat test waveform 100 to 150 times, use slow triangle wave to increase resolution May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 25 Linear Histogram and DLE of 8-bit ADC May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 26 DSP-Based Testing DSP-based tester has: Waveform Generator Waveform Digitizer High frequency clock with dividers for synchronization A/D and D/A Test Parameters Transmission Intrinsic A/D and D/A Faults: offset, gain, non-linearity errors Measured by DLE, ILE, DNL, and INL A/D Test Histograms – static linear and sinusoidal D/A Test –- Differential Test Fixture May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 27 DSP-Based Test Concepts Quantization Error – Introduced into measured signal by discrete sampling Quantum Voltage – Corresponds to flip of LSB of converter Single-Tone Test -- Test of DUT using only one sinusoidal tone Tone – Pure sinusoid of f, A, and phase f Transmission (Performance) Parameter -indicates how channel with embedded analog circuit affects multi-tone test signal UTP – Unit test period: joint sampling period for analog stimulus and response May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 28 Spectral Test of A/D Converter May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 29 Spectral Components in DSP-Based Testing May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 30 A/D Converter Spectrum Audio source at 1076 Hz sampled at 44.1 kHz May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 31 Coherent Multi-Tone Testing May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 32 Analog Test Bus PROs: Usable with digital JTAG boundary scan Adds analog testability – both controllability and observability Eliminates large area needed for analog test points CONs: May have a 5 % measurement error C-switch sampling devices couple all probe points capacitively, even with test bus off – requires more elaborate (larger) switches Stringent limit on how far data can move through the bus before it must be digitized to retain accuracy May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 33 Analog Test Bus Diagram May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 34 Analog Boundary Module May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 35 Chaining of 1149.4 ICs May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 36 Partitioning for Test Partition according to test methodology: Logic blocks Memory blocks Analog blocks Provide test access: Boundary scan Analog test bus Provide test-wrappers (also called collars) for cores. May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 37 Test-Wrapper for a Core Test-wrapper (or collar) is the logic added around a core to provide test access to the embedded core. Test-wrapper provides: For each core input terminal A normal mode – Core terminal driven by host chip An external test mode – Wrapper element observes core input terminal for interconnect test An internal test mode – Wrapper element controls state of core input terminal for testing the logic inside core For each core output terminal May 17, 2001 A normal mode – Host chip driven by core terminal An external test mode – Host chip is driven by wrapper element for interconnect test An internal test mode – Wrapper element observes core outputs for core test Mixed-Signal Test and DFT: va@agere.com 38 A Test-Wrapper from/to External Test pins Scan chain to/from TAP May 17, 2001 Mixed-Signal Test and DFT: va@agere.com Functional core outputs Core Scan chain Scan chain Functional core inputs Wrapper elements Wrapper test controlle r 39 Overhead Estimate Rent’s rule: For a logic block the number of gates G and the number of terminals t are related by t = K Ga where 1 < K < 5, and a ~ 0.5. Assume that block area A is proportional to G, i.e., t is proportional to A 0.5. Since test logic is added to each terminal t, Test logic added to terminals Overhead = ------------------------------------------------- ~ A –0.5 A May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 40 DFT Architecture for SOC Module N wrapper 1 Func. outputs Func. inputs Test Module wrapper Functional inputs User defined test access mechanism (TAM) Test Test source Test sink Functional outputs Instruction register control May 17, 2001 TDO TRST TMS TCK SOC inputs Test access port (TAP) TDI Serial instruction data Mixed-Signal Test and DFT: va@agere.com SOC outputs 41 DFT Components Test source: Provides test vectors via on-chip LFSR, counter, ROM, or off-chip ATE. Test sink: Provides output verification using on-chip signature analyzer, or off-chip ATE. Test access mechanism (TAM): User-defined test data communication structure; carries test signals from source to module, and module to sink; tests module interconnects via test-wrappers; TAM may contain bus, boundary-scan and analog test bus components. Test controller: Boundary-scan test access port (TAP); receives control signals from outside; serially loads test instructions in test-wrappers. May 17, 2001 Mixed-Signal Test and DFT: va@agere.com 42 Summary Functional test: verify system hardware, software, function and performance; pass/fail test with limited diagnosis; high (~100%) software coverage metrics; low (~70%) structural fault coverage. Diagnostic test: High structural coverage; high diagnostic resolution; procedures use fault dictionary or diagnostic tree. SOC design for testability: May 17, 2001 Partition SOC into blocks of logic, memory and analog circuitry, often on architectural boundaries. Provide external or built-in tests for blocks. Provide test access via boundary scan and/or analog test bus. Develop interconnect tests and system functional tests. Develop diagnostic procedures. Mixed-Signal Test and DFT: va@agere.com 43