MAX 7000 Design Optimization: Altera Devices

Optimizing Designs for

Altera’s MAX 7000 Devices

Copyright © 1998 Altera Corporation

Course Outline

SECTION 1: MAX 7000 Family Overview

SECTION 2: MAX 7000 Device Architecture

– Laboratory Exercise #1

SECTION 3: Design Methodology and Guidelines for

MAX 7000 Devices

– Design Entry Techniques

– Resolving Fitting Issues

• Laboratory Exercise #2

– Resolving Performance Issues

• Laboratory Exercise #3

SECTION 4: Programming MAX 7000 Devices

– Laboratory Exercise #4

Copyright © 1998 Altera Corporation

SECTION 1

MAX 7000 Family Overview

Copyright © 1998 Altera Corporation

Altera Offering

200

FLEX 8000A

FLEX 10K

FLEX 10KA

FLEX 6000

FLEX 6000A

FLEX 10KE

100

MAX 7000

(includes

MAX 7000E)

MAX

7000A

MAX

7000B

MAX 7000S

MAX

9000

MAX

9000A

2000 5000

Copyright © 1998 Altera Corporation

12,000

Usable Gates

20,000

24,000 250,000

MAX 7000 Device Technology

Multiple Array MatriX (MAX) devices :

– programmable - AND / fixed - OR product term architecture

Altera MAX 7000 devices include:

– MAX 7000

– MAX 7000E

– MAX 7000S

– MAX 7000A

– MAX 7000B

EPLDs fabricated on CMOS process

EEPROM configuration elements (non-volatile)

Copyright © 1998 Altera Corporation

MAX 7000 => E => S => A => B

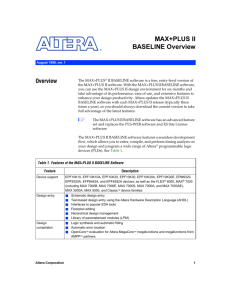

FEATURES MAX 7000 MAX 7000E MAX 7000S MAX 7000A MAX 7000B

Core Voltage

ISP

JTAG BST Circuitry

5.0 Volts 5.0 Volts 5.0 Volts

X

EPM7128S and larger devices

X

3.3 Volts

Enhanced ISP features (excluding

7128A and 7256A)

X

X

2.5 Volts

Enhanced ISP features

X

Open Drain Outputs

Fast Input Registers

Output Enables

2 Global OEs

(dedicated inputs)

1 Global Clock

X

6 pin or logic driven OEs

X

X

6 pin or logic driven OEs

X

X

X X

6 to 10 pin or logic driven OEs

6 to 10 pin or logic driven OEs

X X 2 Global Clocks

Slew Rate control X X X

Technology 0.5um

0.5um

0.5um

0.35um

Note: In addition to the features listed here, the MAX 7000E/S/A/B devices also have enhanced routing resources as compared to MAX 7000

Copyright © 1998 Altera Corporation

X

0.25um

MAX 7000 Device Offering

MAX 7000

(includes

MAX 7000E)

EPM7032

EPM7064

EPM7096

EPM7128E

MAX 7000S MAX 7000A MAX 7000B

EPM7032S EPM7032AE EPM7032B

EPM7064S EPM7064AE EPM7064B

EPM7160E

EPM7192E

EPM7256E

Copyright © 1998 Altera Corporation

EPM7128S

EPM7128A

EPM7128AE

EPM7128B

EPM7160S

EPM7192S

EPM7256S

EPM7256A

EPM7256AE

EPM7256B

EPM7384AE EPM7384B

EPM7512AE EPM7512B

* Check availability

MAX 7000 Family

Feature

EPM7032

EPM7032V

EPM7064

EPM7032S

EPM7032AE

EPM7064AE

EPM7064B

EPM7032B

EPM7064S

EPM7096

EPM7128E

EPM7128S

EPM7128A

EPM7128AE

EPM7128B

EPM7160E

EPM7160S

EPM7192E

EPM7192S

EPM7256E

EPM7256S

EPM7256A

EPM7256AE

EPM7384AE EPM7512AE

EPM7384B EPM7512B

EPM7256B

Macrocells 32 64 96 128 160 192 256 384 512

Usable Gates

Flipflops

600

32

1250

64

1800

96

2500

128

3200

160

3750

192

5000

256

7500

384

10000

512

Note: Use Altera’s web site to check device and package availability http://www.altera.com

Copyright © 1998 Altera Corporation

Device Part Numbers

EPM7128ATC144-6

– EPM = Family Signature (Erasable Programmable MAX device)

– 7128A =

– T =

– C

– 144

=

=

Device type (128 = number of macrocells)

Package type (L = PLCC, T = TQFP...)

Operating temperature (Commercial, Industrial)

Pin count (number of pins on the package)

– -6 = Speed Grade (-5, -6, -7, -10, -12, -15)

– Suffix may follow speed grade (for special device features)

Another Example:

– EPM7064SLC44-5

• EPM7064S in a commercial-temp, 44 pin PLCC package with a 5 ns speed grade

Copyright © 1998 Altera Corporation

Vertical Migration

MAX 7000 devices of different densities but same packages are pin compatible (with some exceptions)

– GND and VCC pins are in the same places

– Dedicated inputs are in the same places

– Remainder of pins are either I/O pins or no connects

EXCEPTIONS:

– MAX 7000 devices in 160 pin QFP packages

• The EPM7128E/S/A/AE/B and EPM7160E/S are pin compatible

• The EPM7192E/S and EPM7256E/S/A/AE/B are pin compatible

• But the two sets are different from each other

– EPM7256A

• When migrating to larger density MAX 7000A devices, some of the EPM7256A no connects turn into VCC pins

Copyright © 1998 Altera Corporation

Altera’s MultiVolt Capability

MultiVolt separates power and ground for device core and

I/O

Allows MAX device to bridge between systems of different voltages

Copyright © 1998 Altera Corporation

Altera’s MultiVolt Offering

Device

MAX 7000/E/S

MAX 7000A

MAX 7000B

Drives (TTL)

VccINT VccIO 2.5

3.3

5.0

5.0

5.0

3.3

X

X

X

3.3

3.3

2.5

X

X X

Driven by

2.5

3.3

5.0

X

X

X

X

X

X

X

X

X

X

2.5

TBD TBD TBD TBD TBD TBD TBD

* MultiVolt is not available in 44-pin packages

Copyright © 1998 Altera Corporation

Turbo Bit

MAX 7000 devices offer low-power OR high speed operation

Total power dissipation can be reduced by 50% or more

This is controllable for the entire device OR on a macrocell by macrocell basis

– A section of the design can operate in high performance (Turbo Bit =

ON) and other sections may operate in low power (Turbo Bit = OFF)

– MAX 7000 devices: macrocells running at low power (Turbo Bit = OFF) incur a delay t

LPA t

SEXP parameters

(8 ns for -5 speed grade) for the t

LAD

, t

LAC

, t

IC

, t

ACL t

EN

,

Copyright © 1998 Altera Corporation

SECTION 2

MAX 7000 Device Architecture

Copyright © 1998 Altera Corporation

Altera MAX 7000 Device Terminology

Macrocell

– The basic building block of a product term based device

– Equivalent to a logic cell (term used to describe the basic building block of any Altera device)

Logic Array Block (LAB)

– A group of logic cells

– Each LAB in a MAX device contains 16 macrocells

Programmable Interconnect Array (PIA)

– Continuous interconnect structure of a MAX 7000 device

Copyright © 1998 Altera Corporation

Device Block Diagram

4 dedicated inputs drive PIA, Macrocells,

I/O Control Block

36 36

16

Macrocells

16 16

16

Macrocells

I/O Control Block

3 to 16

16

Macrocells

16

36

P

I

A

36

16

3 to 16

16

Macrocells

3 to 16

I/O pins

Logic Array Block (LAB)

Copyright © 1998 Altera Corporation

3 to 16 3 to 16

3 to 16 fast input paths

MAX 7000E/S/A/B devices only

Logic Array Block

INPUT

INPUT

INPUT

INPUT

GCLK1

GCLK2

GCLR

GOE

The dedicated inputs are shown here for

MAX 7000E, MAX 7000S, MAX 7000A and

MAX 7000B devices. See next slide for more information.

Copyright © 1998 Altera Corporation

Programmable Interconnect Array (PIA)

36

16

Macrocell 1

Macrocell 2

Macrocell 3

Macrocell 4

Macrocell 5

Macrocell 6

Macrocell 7

Macrocell 8

Macrocell 9

Macrocell 10

Macrocell 11

Macrocell 12

Macrocell 13

Macrocell 14

Macrocell 15

Macrocell 16

16

3 to 16 fast input paths

MAX 7000E/S/A/B devices only

3 to 16

I/O

Control

Block

3 to 16

I/O pins

Shared Logic Expanders

INPUT

INPUT

INPUT

INPUT

MAX 7000E/S/A/B

GCLK1

OE2/GCLK2

GCLRn

OE1

INPUT

INPUT

INPUT

INPUT

Programmable Interconnect Array (PIA)

MAX 7000

GCLK1

OE1n

OE2n

GCLRn

4 Dedicated Inputs can drive

– any macrocell control signal (clock, clear, preset, enable)

– data

– any combination of above (if the input drives a control signal as well as different type of control signal or data 6 to 16

I/O pins then the control signal will be non-global)

Copyright © 1998 Altera Corporation

Shared Logic Expanders

Macrocell

LAB Local Array

Parallel

Expanders from other macrocells

Product-

Term

Select

Matrix

Global

Clear

Global Clock(s)

MAX 7000 -> 1

MAX 7000E/S/A/B -> 2

From I/O Pin

Fast Input Select ->

MAX 7000E/S/A/B only

Register

Bypass

To I/O

Control

Block

D

PRN

Q

EN

CLRN

Clear

Select

Clock/

Enable

Select

Shareable

Logic

Expanders

To

PIA

16 shared expander product terms

Copyright © 1998 Altera Corporation

XOR Functionality

With XOR Synthesis logic option SELECTED

– MAX+plus II can minimize a design by creating new XOR gates that feed combinatorial (non-registered) logic cells

–

This may save resources (logic cells and product terms)

– This may introduce glitches to some designs

Product-

Term

Select

Matrix

Copyright © 1998 Altera Corporation

XOR Functionality

With XOR Synthesis logic option SELECTED

– MAX+plus II can minimize a design by creating new XOR gates that feed combinatorial (non-registered) logic cells

–

This may save resources (logic cells and product terms)

– This may introduce glitches to some designs

Product-

Term

Select

Matrix

With XOR Synthesis logic option NOT selected

– The XOR gate can be used for inversion or for XOR functions already specified in the design (existing XOR gates)

–

MAX+plus II will not create new XOR gates

– Glitches are less likely to occur, but more resources will be needed

Copyright © 1998 Altera Corporation

Expanders

LAB Local Array

16 shared expander product terms

Copyright © 1998 Altera Corporation

Product-

Term

Select

Matrix

Parallel

Expanders from other macrocells

Expanders are used to create logic functions requiring more resources than in a single macrocell

Shareable Logic

Expanders

When expanders are needed to implement a logic function, shared expanders are automatically used by default

Shareable Logic Expanders

Each macrocell can donate one product term as a shared expander instead of using it as a standard product term

Each LAB can have up to 16 shared expanders that can be used by any or all macrocells in the

LAB

LAB Local Array

Copyright © 1998 Altera Corporation

}

Macrocell

Product-

Term Logic

}

Macrocell

Product-

Term Logic

Parallel Expanders

Parallel expanders are unused product terms that can be allocated to neighboring macrocells

Parallel expanders implement faster complex logic functions

LAB Local Array

Product-

Term

Select

Matrix

GND

Product-

Term

Select

Matrix

GND

Preset

From previous macrocell parallel expanders

Clock

Clear

Preset

Clock

Clear

To next macrocell

Copyright © 1998 Altera Corporation

Parallel Expanders- Architecture Rules

LAB A

Cannot borrow any parallel expanders

Can borrow up to 10 parallel expanders from Macrocell 1 and

Macrocell 2

MAX+plus II will automatically place logic in the device to conform to these architecture rules

Macrocell 1

Macrocell 2

Macrocell 3

Macrocell 4

Macrocell 5

Macrocell 6

Macrocell 7

Macrocell 8

Macrocell 9

Macrocell 10

Macrocell 11

Macrocell 12

Macrocell 13

Macrocell 14

Macrocell 15

Macrocell 16

}

Can borrow up to 5 parallel expanders from Macrocell 1

Can borrow up to 15 parallel expanders from the three macrocells immediately above it

Cannot borrow any parallel expanders

Copyright © 1998 Altera Corporation

Parallel Expanders- Architecture Rules

From previous macrocell

A macrocell must borrow all five of the previous macrocell’s product terms before borrowing from another macrocell

Product-

Term

Select

Matrix

GND

Preset parallel expanders

Clock

Clear

A macrocell must use all 5 of its own product terms before trying to borrow from the previous macrocell

Product-

Term

Select

Matrix

GND

Preset

Clock

Clear

A maximum of 20 product terms may directly feed the OR gate of a certain macrocell

Copyright © 1998 Altera Corporation

Parallel Expanders- Architecture Rules

What happens to the rest of a macrocell when it lends less than 5 of its product terms as parallel expanders?

– The rest of the macrocell may still be used

Product-

Term

Select

Matrix

GND

Preset parallel expanders

Clock

Clear

From previous macrocell

Preset

Product-

Term

Select

Matrix

GND

Clock

Clear

Copyright © 1998 Altera Corporation

Parallel Expanders vs. Shareable Expanders

Expander Type Advantage Added Delay

Parallel

Shareable

Speed

Flexibility

Tpexp

Tsexp

Examples

One set of five expanders adds a

0.8 ns delay for MAX 7000 -5

One shareable expander adds a

3 ns delay for MAX 7000 -5

Copyright © 1998 Altera Corporation

Logic Option Assignments

Logic options are “switches” that can be set in

MAX+plus II that control the way MAX+plus II will implement your design in the MAX device

A single logic option controls a single feature of the

MAX device

For example, enabling the Turbo Bit is controlled through a logic option

The set of available logic options varies from device family to device family

There are many features in MAX devices that are controllable; use logic options to get the most control over the MAX design

Copyright © 1998 Altera Corporation

Logic Option Assignments - Examples

Parallel Expanders : Controls the use of parallel expanders to implement the design

Turbo Bit: Controls the use of the turbo bit either on a device-wide or macrocell-by-macrocell basis

XOR Synthesis : Allows MAX+plus II to create new XOR gates from a given design to map to the XOR gate in the macrocell

Fast I/O : Applied to input pins to enable the fast input path from an input pin directly to a macrocell register

Slow Slew Rate : Applied to output pins in MAX 7000E/S/A/B devices to slow down the output transitions

Power-up High : Applied to an individual register in a MAX 7000AE or MAX 7000B device, that will cause the register to power up high

(1)

Global Signal : Applied to input pins to implement them on a dedicated input and make use of the global signal

Copyright © 1998 Altera Corporation

Synthesis Styles and MAX Features

Synthesis Styles may be assigned

Globally, to the project/design Individually, to a subdesign

Styles synthesize for

–

Normal - fit

–

Fast - performance

– WYSIWYG - minimal synthesis

– User-defined styles

Default Style is Normal

Copyright © 1998 Altera Corporation

Synthesis Styles and MAX Features

For each Synthesis Style the available logic options are set to different default values

NORMAL will not implement Parallel expanders

FAST will use parallel expanders where appropriate

WYSIWYG will not implement Parallel expanders

Copyright © 1998 Altera Corporation

Accessing Parallel Expanders

Individual

Logic Options are used to assign parallel expanders to subdesigns without altering the Synthesis

Style

Copyright © 1998 Altera Corporation

Parallel Expanders vs. Shareable Expanders

Expanders

Control

PARALLEL

by

Control

SHAREABLE

by

Logic Option/

Synthesis Style

Fitter Settings

Dialog Box*

*Shareable Expanders are automatically used by default

Copyright © 1998 Altera Corporation

Parallel Expanders vs. Shareable Expanders

Expanders

Use

PARALLEL

for

Use

SHAREABLE

for

SPEED FLEXIBILITY

and

RESOURCE

SAVINGS

Copyright © 1998 Altera Corporation

Laboratory Exercise 1

Go to Laboratory Exercise Manual and

Complete Exercise 1

Copyright © 1998 Altera Corporation

Programmable Interconnect Array (PIA)

The PIA is a global bus which can connect any signal source to any destination on the device

LAB A

Macrocell 1

Macrocell 2

Macrocell 3

LAB B

Macrocell 1

Macrocell 2

Macrocell 3

Macrocell 16

The PIA has a predictable delay (t

PIA

= .8 ns for -5 speed grade)

Copyright © 1998 Altera Corporation

Macrocell 16

Programmable Interconnect Array

36 partially populated

MUXs per LAB

Each signal in the PIA has at least 2 paths into each LAB:

2 paths ->

EPM7032/S/AE/B,

EPM7064/S/AE/B,

EPM7096

4 paths ->

EPM7128E/S/A/AE/B,

EPM7160E/S,

EPM7192E/S,

EPM7256E/S/A/AE/B,

EPM7384AE/B,

EPM7512AE/B

LAB B

Macrocell 1

Macrocell 2

Macrocell 3

Macrocell 16

Copyright © 1998 Altera Corporation

MAX 7000 I/O Control Block

OE1

OE2

VCC

OE control

Up to 2 pin-driven global OE signals available for the

MAX 7000 devices

GND from Macrocell to PIA

Input pins drive the PIA

Macrocells directly drive output pins

Copyright © 1998 Altera Corporation

P

I

A

MAX 7000E/S/A/B I/O Data Paths

VCC

Input pins drive the PIA

– For faster setup times they directly drive macrocell registers

Macrocells directly drive output pins

OE control from Macrocell

Fast Input to

Macrocell Register

Copyright © 1998 Altera Corporation

GND

Open-Drain (MAX 7000S/A/B devices only)

Slew-Rate Control to PIA

P

I

A

MAX 7000E/S/A/B Output Enables

Global OEs

Up to 6 global OE signals, including the dedicated OE input, can be used for OEs in MAX 7000E/S/A/B devices

EPM7384 and EPM7512 have 10

OEs

OE control from Macrocell

Fast Input to Macrocell Register to PIA

Copyright © 1998 Altera Corporation

GND

Open-Drain (MAX 7000S/A/B devices only)

Slew-Rate Control

P

I

A

MAX 7000E/S/A/B Individual Pin Controls

When Slow Slew Rate is selected, board-level noise is reduced and a timing delay is added to the output buffer delay parameter

Compare t

OD1

, t

OD2

, t

OD3

Data Book in the

Open-Drain (open-collector) output available for MAX 7000S/A/B devices

Open-Drain

(MAX 7000S/A/B devices only)

Slew-Rate Control

Fast Input to Macrocell Register to PIA

Copyright © 1998 Altera Corporation

SECTION 3

Design Methodology and Guidelines for MAX 7000 Devices

Copyright © 1998 Altera Corporation

Altera Design Methodology

* -

Focus area

*

Design Specification

Design Entry

Functional Compilation

Functional Error?

Resolve Functional Errors

Copyright © 1998 Altera Corporation

*

Synthesis/Timing Compilation

Fit OK?

Timing Analysis

*

Resolve Fitting Issues

*

Resolve Performance Issues Performance OK?

Program Device

In-System Verification

System Production

Altera Design Methodology

Design Entry Techniques

Copyright © 1998 Altera Corporation

Recommended Design Guidelines

Design Hierarchically

Evaluate Existing Macrofunctions, LPM functions,

Megafunctions, and AMPP functions

Use Dedicated Inputs for Control Signals

Reserve Resources in the Device

Compile Without Assignments Initially

Copyright © 1998 Altera Corporation

Design Hierarchically

Design separate functions in separate design files in order to yield the most control over the implementation of the design in the device

– Partition subdesigns at register outputs

Allows easier and more efficient assignments of logic options and synthesis styles

Allows easier and faster recompilation of alternative implementations

– Example: try different counter implementations by replacing the symbol or instance declaration

Copyright © 1998 Altera Corporation

Evaluate Existing Functions

LPM functions, megafunctions, and some old-style macrofunctions have been optimized for MAX devices to achieve the best possible performance and utilization from the MAX device architecture

All LPM functions and some megafunctions are parameterizable which allow easy design changes

These are described in more detail in the MAX+plus II

Help menu

– Go to Help and select either Megafunctions/LPM or Old-Style

Macrofunctions

Copyright © 1998 Altera Corporation

Evaluate Intellectual Property

Consider using MegaCore or AMPP (Altera Megafunctions Partners

Program) megafunctions

– Large, customized designs that have been optimized for MAX devices

OpenCore Support

– Functions can be evaluated in MAX+plus II

– Download MegaCore functions from Altera’s web site

– Download AMPP function from Partner’s web site

– Purchase is required in order to generate .pof file

More information:

– Refer to the AMPP Catalog (includes megafunction and partner descriptions) or

Microperipheral MegaCore Library Data Book ; request free copies from 1-888-3-

ALTERA

– Use Altera’s home page at http:\\www.altera.com to obtain the latest information about AMPP megafunctions and partners and about MegaCore functions

Copyright © 1998 Altera Corporation

Use Dedicated Inputs for Control Signals

Take advantage of the 4 dedicated inputs which can drive dedicated, low-skew, global signals designed for high fanout control signals (clocks, clears, output enables)

Logic-generated control signals may be used; however, there are some disadvantages if using them:

– More resources are required (logic cells, interconnect)

– More skew may result

– If the logic-generated control signals have high fan-out, the design may be more difficult to fit (compilation may fail)

Copyright © 1998 Altera Corporation

Reserve Resources in the Device

MAX 7000 Devices:

– Reserve 10% logic cells

– Reserve 5% pins

Allows MAX+plus II to fit the design during recompilation as changes are made

Allows MAX+plus II to fit the design during recompilation after assignments have been made:

– Pin assignments as necessary for board layout

– Logic Option and Synthesis Style assignments as necessary to meet performance requirements

Copyright © 1998 Altera Corporation

Compile Without Assignments Initially

Compile the project with default settings and without any assignments (pin, logic option, synthesis style, etc…) initially

Arbitrarily or globally selected assignments can prevent the design from fitting in the device

(compilation may fail)

Evaluate the results: resources (logic cell usage), performance, pin placement

– If these results are sufficient, no further work is necessary

– If optimization is required, see Resolving Fitting and

Performance Issues Sections

Copyright © 1998 Altera Corporation

Pin and Logic Cell Assignments

Make pin assignments only when necessary for board layout (as late as possible in the design cycle)

Make pin assignments after performance optimization

(see Resolving Performance Issues Section)

Use the pinout selected by MAX+plus II during the most recent compilation, if possible

– Under the Assign menu, select Back-Annotate Project, select Chips, Pins, &

Devices, click OK

• This will take the placement that MAX+plus II picked for the pins during the last compilation (.fit file) and assign them (in the .acf file)

Avoid making logic cell assignments

–

Logic cell assignments will likely cause a design with later changes to not compile

Copyright © 1998 Altera Corporation

Pin Assignment Guidelines

If the pinout selected by MAX+plus II cannot be used entirely, or if pins must be assigned prior to design creation, follow these guidelines for MAX 7000 devices:

– Assign speed critical control signals to dedicated inputs

– Assign output enables to appropriate locations

– Estimate fan-in to assign output pins to appropriate LAB

– Assign output pins in need of parallel expanders to

Macrocells #4-8 or Macrocell #12-16

Copyright © 1998 Altera Corporation

Control Signals

Assign speed critical control signals to dedicated inputs

– Assign clocks to global clock dedicated inputs

– Assign clear to global clear dedicated input

– Assign speed critical output enable to global OE dedicated input

Use Help menu in MAX+plus II to determine dedicated input pin numbers

– Help - Devices and Adapters - Select Device

Copyright © 1998 Altera Corporation

Assigning Output Enables

The Help topics for the MAX 7000 devices include a special column:

– OE MUX

Pin;LCell

The data in this column lists the possible sources for the global output enables (GOE1, GOE2…)

– Numbers before the / represent the global output enables that are fed by the pin in the corresponding Function column

– Numbers after the / represent the global output enables that are fed by the logic cell in the corresponding LCell column

Use this information to assign output enables to the appropriate locations

Copyright © 1998 Altera Corporation

Assigning Output Enables

Example - EPM7128

Function JTAG Pin LCell OE MUX LAB PQFP

Pin;Lcell (100 Pin)

I/O or Buried 16 4/6 A 94

– GOE4 can be driven by pin 94; GOE6 can be driven by LCell 16

The Floorplan Editor can help too:

A LAB A

7

8

5

6

3

4

1

2

13

14

15

16

9

10

11

12

Pin 94

Macrocell 16

Copyright © 1998 Altera Corporation

Estimate Fan-In to Assign Output Pins

Try to guess the fan-in (list of inputs or registers) contributing to the realization of each output

Use this to assign output pins in appropriate LABs

– The maximum number of signals that feed each LAB from the PIA is 36

• Maximum 36 input pins / registers(from other macrocells)

• For each signal from the PIA chosen, both the true and the inverted form are available in the LAB

– This will avoid having a fan-in greater than 36 into a LAB

• Prevents compilation errors; saves resources

Outputs / LABs fed by more than 36 inputs / registers will only compile if Multi-Level Synthesis = ON

– More macrocells will be needed for the design to break up the fan-in

Copyright © 1998 Altera Corporation

Outputs Using Parallel Expanders

Assign output pins which may need parallel expanders to pins adjacent to

Macrocells #4-8 or #12-16 within a LAB

These places are where you can borrow the largest number of parallel expanders

Copyright © 1998 Altera Corporation

Cannot borrow any parallel expanders

Can borrow up to 5 parallel expanders from Macrocell 1

Can borrow up to 10 parallel expanders from Macrocell 1 and

Macrocell 2

Can borrow up to 15 parallel expanders from

{ the three macrocells immediately above it

LAB A

Cannot borrow any parallel expanders

Macrocell 1

Macrocell 2

Macrocell 3

Macrocell 4

Macrocell 5

Macrocell 6

Macrocell 7

Macrocell 8

Macrocell 9

Macrocell 10

Macrocell 11

Macrocell 12

Macrocell 13

Macrocell 14

Macrocell 15

Macrocell 16

Altera Design Methodology

Resolving Fitting Issues

Copyright © 1998 Altera Corporation

Topics

Compiling a design in MAX+PLUS II

Resolving macrocell usage issues

Resolving routing issues

Copyright © 1998 Altera Corporation

The MAX+PLUS II Compilation Process

Extracts netlist of entire design hierarchy and checks for syntax error

Performs logic synthesis using synthesis logic option assignments in the .acf file

Builds file for simulation and timing analysis

Builds database for synthesis

Design Doctor checks for common design violations

Copyright © 1998 Altera Corporation

Checks for fit in selected device and partitions into multiple devices if necessary

Executes place & route algorithm and generates .rpt file summarizing device utilization and any fitting problems

Builds programming files

User can pause place & route routine to examine status

When Compiler Can’t Find a Fit

Dialog window opens with choice to override user assignments

Choosing Yes opens the Override User Assignments dialog box

Use message to help determine cause of problem

Partition into multiple devices

Choose a bigger device

Override user assignments

Copyright © 1998 Altera Corporation

Error Message

Choosing No terminates compilation and generates .rpt file

Error caused by design requiring too many macrocells and too many shared expanders

Error caused by routing resource issues (too much fan-in)

Copyright © 1998 Altera Corporation

Resolving Macrocell Usage Issues

Use Multi-Level Synthesis *

Turn OFF Parallel Expanders for all or part of the project

Use DFFs instead of latches

– May reduce macrocell fan-in (may reduce macrocell usage)

Use asynchronous instead of synchronous clear and preset

Try custom Fitter Settings *

Consider selecting a larger device

– Vertical migration allows pinout to be maintained

* Discussed later

Copyright © 1998 Altera Corporation

Resolving Routing Issues

Use Multi-Level Synthesis *

Use Dedicated Inputs / global signals for high fan-out signals

Change pin assignments

– See guidelines in Section 2

Use Fitter Settings Dialog Box *

– Try Advanced Try Harder/Longer Compilation Fitting *

Insert LCELLs to reduce fan-in and shared expanders per macrocell *

* Discussed later

Copyright © 1998 Altera Corporation

Logic Synthesis

Synthesis Styles

Standard Synthesis Multi-Level Synthesis

Partial), NOT Gate Push-Back,

All of the Stardard Synthesis

Global Signal, Hierarchical

Synthesis, Fast I/O, Insert Additional

Options plus: Ignore Soft Buffers,

Logic Cell, Minimization (Full and

Implement as Output of Logic Cell,

Decompose Gates, Reduce Logic,

Parallel Expanders, Slow Slew Rate,

Duplicate Logic Extraction,

Soft Buffer Insertion, Turbo Bit, Use

Refractorization, Subfactor

LPM for AHDL Operators, XOR

Extraction, Multi-Level Factoring,

Synthesis

Resynthesize Network, Register

Optimization

Copyright © 1998 Altera Corporation

Multi-Level Synthesis

MLS is a different type of synthesis which has been created to synthesize complex designs more efficiently

MLS can be selected from

Assign - Global Project

Logic Synthesis

– By default, MLS is turned OFF for MAX 7000 devices

• Standard Synthesis will be used

– By default, MLS is turned ON for

MAX 9000 devices

Copyright © 1998 Altera Corporation

Multi-Level Synthesis

Using MLS

Advantages Disadvantages

May reduce the number of logic cells required to implement the design

For some designs, may increase the number of macrocells required to implement the design

May reduce the number of shared expanders required (may increase performance and routability)

For some designs, may increase the number of shared expanders required to implement the design

Limits the amount of fan-in to each macrocell (may improve routability)

Increases compilation time

Copyright © 1998 Altera Corporation

Synthesis Example

Compile schematic below for any MAX 7000 device with

MLS = OFF (standard synthesis)

– Compilation will fail (the design will not fit)

– All 37 input pins try to feed one macrocell

– In MAX 7000, there are only 36 signals from the PIA into each LAB

With MLS = ON, the design will compile using 2 macrocells

– Macrocell #1 will have fan-in = 36; macrocell #2 will have fan-in = 2

– MLS limits the fan-in to 36 (changeable) for every macrocell

Copyright © 1998 Altera Corporation

Synthesis Example

The schematic below was compiled for a MAX 7000A device; the following resources were required:

– MLS on/off Logic Cells Shared Expanders

– OFF

– ON

2

5

8

0

Avg Fan-in

14.5

4.8

Copyright © 1998 Altera Corporation

Fitter Settings Dialog Box

Normal Fitting: This is the default option. MAX+plus

II may insert LCELLs after I/O pins with assignments if necessary to route the design. If LCELL insertion is not desired, select Custom Fitting and then toggle the

Auto LCELL Insertion Options.

Copyright © 1998 Altera Corporation

Advanced Try Harder

Advanced Try Harder/Longer

Compilation Fitting:

Recommendation: this option should only be used as a last resort to achieve a successful compilation. This option directs

MAX+plus II to cycle through a predefined suite of different Fitter settings to attempt to find a fit. This option will cause the Compiler to run for a longer period of time

(e.g., overnight) while attempting a fit. If you select this option and fitting is successful, you can manually specify the successful settings (listed in the report file) for

Custom Fitting to accelerate future recompilations.

Copyright © 1998 Altera Corporation

Custom Fitting

Custom Fitting: This option allows the user to specify new

Auto LCELL Insertion Options and Other Options (as a % of

Device Family Default).

Other Options: Only Expanders per Logic Cell and Fan-In per Logic

Cell apply to MAX 7000 devices.

The percentages can be decreased to help improve routability.

Copyright © 1998 Altera Corporation

Fitter Settings Dialog Box

Expanders per Logic Cell (0% to

1000%) :

- MAX 7000 default (100%): 1:1

- (MLS or Standard Synthesis)

This option allows the user to control the ratio of shareable expanders to macrocells for the design.

For example, if a design requires

100 macrocells in a MAX 7000 device, the maximum number of shared expanders used will be 100.

If the percentage is decreased to

50%, then 50 expanders may be used for a 100 macrocell design.

Copyright © 1998 Altera Corporation

Fitter Settings Dialog Box

Fan-In per Logic Cell (10% to

200%) :

- MAX 7000 default (100%): 36

Only available with MLS selected

This option allows the user to control what the maximum fan-in is for each macrocell. For example, if a MAX

7000 design is compiled with this option set to 50%, then the maximum fan-in to each macrocell will be 18.

Copyright © 1998 Altera Corporation

Using LCELLs

If utilization, performance, and/or routability are not achieved after trying techniques discussed so far, evaluate using LCELL primitives:

LCELL primitives may:

– Reduce fan-in

– Reduce shared expander use

– Reduce the number of macrocells required for the design

MLS must be turned on or off for the entire project;

LCELLs can be inserted manually (one at a time) to break up complex logic functions

Copyright © 1998 Altera Corporation

Alternative to Inserting LCELLs

When it is difficult to insert LCELL primitives (I.e. using other EDA tools), try:

– Hierarchical

Synthesis

– Implement as Output of Logic Cell

– Insert Additional

Logic Cell

Copyright © 1998 Altera Corporation

Using LCELLs - Example

The schematic below was compiled for a MAX 7000A device; the following resources were required:

– MLS ON

Logic Cells

– MLS OFF 2

– LCELL inserted after NOR gate 3

5

Shared Exp. Avg Fan-in

8 14.5

8

0

6.33

4.8

Copyright © 1998 Altera Corporation

Fitting Enhancement Summary

Reduce macrocell and routing resource usage

– Turn on MLS

– Use DFFs instead of latches

– Turn OFF Parallel Expanders for all or part of the project

– Use asynchronous instead of synchronous clear and preset

– Use Custom Fitter Settings

– Consider selecting a larger device

Increase routability

– Turn on MLS

– Use Dedicated Input/global buffer for high fan-out signals

– Change pin assignments

– Use Fitter Settings Dialog Box

– Manually insert LCELL primitives

Copyright © 1998 Altera Corporation

Still Doesn’t Fit?

Prepare information to work with Altera FAEs

– Record # and % of LCELLs and pins used in device

– Record all assignments made during compilation

– Record Error Summary Section in Report File

Report your findings to your Altera FAEs

Copyright © 1998 Altera Corporation

Laboratory Exercise 2

Go to Laboratory Exercise Manual and

Complete Exercise 2

Copyright © 1998 Altera Corporation

Altera Design Methodology

Resolving Performance Issues

Copyright © 1998 Altera Corporation

Device Timing

Design considerations

– Setup and hold times for signals coming on-chip

– Clock-to-out for signals going off-chip

– Maximum clock frequency, internal register-to-register performance setup time, hold time logic D Q clock frequency logic D Q clock-to-out time logic

Copyright © 1998 Altera Corporation

Device Timing - Setup and Hold

t

SU

= data delay - clock delay + register setup time t

HOLD

= clock delay - data delay + register hold time data delay

Register setup / hold time (see data book) logic

Clock delay - depends on resource used

– Dedicated Inputs drive global signals & PIA

– I/O pins drive PIA clock delay

Data delay - depends on

– Resource used for data input

•

Dedicated Inputs drive global signals & PIA

• Input pins drive PIA or macrocell registers directly via fast input path

– Proximity of input pin and register

D Q

Copyright © 1998 Altera Corporation

Device Timing - Clock-to-Out

t

CO

= clock delay + register clock-to-Q time + data delay

Register clock-to-Q time (see data book)

Clock delay - depends on resource used

– Dedicated Inputs drive global signals & PIA

– I/O pins drive PIA

Data delay - depends on

– Amount of logic between register and output pin

– Proximity of output pin and register

D Q data delay logic clock delay

Copyright © 1998 Altera Corporation

Device Timing - Clock Frequency

f

MAX

= 1 / (register clock-to-Q + data delay + register setup + clock skew)

Register clock-to-Q time (see data book)

Register setup time (see data book)

Clock skew - depends on resource used

– Dedicated Inputs drive global signals & PIA

– I/O pins drive PIA

Data delay - depends on

– Logic delay between registers

– Proximity of registers

D Q data delay logic D Q clock skew

Copyright © 1998 Altera Corporation

MAX+PLUS II Timing Analysis

Setup/Hold Matrix

– Setup/Hold time ( t

SU/HOLD

)

Delay Matrix

– Clock to Output delay ( t

CO

– Pin to pin delay ( t

PD

)

)

Registered Performance

– Maximum clocking frequency ( f

MAX

)

Delay Matrix

Setup/Hold Matrix

Registered

Performance

Copyright © 1998 Altera Corporation

MAX+PLUS II Compilation

The default MAX+PLUS II compilation is

– Unconstrained Synthesis

• No Parallel Expanders used

• Provides best ease-of-fit

– Unconstrained Place & Route

• Equal distribution of macrocells across device

• Prevents logic congestion that makes fitting harder

• Provides best second time fitting

Use synthesis and place & route control assignments to override the default compilation

– Synthesis logic options and pin/location/chip

Copyright © 1998 Altera Corporation

Analyzing t

SU/HOLD

Start analysis List delay path

Copyright © 1998 Altera Corporation

Can be located in

Floorplan Editor

Analyzing t

CO

and t

PD

List delay path

Start analysis

Copyright © 1998 Altera Corporation

Can be located in

Floorplan Editor

Analyzing f

MAX

f

MAX is the most important device timing parameter

Starts analysis f

MAX is displayed

Copyright © 1998 Altera Corporation

List critical paths

Delay paths are listed in descending order

Viewing the Delay Path

Highlight path

Locate path in Flooplan

Editor

Show path

Copyright © 1998 Altera Corporation

Tracing the Delay Path

Highlight source

Copyright © 1998 Altera Corporation

Highlight destination

Achieving Performance in MAX 7000

Copyright © 1998 Altera Corporation

Major Contributors to Long Delays

Excessive levels of logic

– Biggest contributor

Excessive loading (high fan-out)

– When a driving signal drives out to more than one LAB, the

PIA delay increases by 0.1 ns per additional LAB fan-out

– The 0.1 ns adder is the same for all devices

– To minimize the added delay, concentrate the destination macrocells into fewer LABs to minimize the number of LABs that are driven

Copyright © 1998 Altera Corporation

Improving T

SU

and T

CO

To improve t

SU

:

– Try turning on the Fast I/O logic option for the entire project or for individual input pins:

• The Fast I/O logic option will allow input pins to directly drive macrocell registers via the fast-input path

– Reduce amount of logic between the input pin and the register (or pipeline)

– Reduce fan-out

To improve t

CO

:

– Reduce amount of logic between the register and the output pin

(or pipeline)

– Place the register and the output pin as close as possible together

– Use the Global Clock

Copyright © 1998 Altera Corporation

Timing Example for EPM7064STC100-5

1 register Tsu

0.3 ns

0.6 ns

2.5 ns

2.8 ns

7.4 ns

Global

Thold Tco

2.2 ns

1.5 ns

0 ns

0 ns

0 ns

Clk?

10.1 ns no

5.4 ns

7.9 ns no yes

3.2 ns

3.2 ns yes yes

Fast I/O

Logic D Input

Option on off on off off

Location

LAB D

LAB A

LAB D

LAB A

LAB A

Q Output

Location

LAB D

LAB D

LAB D

LAB D

LAB D off LAB A LAB D

Additional LC between d and register?

no no no no yes

Additonal LC between register and q?

yes 2.8 ns 0 ns

16 registers with same d, clk inputs

7.8 ns yes all 2.9 ns all 0 ns all 3.2 ns yes

32 registers with same d, clk inputs all 3.0 ns all 0 ns all 3.2 ns yes off off

LAB A

LAB A

LAB C,D

LAB B, C, D

Copyright © 1998 Altera Corporation

If F

MAX

Requirements Are Not Achieved...

Turn on parallel expanders logic option for individual nodes/ subdesigns that need the increased speed

Advantage : Parallel expanders can increase the performance of complex logic functions

Drawback : More macrocells may be required to implement the project

Drawback : Macrocells that use parallel expanders must be placed physically together in the device which can reduce routability

Copyright © 1998 Altera Corporation

If F

MAX

Requirements Are Not Achieved...

Use the Global Signals (Dedicated Inputs)

– These signals are designed to provide low skew, high speed for high fan-out signals

– Minimize the number of control signals in the design and use the dedicated inputs to implement them

– Do not also use clock signal for data

Turn ON Multi-Level Synthesis

Use “Fast” synthesis style to use parallel expanders and other speed-enhancing MAX+PLUS II logic options

Divide large blocks of combinatorial logic/delay with registers (pipeline)

Copyright © 1998 Altera Corporation

Resolving Performance in MAX 7000

Use Dedicated Inputs

Turn on MLS

Turn on Fast Synthesis Style/ Parallel Expanders

For fast t

SU/HOLD try FAST I/O

For fast t

CO use macrocell closest to output pin

Reduce loading (fan-out) on critical signals

Use pipelining to break up combinatorial logic

Adjust Fitter Settings to reduce shared expanders and reduce fan-in

Copyright © 1998 Altera Corporation

Still Not Enough Performance?

Prepare information to work with Altera FAEs

– Record system requirements

– Record critical path performance numbers

– Record paths not meeting timing specifications

– Record all assignments made during compilation

Report your findings to your Altera FAEs

Copyright © 1998 Altera Corporation

Laboratory Exercise 3

Go to Laboratory Exercise Manual and

Complete Exercise 3

Copyright © 1998 Altera Corporation

SECTION 4

Programming MAX 7000 Devices

Copyright © 1998 Altera Corporation

SECTION 4 Outline

Programming Overview

Using Download Cables

– Laboratory Exercise #4

Using In-Circuit Testers

Using an Embedded Processor

In-System Programming Times

Copyright © 1998 Altera Corporation

Copyright © 1998 Altera Corporation

Programming Overview

Programming MAX Devices

MAX 5000 5.0 V internal EPROM

MA

MAX 7000

(includes

MAX

7000E)

5.0 V internal; except

EPM7032V

(3.3 V internal)

EEPROM

MAX 7000S 5.0 V internal EEPROM

ISP

MAX 7000A 3.3 V internal EEPROM

ISP

MAX 7000B 2.5 V internal EEPROM

ISP

MAX 9000

MAX 9000A

5.0 V internal EEPROM

ISP

MAX devices are nonvolatile

Security bit can be used to protect device information

EEPROM devices can be reprogrammed at least

100 times

EPROM devices can be reprogrammed at least

25 times

All MAX devices (except

BGA packages) can be programmed using a conventional stand-alone programmer

Copyright © 1998 Altera Corporation

Stand-Alone Programmers

Altera’s stand-alone programmer consists of:

– Programming software

• Included with MAX+plus II or

• Downloadable from Altera’s FTP site at ftp.altera.com in the /pub/misc directory: ASAP2.exe

– PLP6 (IBM PC-AT or compatible programming card)

– PL-MPU (Master Programming Unit)

– Adapter (refer to the Data Book or MAX+plus II on-line help)

Third-Party Programmers

– See the Data Book for a list of programmers

MAX devices can be programmed by a distributor

Copyright © 1998 Altera Corporation

Using Altera’s Stand-Alone Programmer

To program a MAX device, set up the MAX+plus II

Programmer:

–

1) Under the MAX+plus II menu, select Programmer (device and programming file will correspond to the project you have selected - these can be changed)

– 2) Under the Options menu, select Hardware Setup ; Auto-Setup ; Click OK

– 3) Select “

Program

”

Copyright © 1998 Altera Corporation

Select Auto-Setup or select the correct Hardware Type (LP4/LP6 +

PL-MPU)

What is ISP?

In-system programming refers to loading data into a device after it has already been mounted on a printed circuit board (PCB)

Mount Unprogrammed Program In-System

Copyright © 1998 Altera Corporation

Reprogram in the Field

ISP Benefits

Minimizes cost

– Sockets no longer needed

– Removes stand alone programming methodology

Minimizes device handling

– Prevents bent leads (most important for delicate QFP packages)

– Reduces possibility of ESD damage

Easy Prototyping

Improves manufacturing efficiency

– Integrated programming & testing using in-circuit testers

– No longer necessary to keep inventory of programmed devices

Easy field upgrades

– Design changes downloaded to system in the field quickly

– No need to return system for upgrades

Copyright © 1998 Altera Corporation

Using IEEE Std. 1149.1 JTAG Test Port

ISP through Joint Test Action Group (JTAG) test port is the industry standard

Ease of use

– Devices in the JTAG chain can be in-system programmed and tested with in-circuit testers

– All JTAG/ISP devices on board can be programmed using the same hardware

– Supports concurrent programming

• Concurrent programming supported within a device family

• Programming time for JTAG chain is on the order of the time for the biggest device in the chain

Copyright © 1998 Altera Corporation

Enabling JTAG Support

Altera Device Family JTAG pins (TDI, TMS, TCK, TDO)

MAX 7000S

MAX 7000A

MAX 7000B

Enable JTAG pins using Enable

JTAG Support option

Under the Assign menu select

Global Project Device Options

Recompile

Once enabled, the pins are not available as user I/O pins. If disabled, these pins are available as user I/O pins.

JTAG pins are dedicated.

MAX 9000

MAX 9000A

Copyright © 1998 Altera Corporation

Disabling JTAG Pins

Device

MAX 9000

MAX 9000A

-

Compiler

Option

TMS TCK TDI TDO

See

AN 100

See

AN 100

See

AN 100

Leave

Open

MAX 7000S

MAX 7000A

MAX 7000B

MAX 7000S

MAX 7000A

MAX 7000B

JTAG

Disabled

JTAG

Enabled

User

I/O

See

AN 100

User

I/O

See

AN 100

User

I/O

User

I/O

See

AN 100

Leave

Open

Copyright © 1998 Altera Corporation

MAX 7000AE Enhanced ISP Features

New ISP programming algorithm (simplified)

– Fewer instructions and addressing information

• Auto-increment counter added to supply addresses

– Improves programming by a factor of 2 to 10 times

ISP Done Bit

– Last bit programmed

– Prevents I/Os from driving out if ISP is interrupted

Pull-up resistor on I/O pins during ISP

– Allows for bus friendly interface

Copyright © 1998 Altera Corporation

Altera Programming Steps

(1) Enter programming mode

(2) Read silicon ID

(3) Bulk Erase device

(4) Program entire device

(5) Verify that bits are programmed correctly

(6) Exit programming mode

At power-up, a blank device has tri-stated I/Os

During programming, I/Os are tri-stated

Note: ISP is supported through Vcc-level programming voltage

– The devices generate a 12.0-V programming voltage internally to program, verify, and erase the EEPROM cells

– Eliminates need for external 12.0-V programming voltage

Copyright © 1998 Altera Corporation

TDI

ISP Implementation

JTAG/ISP Circuitry Block Diagram

Instruction Register

TMS

TCK

UPDATEIR

CLOCKIR

SHIFTIR

TAP

Controller SELECT

UPDATEDR

CLOCKDR

SHIFTDR

Instruction Decode

Bypass Register

Boundary-Scan Register

JTAG BST Circuitry

ISP Registers

ISP Address Shift Register

ISP Data Shift Registers

Data Registers

Copyright © 1998 Altera Corporation

TDO

ISP Implementation

JTAG/ISP Circuitry Block Diagram

(1) Using the circuitry for JTAG Boundary-Scan

Testing

– Used to test for opens and shorts on pins

– Supports BYPASS and other Boundary Scan modes

– See AN 39 (JTAG Boundary-Scan Testing in Altera Devices)

(2) Using the circuitry for In-System Programming

– ISP Instructions (Proprietary)

– TDI shifts in an instruction to Instruction Registers

– TDI shifts in an ISP address to ISP Address Registers

– TDI shifts in ISP data to ISP Data Registers

– The TAP Controller is a state machine that selects/enables the correct type of registers at the right time

Copyright © 1998 Altera Corporation

Programming Methods

Programming Platforms

Programming Support

Design

Prototyping

Production In-Field

Upgrades

Standard Programming

Hardware

.pof, .jbc, or .jam

Download Cables

MAX+plus II with .pof;

.jbc (or .jam)

In-Circuit Testers

.svf, .jam, or .jbc

Embedded Processor .jbc (or .jam)

ISP!

Copyright © 1998 Altera Corporation

Programming Files

Format

POF (Programming

Object File)

Binary

JBC (Jam

Byte Code)

File

Binary

JAM File

(use JBC if

SVF (Serial

Vector Format) possible) File

ASCII text file ASCII text file

Contents

How to create

Platforms supported

Programming data

Created automatically during compilation in

MAX+plus II

Stand alone programmers, download cable with

MAX+plus II

Programming data and algorithm

Programming data and algorithm

Programming data and algorithm

Can be created from

Can be created from

Can be created from a POF a POF a POF

All platforms All platforms In-circuit testers

Copyright © 1998 Altera Corporation

What is Jam

TM

?

Jam Device Programming & Test Language

– An Interpreted Language Optimized for Programming

Devices via the JTAG Port

Created by Altera

Submitted to JEDEC for standardization on

September 23, 1997

Freely licensable

– http://www.jamisp.com

Compatible with all existing JTAG ISP-capable PLDs

Copyright © 1998 Altera Corporation

Why Altera Created Jam

Smaller file format

– Other file formats are too large

• Complicates production

• Impractical for in-field upgrades

Achieve shorter programming times

– Time is money on expensive in-circuit testers

– Programming can take longer using other file formats

Create a standard

– Beyond JTAG, other approaches are all different

– Inconsistent file formats: POF, JED, SVF, PCF, ASC, etc.

– Other solutions are vendor- & platform-specific

Copyright © 1998 Altera Corporation

Jam Features

Contains all programming information

– Design data and programming algorithm

Small file size

– Supports algorithmic instructions (I.e. looping, branching)

Faster programming times

– Reads silicon ID of device to choose appropriate algorithm

Vendor-independent

Platform-independent

Supports existing and future products

Extendible to test

Supports several data formats (I.e. binary, hex)

Open standard

Copyright © 1998 Altera Corporation

File Sizes for ISP (One 256-Macrocell Device)

50 MB

Data Only Algorithm Included

790 KB

Approximate

File Size

17 KB

120 KB

33 KB 42 KB

Copyright © 1998 Altera Corporation

File Sizes for ISP (Five 256-Macrocell Devices)

170 MB

Data Only Algorithm Included

Approximate

File Size

85 KB

600 KB

46 KB

61 KB

2.6 MB

Copyright © 1998 Altera Corporation

Use of Jam

Jam Composer (writes Jam files)

– Each silicon vendor creates their own Jam files

– For Altera devices, the Jam Composer is MAX+plus II

Jam Player

– Freely licensable compiled executable for PC/Parallel Port

– Freely licensable source code

– 2 implementations

• Compiled (Byte-Code)

• Interpreted (ASCII)

Jam Language Specification

– Freely distributed as public domain via the internet

• http://www.jamisp.com

– Submitted for standardization

Copyright © 1998 Altera Corporation

Jam Byte-Code Flow

PLD

Vendor-

Specific

PLD Vendor- &

Platform-

Independent

Jam

Composer

.jbc

Jam

Byte-Code

Player

Platform-Specific

TMS

TCK

TDI

TDO

TDI

TMS

TCK

TDO

Any JTAG

Device

Target

Device

Use Jam Byte-Code files for all new designs

Smaller file sizes

Faster programming times

Copyright © 1998 Altera Corporation

JTAG Chain

TMS

TDI

TCK

TDO

Any JTAG

Device

ASCII Jam Flow

PLD

Vendor-

Specific

PLD Vendor- &

Platform-

Independent

Jam

Composer

.jam

ASCII

Jam

Player

Platform-Specific

TMS

TCK

TDI

TDO

TDI

TMS

TCK

TDO

Any JTAG

Device

Target

Device

ASCII Jam files are supported for backward compatibility

Parsing ASCII characters is slower

ASCII characters require more memory for storage

Copyright © 1998 Altera Corporation

JTAG Chain

TMS

TDI

TCK

TDO

Any JTAG

Device

Jam Support on Standard Programmers

Standard Programmers to support Jam

– Support available now:

• Advin Systems

• Xeltek

• Hi-Lo Research Systems

• System General

• SMS

• Stag Programmers

– Data I/O, BP Microsystems, ICE Technical : TBD

Jam allows immediate support for a new device

– No need to wait for next upgrade

– No need to download new upgrade version

– Programming algorithms and support available from day of device introduction

Copyright © 1998 Altera Corporation

Creating a Jam or SVF File

(1) To access this dialog box: open the Compiler or

Programmer window and go to the File menu and select

Create Jam or SVF File…

(2) Describe the JTAG chain of devices according to board layout

(3) After selecting OK,

1 .jbc, .jam or .svf file

(depending on output file type) will be created representing all devices in the chain

Copyright © 1998 Altera Corporation

Updating a Jam File

With a given .pof file, different (newer) devices can be programmed using the same file

– I.e. a given .pof file generated for a MAX 7000S device can be used to program its MAX 7000A counterpart

– The system (I.e. the latest version of MAX+plus II) looks up the silicon ID of the device, chooses the algorithm, and programs the device

To program a newer device with Jam, the Jam file

(.jam or .jbc) must be updated to include the algorithm for the newer device

– Use the version of MAX+plus II that supports the newer device to re-generate the Jam file from the older .pof file

– Re-compiling the design is NOT necessary

Copyright © 1998 Altera Corporation

SVF2Jam

SVF2Jam conversion utility is available from http://www.jamisp.com

This utility demonstrates the truly vendorindependence of the Jam language

SVF2Jam does a literal translation of each SVF statement to the corresponding Jam statement

– For an optimized Jam file, use the device vendor’s Jam

Composer

Copyright © 1998 Altera Corporation

Using Download Cables

Copyright © 1998 Altera Corporation

Why Use a Download Cable?

A download cable channels programming data between a PC or UNIX workstation and the circuit board

Design changes downloaded directly to devices

– Easy prototyping

– Multiple design iterations accomplished quickly

Copyright © 1998 Altera Corporation

Download Cables

ByteBlaster

™

ByteBlasterMV

™

BitBlaster

™

Type

Platform

Supported

Power Supply

Voltage

Required

Programming

Time

Parallel Cable Parallel Cable

PC PC

5.0 Volts 5.0 Volts or

3.3 Volts

Serial Cable

PC or UNIX

Workstation

5.0 Volts

Programming

Files

Supported

Fast Fast

.pof, .jbc, .jam

(concurrent programming of multiple devices supported with .jbc/.jam)

.pof, .jbc, .jam

(concurrent programming of multiple devices supported with .jbc/.jam)

Slow

(ByteBlasters are 4 times faster)

.pof, .jbc, .jam

(concurrent programming of multiple devices supported with .jbc/.jam)

Copyright © 1998 Altera Corporation

Getting Started

Refer to the following sections in the MAX+plus II

Getting Started Manual:

– Additional Windows NT Installation Steps

• Installing the Altera ByteBlaster driver

– Installing the ByteBlaster on a PC

– Installing the BitBlaster on a PC or UNIX Workstation

Getting Started Manual can be accessed from http://www.altera.com

Copyright © 1998 Altera Corporation

Connecting the Download Cable

.pof, .jbc

or .jam

Same Schematic for ByteBlaster, ByteBlasterMV, and

BitBlaster Cables VCC

VCC 1k

VCC

Download

Cable

VCC 1k 1k

MAX+plus II

Programmer

or System

Prompt on PC or

Workstation

1k

1

3

5

2

4

6

TMS

TCK

TDI

TDO

Any JTAG

Device

Download Cable Female Pin Names

Pin

1

JTAG Mode

TCK

7 8

9 10

10-Pin Male

Header

TMS

TCK

TDI

TDO

MAX 9000

MAX 9000A

MAX 7000S

MAX 7000A

MAX 7000B

6

7

8

9

2

3

4

5

10

GND

TDO

VCC

TMS

No Connect

No Connect

No Connect

TDI

GND

TMS

TCK

TDI

TDO

Any JTAG

Device

Copyright © 1998 Altera Corporation JTAG Chain

Connecting the Download Cable

The circuit board must supply VCC and ground to the cable

If using the BitBlaster or ByteBlaster cable, the cable’s VCC pin must be connected to 5.0 V supply

– If programming a 3.3 or 2.5 V Altera device (I.e. MAX 7000A/

MAX 7000B), the device has 5.0 V tolerant inputs

– The cable’s 5.0 V output will not harm these devices

– Pullup resistors should be connected to 5.0 V supply

If using the ByteBlasterMV cable, the cable’s VCC pin can be connected to 5.0 or 3.3 V supply

When connecting the cable to a chain of more than 4 devices, Altera recommends buffering the TDI, TMS, and TCK pins with an on-board buffer

Copyright © 1998 Altera Corporation

Using MAX+plus II as the Interface

To program a single device, set up the MAX+plus II Programmer to program 1 device

– 1) Under the MAX+plus II menu, select Programmer

– 2) Under the Options menu, select Hardware Setup - select cable click OK

–

3) Check device and programming file displayed select “

Program

”

• Programming file can be a .pof, .jbc or .jam file (Recommendation: use .jbc)

Make sure the correct file and device are displayed.

Double click on each field to change selection.

Copyright © 1998 Altera Corporation

Make sure the correct cable is selected with the correct port information.

Using MAX+plus II as the Interface

To program multiple devices without Jam , set up the

MAX+plus II Programmer to program a chain of devices:

1) Under the

MAX+plus II menu, select Programmer

2) Under the JTAG menu select

Multi-Device

JTAG Chain

3) Under the JTAG menu select

Multi-Device JTAG

Chain Setup or double click on this field

Copyright © 1998 Altera Corporation

Using MAX+plus II as the Interface

To program multiple devices without Jam :

–

4) List the device names and associated programming files in the same order they appear on the board; click on Save JCF to save the information to a .jcf file; click OK

– 5) Select “

Program

” in the Programmer window

Devices that are not Altera devices and devices that cannot be programmed or configured through the

JTAG chain should not have a programming file associated with them

(<none>). These devices will be put in

BYPASS mode.

Detects JTAG chain information and performs integrity test

Copyright © 1998 Altera Corporation

Using MAX+plus II as the Interface

To program multiple devices with Jam :

(1) To access this dialog box: open the Compiler or Programmer window and under the File menu select Create Jam or SVF File…

(2) If you have created a .jcf file already, recall it in this dialog box by selecting Restore JCF . Otherwise, describe the JTAG chain of devices according to board layout.

(3) Make sure the output file type is .jbc (or .jam). Click OK ; 1 .jbc or .jam file will be created representing all devices in the chain.

(Recommendation: use .jbc)

Note: If you do not want to program/re-program some devices in the chain, simply do NOT select a programming file for those devices (<none>)

Copyright © 1998 Altera Corporation

Using MAX+plus II as the Interface

To program multiple devices with Jam :

(5) Under the JTAG menu make sure Multi-Device JTAG

Chain is NOT selected

(6) Select the .jbc or .jam file

( double click on the File : field and browse directories until you find the .jbc or .jam file)

(7) Select Program

Copyright © 1998 Altera Corporation

Using a Command to Program with Jam

(1) Generate 1 .jbc (recommended) or .jam file for the devices in the JTAG chain

(2) Download the Jam Developer’s kit from the internet at http://www.jamisp.com

– Includes the Jam Player

(3) In order to be able to execute Jam from any directory, set the directory path in your system where the Jam Player is located

– jbi.exe (Jam Byte-Code Player - recommended) or

– jam.exe (ASCII Jam Player)

Note: This method allows the user to program a device outside of MAX+plus II. However,

MAX+plus II is needed to compile for and generate a .jbc/.jam file for an Altera device

Copyright © 1998 Altera Corporation

Executing the Jam Player

jbi or jam [-h] [-v] [-d <var=val>] [-p <port>] [-s <port>] [-m

<mem>] <filename>

– -h

– -v

Help message

Verbose messages

– -d Initialize variable to specified value

• See next slide for variables and values

– -p

– -s

Parallel port number or address (for ByteBlaster)

Serial port name (for BitBlaster)

– -m Fixed memory buffer size in bytes

• By default, memory is allocated dynamically

– <filename> is the file (I.e. filename.jbc)

Suggestion: type jbi -h to get the above definitions and ensure the system recognizes the Jam Player

Copyright © 1998 Altera Corporation

Executing the Jam Player

jbi or jam [-h] [-v] [-d <var=val>] [-p <port>] [-s <port>]

[-m <mem>] <filename>

-d Variables and values

–

DO_ERASE

• 0

• 1

Do not perform a bulk erase

Perform a bulk erase

–

DO_BLANKCHECK

• 0 Do not check the erased state of the device

• 1 Check the erased state of the device

– DO_PROGRAM

• 0 Do not program the device

• 1 Program the device

–

DO_VERIFY

• 0

• 1

Do not verify the device

Verify the device

–

DO_READ_UES

• 0 Do not read the JTAG UES code

• 1 Read and report the UES code

– DO_SECURE

• 0

• 1

Do not set the security bit

Set the security bit if the corresponding .pof sets the security bit

– DO_SECURE_ALL

• 0 Do not set the security bit

• 1 Set the security bit overriding

.pof settings

Copyright © 1998 Altera Corporation

Executing the Jam Player: Notes

The only required flags are -d and the filename

– The other flags are optional

Variables that are not initialized after a -d flag are set to 0

The order of variables in the initialization list is not important

Each variable set after the -d flag applies to ALL devices specified in the .jbc or .jam file

The Jam Player can process only 1 .jbc or .jam file at a time

Copyright © 1998 Altera Corporation

Example Command

Copyright © 1998 Altera Corporation

Laboratory Exercise 4

Go to Laboratory Exercise Manual and

Complete Exercise 4

Copyright © 1998 Altera Corporation

Using In-Circuit Testers

Copyright © 1998 Altera Corporation

Bed-Of-Nails Testers

Literally this is an array of hundreds of electrical nails that forces values on board traces and compares results

Able to support testing and programming all devices

(JTAG and non-JTAG)

Price: approximately $200,000 to million dollars

– Tester time is critical: cost $5-$15/minute

Manufacturers:

– HP, Genrad, Teradyne

Test fixture (~$5000) needed for each board for testing/programming

Copyright © 1998 Altera Corporation

JTAG Testers

Uses 4 (or 5) pin interface to test all JTAG Devices

Usually runs with a PC controlling the test

Can only support testing and programming JTAG devices

Price: approximately $5,000 to $20,000 (less expensive than Bed-Of-Nails tester)

Manufacturers

– Asset InterTech, JTAG Technologies, Goepel

Copyright © 1998 Altera Corporation

SVF File

The SVF (Serial Vector Format) file is an industry standard ASCII file that was created for JTAG testing

– For ISP, it includes both programming data and algorithm

– Read directly by many JTAG and Bed of Nails in-circuit testers

Undesirable features for ISP:

– Does not support looping / branching for repetitive sequences

– Does not support data compression for sparse data

– File size can be large

SVF (Higher level)

SIR 10 TDI (01A);

RUNTEST 53 TCK;

SDR 320 TDI

(FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF

FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF

FFFDFDFFF);

Copyright © 1998 Altera Corporation

One command in the

SVF represents a single IR scan or DR scan

SVF File

The SVF specification does not support branching based on silicon ID

– SVF by itself cannot read the silicon ID of a device and choose the correct programming algorithm

– Other programming methods CAN branch based on silicon

ID (I.e. stand-alone programmers, Jam)

When a SVF file is used, the Altera device MUST be a “F”-suffix device (i.e. EPM7128STC100-10F)

What is a “F”-suffix device?

Copyright © 1998 Altera Corporation

F vs. Non-F Devices

“ F” indicates a fixed or constant programming algorithm

– 2 given non”F” devices (i.e. 2 EPM7128STC100-10 devices) are each subject to:

• A unique silicon ID

• A unique die revision

• A unique programming pulse time / algorithm

– “F”-suffix devices are screened for a pre-selected programming pulse time value

– Non”F” devices have adaptive programming algorithms for the fastest possible programming times

Since SVF cannot support adaptive algorithms, “F”suffix devices MUST be used

“F” devices are available for all ISP capable devices

Copyright © 1998 Altera Corporation

SVF vs. Jam

Many in-circuit tester manufacturers have announced commitment to support Jam

If the tester supports Jam, use Jam to program the devices

– “F” devices do NOT need to be purchased

– If the tester supports Jam Byte-Code, use that instead of

ASCII Jam

If the tester does NOT support Jam, use SVF

– “F” devices MUST be purchased

Copyright © 1998 Altera Corporation

Support Schedule

Vendor

Hewlett Packard

Teradyne

Genrad

Corelis

Asset InterTech

JTAG Technologies

Goepel

Copyright © 1998 Altera Corporation

Supported File Formats

SVF supported (via PCF conversion);

Jam for “F” devices: Q1 1999

SVF and ASCII Jam supported

SVF supported

SVF supported; Jam: TBD

SVF supported; Jam: Q4 1998

SVF supported; Jam: TBD

SVF supported; Jam: Q4 1998

Using an In-Circuit Tester for Programming

(1) Generate either the Jam or the SVF file

– Use Jam if the tester supports it

(2) If necessary, a utility can convert the file

– For example, SVF2PCF utility generates HP-PCF vectors from SVF file for Hewlett Packard testers

(3) Add vectors for board test into the Jam, SVF,

PCF... file

(4) The tester programs the Altera devices through the JTAG ports and tests the board

Copyright © 1998 Altera Corporation

Programming Flow

MAX+plus II ATE

Jam or

SVF

Utility

SVF2PCF

SVF2ASC

Vendor Proprietary

Vector Format

JTAG Chain

Copyright © 1998 Altera Corporation

TMS

TCK

TDI

TDO

TMS

TCK

TDI

TDO

Any JTAG

Device

MAX 9000

MAX 9000A

MAX 7000S

MAX 7000A

MAX 7000B

TMS

TCK

TDI

TDO

Any JTAG

Device

Using an Embedded Processor

Copyright © 1998 Altera Corporation

Embedded Processor ISP Flow

MAX+plus II

Jam

Composer

Resides on system memory or can be transferred from external storage

.jbc

Customer End Product

Processor

Jam

Player

TMS

TCK

TDI

TDO

TMS

TCK

TDI

TDO

Any JTAG

Device

JTAG Chain

TMS

TCK

TDI

TDO

MAX 9000

MAX 9000A

MAX 7000S

MAX 7000A

MAX 7000B

Any JTAG

Device

Copyright © 1998 Altera Corporation

Using a Processor for Programming

(1) Generate the .jbc (recommended) or .jam file

(2) Download the Jam Developer’s Kit from http://www.jamisp.com which includes the source code

(3) Modify the ANSI C source code

– jbistub.c for Jam Byte-Code (recommended)

– jamstub.c for ASCII Jam

– See next slides

(4) Compile the code

(5) C-routine and .jbc or .jam file can be stored on disk or in on-board memory

– .jbc / .jam file can be converted into a .hex file to be used to program a EPROM or FLASH device

(6) C-routine reads the file and programs ISP capable devices

Copyright © 1998 Altera Corporation

Embedded Code

Jam Player (C-routine) is split into two sections

– I/O section

– Main program

I/O section is customized for the selected system

– Writing error messages to a file rather than the monitor

– Choosing different I/O pins for ISP

– Placing Jam file in FLASH rather than on a disk

Main program does not require alteration

– Processes Jam instructions

– Generates programming signals

Jam Player Size

– Varies significantly based on processor

– For PC, ASCII Jam Player is 103 KB; Jam Byte-Code is 68 KB

Copyright © 1998 Altera Corporation

Generating Programming Signals

Jam Player

I/O Functions jbistub.c file (Jam Byte-Code) jamstub.c file (ASCII Jam)