Next Generation Nanotechnoloy Electronic Design

advertisement

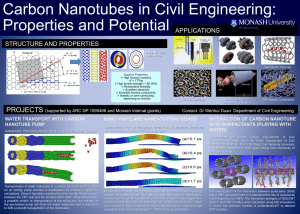

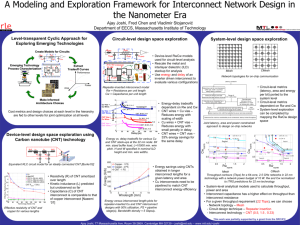

Next Generation Carbon Nanotube Based Electronic Design Outline 1 2 3 4 5 6 7 Introduction Carbon Nanotubes (CNT) Interconnect Buffering CNT Interconnect for Timing Optimization Preliminary Results for CNT Buffering Fabrication Variation Aware CNT Buffering Fabrication Variation Aware CNT based VLSI Synthesis Conclusion 2 Interconnect Delay Dominates Copper 3 Copper resistivity (uOhms.cm) Bottleneck of Prevailing Copper Technology Copper Resistivity Copper interconnect technology has its fundamental physical limit, interconnect delay due to ever increasing wire resistivity has greatly limited the circuit miniaturization. 6 5 4 3 2 1 0 80 65 45 32 22 14 Technology node (nm) 4 Copper Global Interconnect Delay Driver Load Interconnect delay (ps) Copper Global Interconnect Technology node (nm) Minimum pitch (nm) 68 210 52 156 1500 40 120 1000 32 96 22 66 18 54 14 42 3500 3000 2500 2000 500 0 68 59 52 45 40 36 32 28 25 22 20 18 16 14 Technology node (nm) Interconnect RC delay (ps) for a 1 mm length minimum pitch Cu global wire (ITRS 2007) 5 Carbon Nanomaterial Carbon Nanotube (CNT) is one of the material of carbon as well as Graphenes. Graphenes CNT 6 Nobel Prize The Nobel Prize in Physics 2010 was awarded jointly to Andre Geim and Konstantin Novoselov “ for groundbreaking experiments regarding the two-dimensional material graphene" 7 SWCNTs: Single-Walled Carbon Nanotubes Single-walled carbon nanotube (SWCNT) can be envisioned as a rolled up graphene sheet into a seamless cylinder with fullerene caps. Diameters of SWCNTs are typically 0.5 to 3nm. CNT lengths range from less than 100 nm to several centimeters 8 Bundled SWCNTs 1nm 0.32nm Bundled SWCNTs consist of a bundle of parallel single SWCNTs 9 Mean Free Path of CNT 40nm 1000nm All particles suffer from collisions with other particles such that their path through space is very short for high densities. This typical path length is called the mean free path. The longer mean free path results in smaller resistivity. Resistivity 𝜌 ∝ 1 𝑙 10 Advantage of CNT Compared to Cu Properties CNT Cu Mean Free Path 1000𝑛𝑚 40𝑛𝑚 Max. Current Density 1010 𝐴/𝑐𝑚2 106 𝐴/𝑐𝑚2 Thermal Conductivity 6000𝑊/𝑚𝐾 400𝑊/𝑚𝐾 Copper interconnect technology is approaching its fundamental physical limit, and issues such as electromigration and ever increasing wire resistivity which has greatly limited the circuit miniaturization. Carbon nanotube (CNT) interconnect is a promising replacement material. CNT has better performance in mean free path, maximum current density and thermal conductivity. 11 CNT Fabrication Process: Chemical Vapor Deposition (CVD) CVD uses carbon precursors from gas phase to form CNTs that takes place at relatively low temperatures (500–1000 °C), providing great scalability and controllability. Thus, CVD is regarded as a highly promising CNT growth technique for the purpose of large-scale synthesis 12 Quartz Wafer-Scale Aligned CNT Growth Quartz wafer with catalyst Aligned CNT growth 13 Transfer CNTs from Quartz Wafers to Silicon Wafers CNT transfer technique using Thermal Release Tape. (a) SEM of CNTs on quartz. (b) 100 nm of Au evaporated on 4” quartz wafer after CNT growth. (c) Thermal release tape is applied to the Au film and the tape/Au bilayer is peeled off. (d) SiO2/Si Wafer with transferred Au after tape release at 120oC. (e) SEM images of SWNTs transferred from quartz to 50 nm SiO2 on Si after gold etching (KI/I2). (f) (f) Si wafer after substrategated CNFET fabrication. • N. Patil, A. Lin, E. Myers, H.-S. P.Wong, and S. Mitra, “Integrated waferscale growth and transfer of directional carbon nanotubes and misalignedcarbon-nanotube-immune logic structures,” in Proc. Symp. VLSI Technol., pp. 205–206, 2008. 14 CNT Fabrication Orientation Control Surface structures of substrate and state of gas flow can partially decide the growth orientation of SWCNTs under a suitable temperature range 15 CNT Fabrication Length Control To selectively grow SWCNT arrays with certain length, one easy way is confining the spatial termination position of growing SWCNTs, which means to obstruct the growth of SWCNTs by instantaneously stopping the catalysts' activity possibility with additional barriers at a certain position. Rogers et al. introduce a layer of amorphous SiO2 onto quartz surface, and SWCNTs terminated at the edge of the SiO2 layer because of the surface relief 16 CNT Fabrication Density Control Keeping catalyst activity; multiple-cycle CVD growth; adding in new catalysts to grow new SWCNTs 17 CNT Variations in Density Aligned arrays of CNTs can take full advantage of the superior transport characteristics of CNTs, and therefore are considered to be most suitable for high-performance circuit applications. The density of variations will impact on the resistance and capacitance parameters of bundled CNTs 18 CNT Fabrication Diameter Control Depend on the diameter of catalysts and Temperature 19 CNT Variation in Diameter 20 Mis-alignment CNT State-of-the-art CNT growth techniques today are able to produce CNTs with >99.9% alignment for low density. In our design, high density CNTs are desired and misalignment becomes an important issue. 21 Outline 1 2 3 4 Introduction Carbon Nanotubes (CNT) Interconnect Buffering CNT Interconnect for Timing Optimization Preliminary Results for CNT Buffering 5 Fabrication Variation Aware CNT Buffering 6 Fabrication Variation Aware CNT based VLSI Synthesis 7 Conclusion 22 Overview of Bundled SWCNTs Circuit Model Driver Load Bundled SWCNTs interconnect 𝑅𝑑𝑟 𝐶𝑑𝑟 𝑅𝑐_𝑢𝑝 𝑅𝑄 𝑏𝑢𝑛𝑑𝑙𝑒 2 𝐶𝐸 𝑏𝑢𝑛𝑑𝑙𝑒 ∙ 𝑙 2 𝑅𝑆𝑏𝑢𝑛𝑑𝑙𝑒 𝑙 𝑅𝑄 𝑏𝑢𝑛𝑑𝑙𝑒 2 𝐶𝐸 𝑏𝑢𝑛𝑑𝑙𝑒 ∙ 𝑙 2 𝑅𝑐_𝑑𝑜𝑤𝑛 𝐶𝑙𝑜𝑎𝑑 23 Quantum Resistance of Single SWCNT If the size of the structure is of the same scale as the mean free path of an electron, Ohm’s law may not apply, there exist quantum effects Quantum resistance (the lowest possible resistance of an isolated SWCNT) ℎ 𝑅𝑄 = 2 = 6.45𝑘Ω 4𝑒 ℎ =6.626×10−34 J·s -- Plank’s constant 𝑒 =1.602×10−19 Coulombs -- the electronic charge 24 Scattering Resistance of Single SWCNT Scattering unit resistance ℎ 𝑅𝑆 = 2 = 6.45𝑘Ω/𝜇𝑚, when 𝑙 > λ 4𝑒 𝜆 For simplicity, define 𝑅𝑆 = 0, when 𝑙 ≤ λ Total resistance of a single SWCNT 𝑅𝑖𝑠𝑜𝑙𝑎𝑡𝑒𝑑 = 𝑅𝑄 + 𝑅𝑆 𝑙 ℎ =6.626×10−34 J·s -- Plank’s constant 𝑒 =1.602×10−19 Coulombs -- the electronic charge 𝜆 is the mean free path of electrons for a CNT 𝑙 is the length of CNT 25 Resistance of Bundled SWCNTs Total resistance of bundled SWCNTs 𝑅𝑏𝑢𝑛𝑑𝑙𝑒 = 𝑅𝑖𝑠𝑜𝑙𝑎𝑡𝑒𝑑 /𝑁𝑐𝑛𝑡 𝑅𝑖𝑠𝑜𝑙𝑎𝑡𝑒𝑑 is total resistance of a single SWCNT 𝑁𝑐𝑛𝑡 is the number of SWCNTs contained in the bundle For global interconnect, the scattering resistance dominates, thus, 𝑅𝑏𝑢𝑛𝑑𝑙𝑒 = 𝑅𝑖𝑠𝑜𝑙𝑎𝑡𝑒𝑑 /𝑁𝑐𝑛𝑡 =𝑅𝑆 𝑙/𝑁𝑐𝑛𝑡 26 Contact Resistance Imperfect contacts between copper and carbon nanotubes CNT interconnect layer Contact resistance Some research groups have accomplished to fabricate the contact resistances ranging from a few hundred ohms to a few kilohms 27 Quantum Capacitance of Single SWCNT and Bundled SWCNTs Quantum unit capacitance 𝐶𝑄 = 2𝑒 2 ℎ𝑣𝑓 where 𝑣𝑓 is the Fermi velocity (𝑣𝑓 ≈ 8 × 105 𝑚/𝑠) Since an SWCNT has four conducting channels, the net quantum capacitance of a single SWCNT is 𝐶𝑄𝐶𝑁𝑇 = 4𝐶𝑄 Quantum capacitance of a bundled SWCNTs is 𝐶𝑄𝑏𝑢𝑛𝑑𝑙𝑒 = 𝑁𝑐𝑛𝑡 𝐶𝑄𝐶𝑁𝑇 28 Electrostatic Capacitance of Single SWCNT and Bundled SWCNTs Electrostatic unit capacitance 2𝜋𝜖 𝐶𝐸 = −1 𝑐𝑜𝑠ℎ (𝑦/𝑑) FastCap is used to calculate the electrostatic capacitance of each single SWCNT 29 Effective Capacitance of Bundled SWCNTs The effective capacitance of an SWCNT bundle interconnect (Cbundle) is given by the series combination of its electrostatic capacitance and quantum capacitance. As shown in left figure, the effective SWCNT bundle capacitance is nearly equal to its electrostatic capacitance and the effect of the quantum capacitance is small. N. Srivastava, H. Li, F. Kreupl and K. Banerjee, “On the Applicability of Single-Walled Carbon Nanotubes as VLSI Interconnects,” IEEE Transactions on Nanotechnology, vol. 8, no. 4, pp. 542–559, 2009. 30 Inductance of Single SWCNT and Bundled SWCNTs Kinetic inductance of single SWCNT ℎ 𝑖𝑠𝑜𝑙𝑎𝑡𝑒𝑑 𝐿𝐾 = 2 8𝑒 𝑣𝐹 Magnetic inductance of single SWCNT 𝜇 𝑦 𝑖𝑠𝑜𝑙𝑎𝑡𝑒𝑑 −1 𝐿𝑀 = 𝑐𝑜𝑠ℎ ( ) 2𝜋 𝑑 Inductance of bundled SWCNTs 𝐿𝑏𝑢𝑛𝑑𝑙𝑒 = 𝐿𝐾 𝑖𝑠𝑜𝑙𝑎𝑡𝑒𝑑 + 𝐿𝑀 𝑖𝑠𝑜𝑙𝑎𝑡𝑒𝑑 𝑁𝑐𝑛𝑡 31 Inductive Effect of Bundle SWCNTs is Not Important 1 𝑅𝑑𝑟 𝐶𝑙 < 𝑅𝑙𝐶𝑙 < 𝐿𝐶𝑙 2 𝑅𝑑𝑟 𝐶𝑙 where Rdr is the driver impedance and R, C and L are the per unit length interconnect resistance, capacitance and inductance. (1/2)𝑅𝑙𝐶𝑙 𝐿𝐶𝑙 The above inequality never holds, inductance can be ignored. N. Srivastava, H. Li, F. Kreupl and K. Banerjee, “On the Applicability of Single-Walled Carbon Nanotubes as VLSI Interconnects,” IEEE Transactions on Nanotechnology, vol. 8, no. 4, pp. 542–559, 2009. 32 Bundled SWCNTs Interconnect Model CNT interconnect layer Driver Load Bundled SWCNTs interconnect 𝑅𝑄𝑏𝑢𝑛𝑑𝑙𝑒 𝑅𝑑𝑟 𝑅𝑐,𝑑𝑜𝑤𝑛𝑠𝑡𝑟𝑒𝑎𝑚 2 𝑅𝑆 𝑏𝑢𝑛𝑑𝑙𝑒 𝐶𝑄𝑏𝑢𝑛𝑑𝑙𝑒 𝐶𝐸𝑏𝑢𝑛𝑑𝑙𝑒 𝑅𝑆 𝑏𝑢𝑛𝑑𝑙𝑒 𝑅𝑆 𝑏𝑢𝑛𝑑𝑙𝑒 𝐶𝑄𝑏𝑢𝑛𝑑𝑙𝑒 𝐶𝑄𝑏𝑢𝑛𝑑𝑙𝑒 𝐶𝐸𝑏𝑢𝑛𝑑𝑙𝑒 𝐶𝐸𝑏𝑢𝑛𝑑𝑙𝑒 𝑅𝑄𝑏𝑢𝑛𝑑𝑙𝑒 2 𝑅𝑐,𝑢𝑝𝑠𝑡𝑟𝑒𝑎𝑚 𝐶𝑙𝑜𝑎𝑑 33 Bundled SWCNT Interconnect π Model 𝑅𝑑𝑟 𝐶𝑑𝑟 𝑅𝑐,𝑑𝑜𝑤𝑛𝑠𝑡𝑟𝑒𝑎𝑚 𝑅𝑄𝑏𝑢𝑛𝑑𝑙𝑒 + 𝑅𝑆 𝑏𝑢𝑛𝑑𝑙𝑒 𝑙 𝐶𝑄𝑏𝑢𝑛𝑑𝑙𝑒 ∙ 𝐶𝐸 𝑏𝑢𝑛𝑑𝑙𝑒 ∙ 𝑙 2(𝐶𝑄𝑏𝑢𝑛𝑑𝑙𝑒 + 𝐶𝐸𝑏𝑢𝑛𝑑𝑙𝑒 ) 𝐶𝑄𝑏𝑢𝑛𝑑𝑙𝑒 ∙ 𝐶𝐸 𝑏𝑢𝑛𝑑𝑙𝑒 ∙ 𝑙 2(𝐶𝑄𝑏𝑢𝑛𝑑𝑙𝑒 + 𝐶𝐸𝑏𝑢𝑛𝑑𝑙𝑒 ) 𝑅𝑐,𝑢𝑝𝑠𝑡𝑟𝑒𝑎𝑚 𝐶𝑙𝑜𝑎𝑑 34 Bundled SWCNT Global Interconnect Simplified π Model 𝑅𝑑𝑟 𝐶𝑑𝑟 𝑅𝑆𝑏𝑢𝑛𝑑𝑙𝑒 𝑙 𝑅𝑐,𝑑𝑜𝑤𝑛𝑠𝑡𝑟𝑒𝑎𝑚 𝐶𝐸 𝑏𝑢𝑛𝑑𝑙𝑒 ∙ 𝑙 2 𝑅𝑐,𝑢𝑝𝑠𝑡𝑟𝑒𝑎𝑚 𝐶𝐸 𝑏𝑢𝑛𝑑𝑙𝑒 ∙ 𝑙 2 𝐶𝑙𝑜𝑎𝑑 35 Outline 1 2 3 4 Introduction Carbon Nanotubes (CNT) Interconnect Buffering CNT Interconnect for Timing Optimization Preliminary Results for CNT Buffering 5 Fabrication Variation Aware CNT Buffering 6 Fabrication Variation Aware CNT based VLSI Synthesis 7 Conclusion 36 Delay for A Circuit Delay = all Ri all Cj downstream from Ri Ri*Cj Elmore delay to n1 R(B)*(C1+C2) Elmore delay to n2 R(B)*(C1+C2)+R(w)*C2 37 Buffer Insertion For Delay Reduction 38 Why Buffers Can Reduce Delay? (Rd,Cd) 𝑟𝑙 𝑅𝑑 𝐶𝑑 𝑐𝑙 2 𝑟𝑙/2 𝑅𝑑 𝑐𝑙 2 (Rb,Cb) (Rd,Cd) (CL) 𝐶𝐿 𝑐𝑙 𝑡𝑢𝑛𝑏𝑢𝑓 = 𝑅𝑑 𝑐𝑙 + 𝐶𝐿 + 𝑟𝑙( + 𝐶𝐿 ) 2 Suppose that 𝑅𝑑 = 𝑅𝑏 , 𝐶𝑑 = 𝐶𝑏 ∆𝑡 = 𝑡𝑏𝑢𝑓 − 𝑡𝑢𝑛𝑏𝑢𝑓 = 𝑅𝑏 𝐶𝑏 − 𝑟𝑐𝑙 2 /4 𝑐𝑙 4 𝐶𝑑 𝑡𝑏𝑢𝑓 = 𝑅𝑑 𝑐𝑙 4 𝑅𝑏 𝐶𝑏 (CL) 𝑟𝑙/2 𝑐𝑙 4 𝑐𝑙 4 𝐶𝐿 𝑐𝑙 𝑟𝑙 𝑐𝑙 𝑐𝑙 𝑟𝑙 𝑐𝑙 + 𝐶𝑏 + + 𝐶𝑏 + 𝑅𝑏 + 𝐶𝐿 + ( + 𝐶𝐿 ) 2 2 4 2 2 4 ∆𝑡 𝑙 39 CNT Buffering and Copper Buffering CNT interconnect layer Copper interconnect layer Copper buffering CNT buffering 40 Existing Works Some existing works consider the CNT interconnect or buffered CNT interconnect, however, they only use a two pin mode interconnect model None of the existing works consider the deployment of CNT into VLSI physical design • • • • N. Srivastava, H. Li, F. Kreupl and K. Banerjee, “On the Applicability of SingleWalled Carbon Nanotubes as VLSI Interconnects,” IEEE Transactions on Nanotechnology, vol. 8, no. 4, pp. 542–559, 2009. A. Nieuwoudt and Y. Massoud, “On the optimal design, performance, and reliability of future carbon nanotube-based interconnect solutions,” IEEE Transactions on Electron Devices, vol. 55, no. 8, pp. 2097–2110, 2008. G. Close and H.-S. Wong, “Assembly and electrical characterization of multiwall carbon nanotube interconnects,” IEEE Transactions on Nanotechnology, 2008. A. Naeemi and J. D. Meindl, “Design and performance modeling for singlewall carbon nanotubes as local, semi-global, and global interconnects in gigascale integrated systems,” IEEE Transactions on Electron Devices, vol. 54, no. 1, pp. 26–37, 2008. 41 Problem Formulation Timing Constrained Minimum Cost Buffering for Carbon Nanotube Interconnects: Given a binary routing tree with 𝑛 candidate buffer locations in carbon nanotube interconnect layer, a buffer library and a set of candidate buffer positions, to compute a buffer assignment solution such that the timing constraint is satisfied, and the total buffer cost is minimized. 42 Solution Characterization To model effect to downstream, a candidate solution is associated with • v: a node • C: downstream capacitance • Q: required arrival time • W: cumulative buffer cost 43 Candidate Buffering Solutions 44 Dynamic Programming (DP) Start from sinks Candidate solutions are generated Three operations – Add Wire – Insert Buffer – Merge Candidate solutions are propagated toward the source Solution Pruning 45 Solution Propagation: Add Buffer (𝑄 𝛾 ′ , 𝐶 𝛾 ′ , 𝑊 𝛾 ′ ) (𝑄 𝛾 , 𝐶 𝛾 , 𝑊(𝛾)) 46 Solution Propagation: Add Wire (𝑄 𝛾𝑣 , 𝐶 𝛾𝑣 , 𝑊 𝛾𝑣 ) 𝑢 (𝑄 𝛾𝑢 , 𝐶 𝛾𝑢 , 𝑊 𝛾𝑢 ) 𝑅 𝑢, 𝑣 , 𝐶(𝑢, 𝑣) 𝑣 47 Solution Propagation: Add Driver (𝑄 𝛾 ′ , 𝐶 𝛾 ′ , 𝑊 𝛾 ′ ) (𝑄 𝛾 , 𝐶 𝛾 , 𝑊(𝛾)) 48 Branch Merge (𝑄 𝛾 , 𝐶 𝛾 , 𝑊(𝛾)) (𝑄 𝛾1 , 𝐶 𝛾1 , 𝑊 𝛾1 ) (𝑄 𝛾2 , 𝐶 𝛾2 , 𝑊 𝛾2 ) 49 Exponential Runtime 16 solutions 8 solutions 4 solutions 2 solutions n candidate buffer locations lead to 2n solutions 50 Too Many Solutions Needs solution pruning for acceleration Two candidate solutions – (v, c1, q1,w1) – (v, c2, q2,w2) Solution 1 is inferior to Solution 2 if – c1 c2 : larger load – and q1 q2 : tighter timing – and w1 w2: larger cost 51 Pruning (Q1,C1,W1) inferior/dominated if C1 C2,W1 W2 and Q1 Q2 (Q2,C2,W2) 52 Outline 1 2 3 4 5 6 7 Introduction Carbon Nanotubes (CNT) Interconnect Buffering CNT Interconnect for Timing Optimization Preliminary Results for CNT Buffering Fabrication Variation Aware CNT Buffering Fabrication Variation Aware CNT based VLSI Synthesis Conclusion 53 Experimental Environment The proposed carbon nanotube interconnect based timing driven minimum cost buffer insertion algorithm is implemented in C and tested on a machine with 3.40GHz Intel Pentium CPU and 3GB memory. Simulation 1: Timing constrained minimum cost buffering Simulation 2: Timing minimization without considering cost 54 Experimental Setup – Layer RC Information Cu Bundled SWCNT (1000 SWCNTs) Resistance (Ω) 14.50 6.45 Capacitance (fF) 0.16 0.16 𝜌𝑙 𝐴 CNT density = 1000/(33 × 88) = 0.34𝑛𝑚2 𝑅𝑐𝑢 = Contact resistance is set to 100Ω 55 Experimental Setup – Buffer Library Property BUF_X1 BUF_X2 BUF_X4 BUF_X8 BUF_X16 Resistance (Ω) 2310.0 1201.0 618.9 315.5 159.6 Intrinsic delay (ps) 0.21 Capacitance (fF) Linear fitting 2.93 Area (nm2) 15197.6 Property INV_X1 RC1846.0 0 Resistance (Ω) 0.44Reference 0.88 driver A2.91 B 2.87 30395.2 60790.4 INV_X2 INV_X4 Buffer w/ unknown 3.51 capacitance 1.76 2.87 121580.8 INV_X8 Reference driver C A’ 976.5 514.8 B’ 270.2ref 2.87 C 243161.6 INV_X16 139.7 C’ Capacitance (fF) 0.44 0.87 1.74 3.49 6.97 Intrinsic delay (ps) 0.59 0.62 0.61 0.61 0.61 Area (nm2) C 10115.6 20231.2 40462.4 80924.8 161849.6 56 Experimental Setup – Global Nets Our experiments are performed to 500 global nets. Due to the lack of industrial nets in 22nm technology, we scale wire lengths of old technology nets to 22nm technology. 57 Experiment 1 Timing constrained minimum cost buffering Timing minimization without considering cost 58 Experiment 1 Results of 500 Nets On Average (Normalized) Chart Title 1.2 1 Ratio 0.8 0.6 0.4 0.2 0 CNT w/o contact resistance Area # Buffers CNT w/ 100 Ohms contact resistance Delay # Solutions Cu CPU 59 Experiment 1 Results on Five Representative Nets Test cases CNT w/o contact resistance CNT w/ contact resistance (100Ω) Cu 1 2 3 4 5 Average Area (nm2) 318666.0 394605.0 222543.0 50578.0 40462.4 205370.88 # Buffers 7 9 5 3 2 5.2 Delays (ps) 754 1128 676 1019 722 859.8 Area (nm2) 379359.0 263151.0 222543.0 80924.8 40462.4 197288.04 # Buffers 7 9 5 4 2 5.4 Delays (ps) 762 1130 691 927 736 849.2 Area (nm2) 955997.0 612308.0 475433.0 202312.0 91040.4 467418.08 # Buffers 18 19 12 10 5 15.0 Delays (ps) 766 1180 702 994 870 902.4 60 Area and Delay Trade-off Curves for Cu and CNT 61 Experiment 2 Timing constrained minimum cost buffering Timing minimization without considering cost 62 Experiment 2 Results on Five Representative Nets Test cases CNT w/o contact resistance CNT w/ contact resistance (100Ω) Cu 1 2 3 4 5 Average Area (nm2) 3307950.0 3738560.0 2477160.0 3039520.0 1945290.0 2913844.00 # Buffers 50 61 44 44 32 46.0 Delays (ps) 376 724 314 249 188 370.2 Area (nm2) 1463910.0 1995870.0 1408250.0 1458970.0 1094230.0 1555162.00 # Buffers 36 36 31 24 18 30.8 Delays (ps) 423 797 347 302 229 419.6 Area (nm2) 2851920.0 3794220.0 2269040.0 2872350.0 2142860.0 3040382.00 # Buffers 65 67 56 48 36 59.4 Delays (ps) 479 877 382 363 276 475.4 63 Observations In order to achieve the similar delay, the CNT buffering saves more than 50% buffer area over copper buffering The total number of buffers in CNT buffering is much (about 2X) smaller than that of copper buffering thanks to the fact that wire resistivity of bundled SWCNTs is much lower than that of copper for global interconnect The contact resistance does not have significant impact on the performance for CNT interconnect timing constrained minimum cost buffering CNT buffering always outperforms the copper buffering in terms of timing and buffer area CNT buffering can reduce timing by up to 32% comparing to copper buffering for buffering timing minimization without considering cost 64 Summary of CNT Buffering Carbon nanotube interconnects have become a promising replacement material for copper interconnects thanks to their superior conductivity. This work develops the first timing driven buffer insertion technique for carbon nanotube interconnects. In the experimental results, it demonstrates that with the same timing constraint, CNT buffering can save over 50% buffer area compared to copper buffering. In addition, CNT buffering can effectively reduce the delay by up to 32% without considering cost. This work is published in ISVLSI2014. Lin Liu, Yuchen Zhou and Shiyan Hu, “Buffering Single Walled Carbon Nanotube Bundle Interconnects for Timing Optimization”, to appear in Proceedings of IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 2014. 65 Outline 1 2 3 4 5 6 7 Introduction Carbon Nanotubes (CNT) Interconnect Buffering CNT Interconnect for Timing Optimization Preliminary Results for CNT Buffering Fabrication Variation Aware CNT Buffering Fabrication Variation Aware CNT based VLSI Synthesis Conclusion 66 Fabrication Imperfectness • It is very difficult for today’s CNT processing to produce perfect CNTs. • New design techniques must be employed that are immune to these inherent CNT imperfections. • These new design techniques must be compatible with VLSI processing, and must have minimal impact on existing VLSI design flows. 67 Existing Works Some research works studied the variations of CNT and some proposed robust design considering CNFET Some research works studied the copper variation based buffer insetion • • • • • Jie Zhang, et al, "Carbon Nanotube Robust Digital VLSI," Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on , vol.31, no.4, pp.453,471, April 2012 Patil, N.; Lin, A.; Myers, E.R.; Ryu, Koungmin; Badmaev, A.; Chongwu Zhou; Wong, H. -S P; Mitra, S, "Wafer-Scale Growth and Transfer of Aligned Single-Walled Carbon Nanotubes," Nanotechnology, IEEE Transactions on , vol.8, no.4, pp.498,504, July 2009 Jie Zhang; Patil, N.P.; Hazeghi, A.; Wong, H. -S P; Mitra, S, "Characterization and Design of Logic Circuits in the Presence of Carbon Nanotube Density Variations," Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on , vol.30, no.8, pp.1103,1113, Aug. 2011 Raychowdhury, A.; De, V.K.; Kurtin, Juanita; Borkar, S.Y.; Roy, K.; Keshavarzi, A., "Variation Tolerance in a Multichannel Carbon-Nanotube Transistor for High-Speed Digital Circuits," Electron Devices, IEEE Transactions on , vol.56, no.3, pp.383,392, March 2009 Jinjun Xiong; Lei He, "Probabilistic Transitive-Closure Ordering and Its Application on Variational Buffer Insertion," Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on , vol.26, no.4, pp.739,742, April 2007 68 CNT Fabrication Variations Distribution CNT diameter variations (d) Normal CNT length variations (l) Normal CNT counts (Ncnt) Normal 𝜇𝑑 = 1.3𝑛𝑚 𝜎𝑑 = 0.2𝑛𝑚 𝜇𝑙 𝜎𝑙 = 𝜇𝑙 cos 10° 𝜇𝑁𝑐𝑛𝑡 = 1000 𝜎𝑁𝑐𝑛𝑡 = 22 CNT distance to ground (y) Normal 𝜇𝑦 𝜎𝑦 = 0.1𝑛𝑚 Jie Zhang; Patil, N.P.; Hazeghi, A.; Wong, H. -S P; Mitra, S, "Characterization and Design of Logic Circuits in the Presence of Carbon Nanotube Density Variations," Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on , vol.30, no.8, pp.1103,1113, Aug. 2011 http://www.sciencedirect.com/science/article/pii/S1369702113000205 71 Parameters Variations 𝑅𝑑𝑟 𝑅𝑆𝑏𝑢𝑛𝑑𝑙𝑒 𝑙 𝑅𝑐,𝑑𝑜𝑤𝑛𝑠𝑡𝑟𝑒𝑎𝑚 𝐶𝐸 𝑏𝑢𝑛𝑑𝑙𝑒 ∙ 𝑙 2 𝐶𝑑𝑟 𝑅𝑐,𝑢𝑝𝑠𝑡𝑟𝑒𝑎𝑚 𝐶𝐸 𝑏𝑢𝑛𝑑𝑙𝑒 ∙ 𝑙 2 𝐶𝑙𝑜𝑎𝑑 𝑙, 𝑁𝑐𝑛𝑡 , 𝑦 and 𝑑 follow normal distribution In a SWCNT bundle that contains large amount of CNTs in parallel; according to Central Limit Theorem, we have 𝑅𝑆𝑏𝑢𝑛𝑑𝑙𝑒 ~𝑁 𝜇𝑅𝑏𝑢𝑛𝑑𝑙𝑒 , 𝜎𝑅𝑏𝑢𝑛𝑑𝑙𝑒 2 𝑆 𝐶𝐸 ~𝑁(𝜇𝐶𝐸 , 𝜎𝐶𝐸 2) 𝑆 70 Uncertainty Aware Design Idea 1. According to the distribution of each variable, generate large amount of test cases with deterministic values; 2. For each deterministic test case, perform the deterministic algorithm; 3. If the yield rate is large enough, the current solution is return; else generate new test cases and repeat 2. 71 Uncertainty Aware Design on CNT Buffering Algorithm Given the maximum and minimum of each variable Generation the value of the variables by 𝑉=𝛽𝑉𝑚𝑎𝑥+(1−𝛽)𝑉𝑚𝑖𝑛, 𝛽 is initialized to 0 Generate large amount of test cases given normal distribution of each variables Run the deterministic CNT buffering algorithm Timing constraints yield rate is satisfied No Update 𝛽 = 𝛽 + ∆ Yes Return the buffering solution 72 Outline 1 2 3 4 5 6 7 Introduction Carbon Nanotubes (CNT) Interconnect Buffering CNT Interconnect for Timing Optimization Preliminary Results for CNT Buffering Fabrication Variation Aware CNT Buffering Fabrication Variation Aware CNT based VLSI Synthesis Conclusion 73 Traditional Physical Synthesis of Copper Based Design Given: nets, a set of cells and constraints of timing, power and area. Placement: determine the physical location of each cell Routing: given a placement solution, determine the routing path of every cell Buffer insertion: given a routing solution, insert buffer to reduce the delay Layer assignment: determine the layer of interconnects 74 Fabrication Variation Aware CNT based VLSI Physical Synthesis Placement Routing CNT Co-design Layer Assignment No Converged? CNT Buffering Yes Output 75 Cross-Entropy (CE) Method CE is developed as an efficient estimation technique for rare-event probabilities in discrete event simulation systems and is adapted for use in optimization. Two phases of CE: 1.Generate a random data sample according to a specified mechanism. 2.Update the parameters of the random mechanism based on the data to produce a "better" sample in the next iteration. 76 Placement: SimPL Initial Placement Global Placement Post Global Placement Uniformly Distributed Placement Look-ahead Legalization (Upper Bounds) Last Upper-bound Placement Pseudonets linking each cell to its legalized location Final Legalization and Detailed Placement B2B Graph Update Linear System (Lower Bounds) Legal Placement Netlist Graph (B2B Net Model) Linear System No Converged? (Δ HPWL) Yes No Converged? (Gap+ΔHPWL) Yes 77 Initialize PDF for each cell Cross-Entropy Based Flowchart Pull cell to available placement according to PDF of each cell using Monte-Carlo method Update PDF for cells associated with survivals Keep Samples With Smaller Gaps Sample 1 (Upper Bounds) Sample 2 (Upper Bounds) Sample N (Upper Bounds) B2B Graph Update Linear System (Lower Bounds) B2B Graph Update Linear System (Lower Bounds) B2B Graph Update Linear System (Lower Bounds) Copper based Routing Copper based Routing Copper based Routing CNT Co-Design Layer Assignment CNT Co-Design Layer Assignment CNT Co-Design Layer Assignment CNT Buffering CNT Buffering CNT Buffering Yes No Converged? Finish 78 CNT for Security? CNT technologies can be utilized to design Physically Unclonable Function (PUF) for security applications. Based on a physical system (e.g. random variation during an IC fabrication process) For use in crypto applications Easy to construct and evaluate a PUF Very hard (“impossible”) to produce two PUFs with similar challenge-response behavior Challenge PUF Response 79 One Example C D Q 0 x No change 1 1 1 1 0 0 1 0 1 0 D 1 0 Q 1 0 C If top path is faster, the D = 0, C = 1, output Q = 0; If bottom path is faster, the D = 1, C = 0, output Q remains at 1. The fabrication variation will generate unpredictable and random output. 80 Basic Properties of PUF Minimum requirements: For two random PUFs, difference between expected responses to same challenge, should be large For single random PUF, difference between two measured responses to same challenge should be small For single random PUF, uncertainty about response to challenge is large 81 PUFs Classification Delay based intrinsic PUFs Utilize the propagation delay between identical circuits in order to derive a response e.g. Arbiter PUF, Ring oscillator PUF Memory based intrinsic PUFs Produce an output response based on the unpredictable startup state of feedback-based CMOS memory structures e.g. SRAM PUF 82 Arbiter PUF Initial design switch block: e.g. two MUX arbiter: e.g. a latch or a flip-flop n switch blocks 2n “different” delays Lee, J.W.; Lim, D.; Gassend, B.; Suh, G.E.; van Dijk, M.; Devadas, S., "A technique to build a secret key in integrated circuits for identification and authentication applications," in VLSI Circuits, 2004. Digest of Technical Papers. 2004 Symposium on , pp.176-179, 2004 83 SRAM PUF Which state right after power-up? depends on physical mismatch between M2 and M4 𝑄 𝑸 1 0 0 1 2 possible stable states J. Guajardo, S. S. Kumar, G. 1. Schrijen , and P. Tuyls, "FPGA Intrinsic PUFs and Their Use for IP Protection ," in CHES, 2007, pp. 63-80. 84 CNT Fabrication Process CNT fabrication process at the Future Carbon GmbH in Bayeruth, Germany 85 CNT Density Variation CNT density is defined as the CNT count per unit width (1um). CNT density variation is caused by randomness of CNT manufacturing process. Spacing between alligned CNTs varies significantly, leading to huge CNT density variation. (i-1,j) (i,j) (i-1,j+1) (i,j+1) (i+1,j) Bundled CNT interconnect (i+1,j+1) 86 Parallel Bundled SWCNTs Unit A Timing B comparator Parallel Bundled SWCNTs Unit Output 1/0 If signal A arrives first, the output is 1; if signal B arrives first, the output is 0. The two set of bundled SWCNTs are generated in exactly same environment. 87 Using Bundled SWCNT Interconnects to Design PUF Challenge Parallel Bundled SWCNTs Unit Parallel Bundled SWCNTs Unit Parallel Bundled SWCNTs Unit Parallel Bundled SWCNTs Unit Response 88 CNFET Based PUF CNT based PUFs aim to achieve better reliability, low energy and power consumption compared to that of silicon based PUFs. 89 PUFs Properties Challenge x Evaluatable PUF Response y y = PUF (x) is easy Unique PUF(x) contains some unique information Reproducible PUF() has only small error Unclonable Hard to make PUF’(x) given PUF(x) Unpredictable Hard to find yN=PUF(xN) given other x, y pairs One-way Given y and PUF(), cannot find x Tamper evident Tampering changes PUF() 90 Conclusion Carbon nanotube interconnects have become a promising replacement material for copper interconnects thanks to their superior conductivity. We develop the first carbon nanotubes based fabrication variation aware VLSI physical synthesis targeting timing optimization. We develop the first timing driven buffer insertion technique for carbon nanotube interconnects. Uncertainty aware method and probabilistic method are proposed to handle fabrication variations. CNT technologies can be used for security applications (PUF designs). 91 92