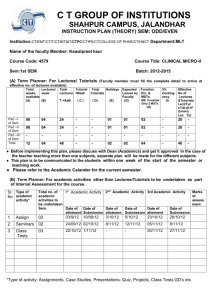

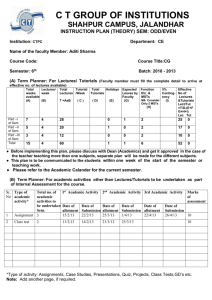

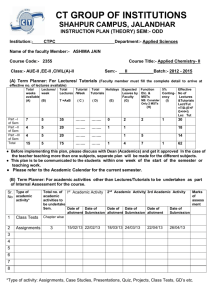

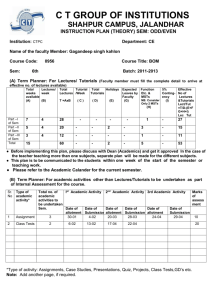

ct group of institutions shahpur campus, jalandhar instruction plan

advertisement

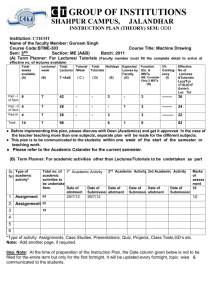

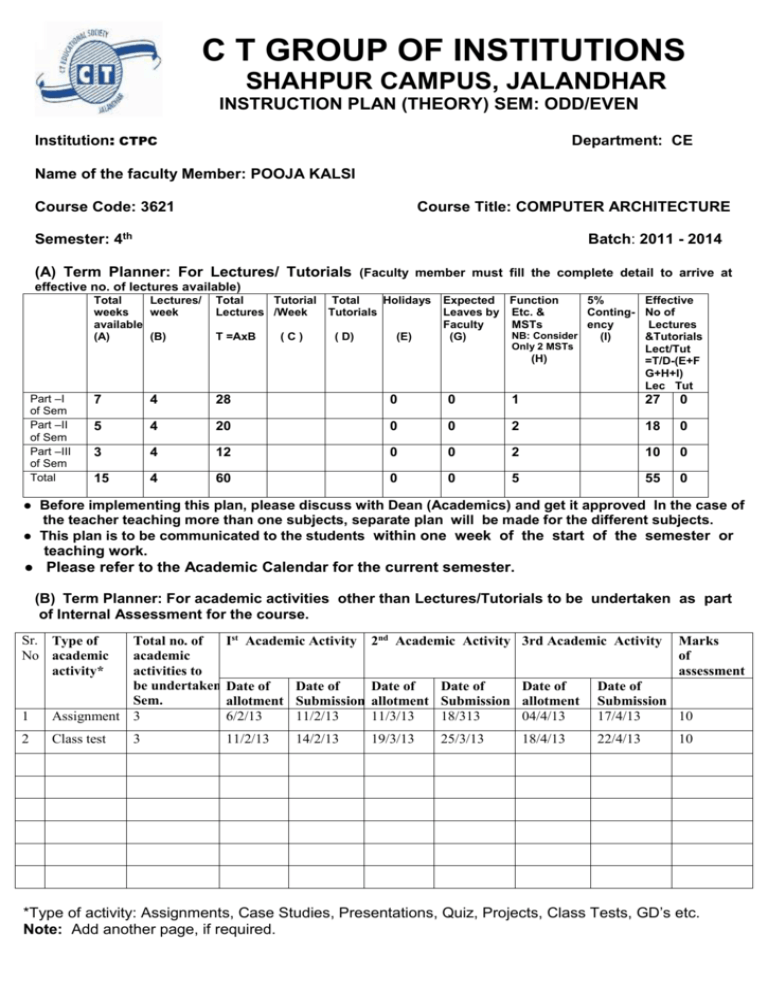

C T GROUP OF INSTITUTIONS SHAHPUR CAMPUS, JALANDHAR INSTRUCTION PLAN (THEORY) SEM: ODD/EVEN Institution: CTPC Department: CE Name of the faculty Member: POOJA KALSI Course Code: 3621 Course Title: COMPUTER ARCHITECTURE Semester: 4th Batch: 2011 - 2014 (A) Term Planner: For Lectures/ Tutorials (Faculty member must fill the complete detail to arrive at effective no. of lectures available) Part –I of Sem Part –II of Sem Part –III of Sem Total Total Lectures/ weeks week available (A) (B) Total Tutorial Lectures /Week 7 4 28 0 0 1 27 0 5 4 20 0 0 2 18 0 3 4 12 0 0 2 10 0 15 4 60 0 0 5 55 0 T =AxB (C) Total Holidays Tutorials ( D) (E) Expected Function 5% Effective Leaves by Etc. & Conting- No of Faculty MSTs ency Lectures NB: Consider (G) (I) &Tutorials Only 2 MSTs Lect/Tut (H) =T/D-(E+F G+H+I) Lec Tut ● Before implementing this plan, please discuss with Dean (Academics) and get it approved In the case of the teacher teaching more than one subjects, separate plan will be made for the different subjects. ● This plan is to be communicated to the students within one week of the start of the semester or teaching work. ● Please refer to the Academic Calendar for the current semester. (B) Term Planner: For academic activities other than Lectures/Tutorials to be undertaken as part of Internal Assessment for the course. Ist Academic Activity 1 Total no. of academic activities to be undertaken Sem. Assignment 3 Date of Date of Date of Date of Date of allotment Submission allotment Submission allotment 6/2/13 11/2/13 11/3/13 18/313 04/4/13 Date of Submission 17/4/13 10 2 Class test 11/2/13 22/4/13 Sr. Type of No academic activity* 3 14/2/13 2nd Academic Activity 3rd Academic Activity 19/3/13 25/3/13 18/4/13 Marks of assessment 10 *Type of activity: Assignments, Case Studies, Presentations, Quiz, Projects, Class Tests, GD’s etc. Note: Add another page, if required. Imp. Note: At the time of preparation of the Instruction Plan, the Date column given below is not to be filled for the entire term but only for the first fortnight. It will be updated every fortnight, topic wise & communicated to the students. INSTRUCTION PLAN BEFORE MST-I Sr. No CHAPTER 1 Data Representation 2 Central Processing Unit 3 Arithmetic Operations TEACHING SCHEDULE Sr. No 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 LECTUREWISE BREAKAGE Date 21/1/13 22/1/13 23/1/13 Binary to decimal 24/1/13 Binary to hexadecimal 28/1/13 Hexadecimal to decimal 29/1/13 1’s Complement 30/1/13 2’s Complement 30/1/13 BCD code 4/2/13 Gray Code 5/2/13 Introduction General Register Organization 6/2/13 7/2/13 Stack Organization 11/2/13 Types of Stack Organization 12/2/13 Instruction Formats 13/2/13 Addressing Modes Types of Addressing Modes/Test 14/2/13 18/2/13 Introduction to RISC 20/2/13 Introduction to CISC 21/2/13 CISC architecture 25/2/13 Pipeline processing 26/2/13 Introduction 27/2/13 Addition 26/2/13 Subtraction 28/2/13 Multiplication 4/3/13 Division 5/3/13 Algorithms 6/3/13 Revision Data Types Number System Note : Add another page, if required. No. of Mode of Lect. Delivery* Reqd. 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture 1 Lecture Students Role** G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. G.D. INSTRUCTION PLAN BEFORE MST-II Sr. No CHAPTER 4 5 Input-Output Organisation Memory Organization TEACHING SCHEDULE Sr LECTUREWISE BREAKAGE No Date 1 2 3 4 5 6 7 Input-output interface I/O bus and interface for module I/ O vs. memory bus Isolated Vs memory mapped IP modes of data transfer first in first out buffer priority interrupt 11/3/13 12/3/13 13/3/13 14/3/13 18/3/13 19/3/13 20/3/13 No. of Lec. Reqd. 1 1 1 1 1 1 1 8 9 10 11 12 Daisy chaining priority parallel priority interrupt/Test priority encoder interrupt cycle Direct memory access, DMA controller DMA transfer Memory hierarchy Main memory Memory address map 21/3/13 25/3/13 26/3/13 28/3/13 1/4/13 2/4/13 3/4/13 4/4/13 8/4/13 9/4/13 13 14 15 16 17 Note : Add another page, if required. Mode of Delivery* Students Role** Lecture Lecture Lecture Lecture Lecture Lecture Lecture G.D G.D G.D G.D G.D G.D G.D 1 1 1 1 1 Lecture Lecture Lecture Lecture Lecture G.D G.D G.D G.D G.D 1 1 1 1 1 Lecture Lecture Lecture Lecture Lecture G.D G.D G.D G.D G.D INSTRUCTION PLAN AFTER MST-II Sr. No CHAPTER 5 TEACHING SCHEDULE Sr. LECTUREWISE BREAKAGE No Date 1 2 17/4/13 18/4/13 No. of Mode of Lec. Delivery* Reqd. 1 Lecture 1 Lecture 22/4/13 23/4/13 24/4/13 25/4/13 29/4/13 30/4/13 1/5/13 2/5/13 3/5/13 1 1 1 1 1 1 1 1 1 3 4 5 Memory Organization 6 7 8 9 10 11 RAM and ROM chips Memory connection to CPU auxiliary memory/Test associative memory read and write operation Cache memory associative mapping virtual memory memory management hardware Memory segmentation. Revision Lecture Lecture Lecture Lecture Lecture Lecture Lecture Lecture Lecture Students Role** G.D G.D G.D G.D G.D G.D G.D G.D G.D G.D G.D Note : Add another page, if required. * Mode of delivery may be lectures, Film/CD, Case study etc. ** Students Role: Group Discussion, Presentation, Assignment etc ***Academic Activity :(Class Test, Presentation, Case Study, Paper Solving, Doubt clearing or any other). Syllabus Coverage Reports (SCR) – Dates of submission are Note: Teacher will judiously plan the coverage of syllabus after considering the dates of MST’s/Extra Co-curricular activities etc. Ist SCR: 45 2nd SCR:85 3rd SCR: 100 Reason for not covering the syllabus as planned. How to conduct classes: ( The period break-up suggested is as follows) : 1. 2. 3. 2-3 minutes on review of previous lesson/topic/ discussion 2-3 minutes for attendance 45 minutes for actual teaching that will include the following two important stages: (a) Broad overview of what the teacher will teach today (b) What he/she expects the students to learn. 4. 2-3 minutes for summarizing the lesson/topic covered and giving homework assignments. 5. 2-3 minutes for students’ evaluation/assessment/feedback. 4. MY RESOURCE BANK: S.NO *Additional Text Books Author Publisher Edition 1 Computer Architecture Amit sood Eagle 2013 2 Computer Architecture Er.Gurpreet Singh IPH 2013 S.NO Standard Reference Book Author Publisher Edition 1 Computer architecture Morris Mano Pearson 4th 2 Computer organization and architectureWilliam Stallings Prentice Hall 8th 3 Computer-architecture-parallel-processing Briggs Tata Mc Graw Hill 6th 3 4 S.NO 1 *Additional Newspaper & Periodicals www.google.com 2 www.wikipedia.com Publisher (in case of Periodicals) * NOTE: Additional new reference books, journals & news papers must be incorporated to the standard Instruction Plan as the course is being taught in the semester. Date: 20-01-2013 Sig. of faculty member: Signatory of HOD with Remarks ________________________ Director ______________________ Dean (Academic Affairs) (ACADEMIC AUDIT RECORD/ INSPECTION REPORT) DATE REMARKS SIGNATURE OF DIRECTOR/DEAN/HOD _________________________ (DIRECTOR)