Cycle Time - xs3d.kaist.edu

advertisement

CASE 2014 Technical Presentation

Cycle Time and Throughput Models of Clustered

Photolithography Tools for Fab-Level Simulation

Kyungsu Park and James. R. Morrison

Department of Industrial and Systems Engineering

KAIST, South Korea

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 1

Presentation Overview

•

Motivation

•

System description: Clustered photolithography tool (CPT)

•

Equipment models

•

Linear model

Affine model

Exit recursion model

Flow line model

Numerical experiments

Same sample & same parameter

Different sample & same parameter

Different sample & different parameter

•

Concluding remarks

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 2

Motivation

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 3

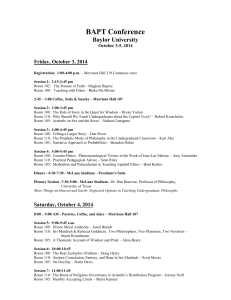

Motivation (1)

• Semiconductor manufacturing

• Global revenue in 2013: NT$ 9,540 billion (US$ 318 billion)

[1]

• Construction costs

• 300 mm wafer fab:

• 450 mm wafer fab:

NT$150 billion

NT$300-450 billion

(US$ 5 billion [2])

(US$10-15 billion)

• Significant value for improvements

• 1996-1999: Fab production control method earned Samsung NT$ 15 bi

llion (US$ 1 billion [3]) additional revenue

• 2005: IBM’s 30 independent supply chains merged into a single global

system and saved NT$ 180 billion (US$ 6 billion [4])

• …

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 4

Motivation (2)

• Clustered photolithography tools (CPT)

•

•

•

•

Purchase cost of NT$ 0.6-3 billion (US$ 20-100 M [5])

The most expensive tool in a fabricator

Typically the bottleneck of the fabricator

Key yield and cycle time contributor

[5]

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 5

Motivation (3)

• Want: Models for CPTs

• Accurate:

Predict throughput with less than 1% error

• Expressive:

Incorporate fundamental behaviors

• Computationally tractable: Very quick to calculate results

• For the purpose of:

•

•

•

•

Understanding toolset performance

Enabling capacity optimization

Toolset scheduling or optimization

Improving the quality of fab simulation models

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 6

System Description:

Clustered Photolithography Tool (CPT)

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 7

System Description: CPT (1)

Scanner

Clustered

Photolithography

Tool

•

•

•

•

•

•

Multi-cluster tool, robot in each cluster, IF buffers, STK buffer

Scanner is often the CPT bottleneck

Largely deterministic process times

Process time can vary by product

Setups between lots (reticle changes, pre-scan setup, …)

Wafer handling robot decision policy & deadlock prevention [6]

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 8

System Description: CPT (2)

“

“

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 9

System Description: Performance Metrics

• Notation

al: Arrival time of lot l to the tool

Sl: Start time of lot l in the tool

Cl: Completion time of lot l from the tool

• Performance measures

Cycle time of lot l: CTl := Cl - al

Computation time

Lot residency time of lot l: LRTl := Cl - Sl

Throughput time of lot l: TTl := min{ LRTl , Cl – Cl-1 }

TT1

TT2

TT3

Lot 1

Lot 2

Lot 3

Time

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 10

Equipment Models

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 11

Models for CPTs

• Models with various levels of detail

Detailed Model

Linear Model

“Everything”

A(k1)

A(k1), B

Affine Models

A(k1), B(k1)

Access Big Data

A(k1), B(k1, k2)

Flow Line

Models

Parametric flow lines

Data Analytics

Empirical flow lines

With complete tool log data

Exit Recursion

Models

With wafer in/out log data

With lot in/out log data

Simulate

models

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 12

Linear Model

Ax Model for lot cycle time in a one machine tool

Wafers

enter

Wafers

exit

m

Al

•

Referred to as the Ax equipment model or linear model

Pros:

•

•

between

wafer completions:

–TimeSimple

to understand

estimation:

–Process

Fasttime

computation

•

Cons:

Al

PT

Ak1 ∙ w(l)

( w(l):tothe

number

wafers

–Tl =

Exactly

matched

single

waferoftool,

notof

tolot

CPTl )

𝐴 𝑘1 =

𝑙∈𝛺(𝑘1)[𝐶𝑀,𝛺(𝑙,𝑤 𝑙 ) −𝑆(𝑙)]

Complete Model:

𝑆l = max{ al , 𝑉l-1 }

𝐿l = 𝑆l

𝐶 l = 𝑆l + Ak1 ∙ w(l)

𝑉l = 𝐶 l

𝑙∈𝛺(𝑘1) 𝑤(𝑙)

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 13

Affine Models

𝐴 𝑘1 =

𝑙∈𝛺(𝑘1)[𝐶𝑀,𝛺(𝑙,𝑤 𝑙 )

𝐵=

𝑙∈𝛺(𝑘1)[𝑤

𝑙∈𝛺[𝐶𝑀,𝛺(𝑙,1)

− 𝐶𝑀,𝛺(𝑙,1) ]

𝑙 − 1]

− 𝑆(𝑙)]

𝑙∈𝛺 1

B can be generalized to B(k1), B(k1, k2)

•

Pros:

•

•

••

•

• Referred

Simpletotoasunderstand

the Ax+B model

• FirstFast

computation

wafer

delay:

Bl

Time between wafer completions:

Al

Cons:

estimation:

• Process

Only time

one module

per process, so not matched to CPT

= Ak1

∙ (w(l)

1) +when

Bl the

( w(l)

: the

number of wafers of lot l )

• TlPTNew

lots

enter–only

tool

is empty

Complete model:

𝑆l = max{ al , 𝑉l-1 }

𝐿l = 𝑆l

𝐶 l = 𝑆l + B + Ak1 ∙ (w(l) - 1)

𝑉l = 𝐶 l

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 14

Flow Line Models: Elementary Evolution Equations

Process i

W

W-1

• Notation

• aw : Arrival time of wafer w to the tool, aw≥ aw-1

• Xi(w) : Entry time of wafer w into process i of the tool

• 𝜏𝑖 : Deterministic process time for process i

• Elementary Evolution Equations (EEEs)

• X1(w) = max{aw , X2(w-1) }

• Xi+1(w) = max{Xi(w) + 𝜏𝑖 , Xi+2(w-1) }

• XM(w) = max{XM-1(w) + 𝜏𝑀−1 , XM(w-1) + 𝜏𝑀 }

(M is the last process)

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 15

Flow Line Models: Extensions

Wafers

enter

Wafers

exit

• Elementary Evolution Equations (EEEs) can be generalized to allow:

•

•

•

•

Different classes of wafer to be produced

Multiple modules per process

Consider robotic workload in process times of modules

Consider setups – reticle setup, pre-scan setup

• Parameter extraction

• Parametric flow line model – Known process times, robot times, and setup times

• Empirical flow line model – Parameters extracted from tool processing data

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 16

…

…

Flow Line Models: Exit Recursions

Wafer Lots

Arrive

P1

P2

P3

t1

t2

t3

PM

…

tM

Wafer Lots

Exit

• Theorem: Exact recursion for customer completion (exit) times [7,8]

…

…

M

cM k 1 max ak 1 t m , cM k t B

m 1

R =3

R1=2

P2

R2=1

3

RM=2

Customers

Arrive

Customers

Exit

…

• Theorem: Recursive bound for customer completion (exit) times [9]

M

(i )

C (k ) max ak t m , max C (k i ) t max

iN

m 1

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 17

Exit Recursion Model (1)

• Conceptually based on flow line exit recursions

~

~

Ci max ai FWD k (i ) A1k(i) (Wi 1), Ci 1 A2k(i),k(i 1) (Wi 1) B k (i ),k (i 1)

No Contention at bottleneck

Contention at bottleneck

• Complete model

~

~

~

k(i)

k(i),k(i1)

Ci max Si FWDk(i) A1 (Wi 1), Ci 1 A2

(Wi 1) Bk(i),k(i 1)

~

~

k(i),k(i 1)

Si Li E

~

~

Li max ai , Vi 1

~ ~

k(i),k(i 1)

Vi Ci D

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 18

Exit Recursion Model (2)

• Parameter extraction

FWD k

1

FWD(l )

Φ1(k) lΦ (k)

k

A1

1

B

k1 ,k 2

1

Φ2(k1,k 2 )

B(l ) D

l Φ2(k1 ,k 2 )

l Φ1(k)

k1 ,k 2

1

A (l )

Wl 1 lΦ (k) 1

1

Φ0 (k1,k2 )

k

A2

1

D(l ) E

lΦ0(k1 ,k 2 )

l Φ 2(k)

k1 ,k 2

1

Φ0(k1,k2 )

• Populations used as a function of available category of data

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 19

1

A (l )

Wl 1 lΦ (k) 2

2

E(l)

lΦ0(k1 ,k 2 )

Model Properties

Proposition: Exactness of completion times in the linear model

(i)

(ii)

All completion times in the linear model exactly match those in a single process deterministic flow

line from which the parameters are derived..

Throughput time can be exactly achieved on average in a flow line with different structure..

Proposition: Exactness of completion times in the affine model

(i)

(ii)

Completion times in the affine model exactly match those in a deterministic flow line in which each

lot starts on an empty tool (via full flush constraint) from which the parameters are derived.

Throughput time can be exactly achieved on average in a flow line with different structure..

Proposition: Exactness on completion times in the exit recursion model

Completion times in the exit recursion model exactly match those in a deterministic flow line from which

the parameters are derived with

(i) A single class of wafers and constant setup between wafers , or

(ii) Multiple wafer classes with no setup, proportional service and geometric decay within channels

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 20

Numerical Experiments

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 21

Numerical Experiments

[1]

•

•

•

•

•

LWP(Longest waiting pair) robot policy[6]: gives optimal steady state throughput

Dead lock avoidance rule

Setup time ~ Uniform(210, 260); Reticle alignment ~ Uniform(240, 420)

13,000 lots x 30 replications

Assume detail simulation is true operation.

A : Linear Model B : Affine Model - A(k1),B C : Affine Model - A(k1),B(k1)

D : Affine Model - A(k1),B(k1,k2) E : FL Model F : EFL Model

G : ER Model - Tool Log H : ER Model - Wafer Log I : ER Model - Lot Log

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 22

Same Sample, Same Parameter

•

loading level : 0.95, train level : 3, lot size : {22, 23, 24} with probability {0.25, 0.5, 0.25}, both setups

Cycle Time

40%

36.36%

36.35%

Lot Residency Time

10%

36.28% 36.26%

0.61%

-2.59%

E

F

G

2.56%

2.34%

0%

30%

-10%

20%

Detail

A

B

C

D

H

I

-20%

10%

0%

-10%

2.74%

Detail

A

B

C

D

-0.09%

-0.13%

E

F

2.60%

3.52%

3.17%

-30%

-40%

G

H

I

-50%

-60%

•

Throughput Time

10%

•

5%

0.00%

0%

Detail

A

-0.00

B

-0.00

C

-0.00

D

-0.01%

E

-0.02%

0.00%

0.03%

-0.09%

F

G

H

I

--51.32% -51.33% -51.33% -51.33%

Linear model & Affine models are only good in

throughput time.

ER models & Flow line models are good in all

times.

-5%

-10%

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 23

Same Sample, Same Parameter

•

loading level : 0.3, train level : 3, lot size : {22, 23, 24} with probability {0.25, 0.5, 0.25}, both setups

Cycle Time

Lot Residency Time

10%

10%

3.97%

5%

5%

2.16%

2.15%

2.15%

2.15%

0%

Detail

A

B

C

D

2.27%

-0.30%

-0.57%

E

F

2.33%

-0.04%

G

H

-17.28% -17.28% -17.28% -17.28%

0%

I

-5%

-5%

Detail

A

B

C

D

0.20%

-0.09%

0.81%

E

F

G

1.71%

H

I

-10%

-15%

-10%

-20%

•

Throughput Time

10%

•

5%

0%

Detail

-0.00%

-0.00%

-0.00%

-0.00%

-0.13%

-0.35%

0.03%

0.07%

-1.82%

A

B

C

D

E

F

G

H

I

Linear model & Affine models are good in cycle

time, and throughput time.

ER models & Flow line models are good in all

times

-5%

-10%

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 24

Different Sample, Same Parameter

•

loading level : 0.95, train level : 3, lot size : {22, 23, 24} with probability {0.25, 0.5, 0.25}, both setups

Cycle Time

Lot Residency Time

80%

10%

0%

58.35%

60%

43.43%

-10%

46.19% 47.40%

40%

-20%

20%

-30%

4.97%

-0.37%

1.24%

2.70%

2.04%

E

F

G

H

I

0%

Detail

A

B

C

D

-20%

•

5%

-0.12%

0%

Detail

A

0.05% 0.05%

B

C

0.06%

0.03%

D

E

0.01%

F

0.01%

G

0.04%

H

B

C

D

E

F

G

H

I

2.75%

0.62%

-2.58%

2.77%

2.46%

-50%

•

10%

A

-40%

-60%

Throughput Time

Detail

-51.40%

-51.31% -51.31% -51.31%

Linear model & Affine models are only good in

throughput time.

ER models & Flow line models are good in all

times.

-0.00%

I

-5%

-10%

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 25

Different Sample, Same Parameter

•

loading level : 0.3, train level : 3, lot size : {22, 23, 24} with probability {0.25, 0.5, 0.25}, both setups

Cycle Time

Lot Residency Time

10%

10%

3.98%

5%

5%

2.57%

2.65%

2.52%

2.30%

2.42%

0.44%

-0.17% -0.35%

0%

Detail

A

B

C

D

E

F

G

H

-17.22% -17.14% -17.16% -17.16%

0%

2.28%

I

-5%

-5%

Detail

A

B

C

D

0.29%

-0.03%

0.84%

E

F

G

2.23%

H

I

-10%

-15%

-10%

-20%

•

Throughput Time

10%

•

5%

0%

Detail

0.09%

0.19%

A

B

0.17%

0.17%

-0.16%

-0.37%

0.05%

0.14%

-1.46%

C

D

E

F

G

H

I

Linear model & Affine models are good in cycle

time, and throughput time.

ER models & Flow line models are good in all

times

-5%

-10%

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 26

Different Sample, Different Parameter

•

From loading level : 0.95 & train level : 3, To lading level : 0.8 & train level : 1

With lot size : {22, 23, 24} with probability {0.25, 0.5, 0.25}, both setups

Cycle Time

Lot Residency Time

25%

10%

19.29%

20%

20.21%

17.67%

15%

0%

Detail

-5.09%

-4.05%

A

B

-5.90% -4.12%

C

D

-0.04%

0.43%

6.36%

5.67%

Detail

A

B

C

D

E

F

G

H

I

E

F

-30%

G

H

I

-10%

-40%

-37.96% -37.89% -37.89% -37.81%

-50%

•

Throughput Time

10%

•

5%

-5.19%

0%

-5%

2.17%

-20%

5%

-5%

0.08%

0%

-10%

10%

0.11%

Detail

A

-5.09%

B

-5.09%

-4.97%

-0.00%

-0.11%

-0.04%

0.00%

-0.42%

C

D

E

F

G

H

I

•

Linear model & Affine models are slightly good

in cycle time, and throughput time .

ER models are good in lot residency time, and

throughput time.

Only FL models are good in all times.

-10%

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 27

Different Sample, Different Parameter

•

From lot size: {22, 23, 24} with {0.25, 0.5, 0.25}, to lot size: {12, 13, 14} with {0.25, 0.5, 0.25}

with loading level : 0.95, train level : 3, both setups

Cycle Time

Lot Residency Time

40%

20%

20%

-33.18% -14.54% -15.85% -15.21%

0%

Detail

A

B

C

D

0.29% -0.64%

E

F

-0.43%

G

H

I

-20%

-20%

Detail

A

B

C

D

F

3.56%

7.43%

G

H

0.38%

I

-40%

-80%

•

Throughput Time

5%

0%

Detail

A

B

C

D

-0.13%

-0.16%

-0.17%

0.02%

-3.78%

E

F

G

H

I

•

•

-10%

-9.92%

-9.92%

Linear model & Affine models are bad in all

times.

ER models are good in lot residency time, and

throughput time.

Only FL models are good in all times.

-9.92%

-15%

-20%

E

0.39%

-60%

-40%

-5%

-59.70% -56.67% -56.68% -56.67% 1.26%

0%

17.66% 16.71%

-16.21%

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 28

Computational Comparison

Relative Computation Time

Linear Model

0.5

Affine Model

1

ER Model

2.4

FL Model

120

Detailed Simulation

13,000

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 29

Accuracy Comparison

Same Sample, Same Parameter Different Sample, Same Parameter Different Sample, Different Parameter

Linear Model

CT

LRT

TT

CT

LRT

TT

CT

LRT

TT

Affine Models

CT

LRT

TT

CT

LRT

TT

CT

LRT

TT

ER Models

CT

LRT

TT

CT

LRT

TT

CT

LRT

TT

Flow Line Models

CT

LRT

TT

CT

LRT

TT

CT

LRT

TT

• Errors relative to detailed model

• Error of 20%+

• Error 5-20%

• Error 0-5%

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 30

Concluding Remarks

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 31

Concluding Remarks

• CPT: Expensive & typically fab bottleneck toolset

• Models for CPT throughput time, process time & cycle time

• Classic models: Linear, affine

• Recent models: Flow line, exit recursion

• Compare: Computation and accuracy

• Next directions

• Improved models: Newer exit recursions, additional

parameters

• Implementation: Fab simulation, optimization, etc.

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 32

References

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

HIS iSuppli April 2011

Elpida Memory, Inc., available at http://www.eplida.com,

Leachman, Robert C., Jeenyoung Kang, and Vincent Lin. "SLIM: Short cycle time and low inventory in manuf

acturing at samsung electronics." Interfaces32.1 (2002): 61-77

http://www.forbes.com/forbes/2003/0811/076.html

Roger H. French and V. Hoang, “Immersion Lithography: Photomask and Wafer-Level Materials,” Tran.

Annual Review of Materials Research, Vol. 39, 93-126

Hyun Joong Yoon and Doo Yong Lee, “Deadlock-free scheduling of photolithography equipment in semicon

ductor fabrication,” IEEE Trans. Semi. Mfg., vol. 17, no. 1, pp. 42-54, 2004

Avi-Itzhak, B. "A sequence of service stations with arbitrary input and regular service times." Management

Science 11.5 (1965): 565-571

Friedman, Henry D. "Reduction methods for tandem queuing systems." Operations Research 13.1 (1965): 1

21-131

Park, Kyungsu, and James R. Morrison. "Performance evaluation of deterministic flow lines: Redundant mo

dules and application to semiconductor manufacturing equipment." Automation Science and Engineering (

CASE), 2010 IEEE Conference on. IEEE, 2010

Morrison, James R. "Deterministic flow lines with applications." Automation Science and Engineering, IEEE

Transactions on 7.2 (2010): 228-239

Morrison, James R. "Multiclass flow line models of semiconductor manufacturing equipment for fab-level s

imulation." Automation Science and Engineering, IEEE Transactions on 8.1 (2011): 81-94

Longest waiting pair: [7] Geismar, H.N.; Sriskandarajah, C.; Ramanan, N., "Increasing throughput for robotic cells

with parallel Machines and multiple robots," IEEE Trans. Auto. Sci. and Eng., vol.1, no.1, pp.84,89, Jul 2004

© 2014 – James R. Morrison – IEEE CASE – August 2014 - 33