Chapter 10

advertisement

Chapter 10

State Machine Design

State Machine Definitions

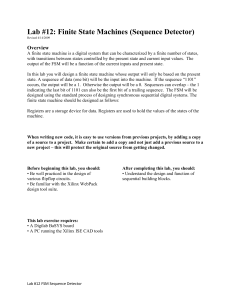

• State Machine: A synchronous

sequential circuit consisting of a

sequential logic section and a

combinational logic section.

• The outputs and internal flip flops (FF)

progress through a predictable

sequence of states in response to a

clock and other control inputs.

2

State Machine Types

• Moore Machine: A Finite State Machine

(FSM) whose outputs are determined

only by the Sequential Logic (FF) of the

FSM.

• Mealy Machine: An FSM whose

outputs are determined by both the

sequential logic and combinational logic

of the FSM.

3

State Machine Basics

• State Variable: The variable held in the

SM (FF) that determines its present

state.

• A basic FSM has a memory section that

holds the present state of the machine

(stored in FF) and a control section that

controls the next state of the machine

(by clocks, inputs, and present state). 4

State Machine Basics

5

State Machine Basics

6

FSM Design Techniques

• Classical Design: Makes use of state

tables, FF excitation tables, and

Karnaugh Mapping to find FF input

control logic.

• VHDL Design: Uses case statements

or IF THEN ELSE statements to set the

design and the logic synthesis tools to

define equations.

7

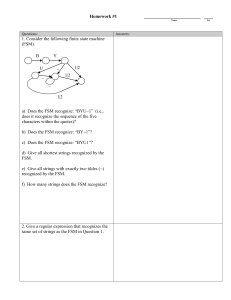

Classical Design Approach – 1

• Define the actual problem.

• Draw a state diagram (bubble) to

implement the problem.

• Make a state table. Define all present

states and inputs in a binary sequence.

Then define the next states and outputs

from the state diagram.

8

Classical Design Approach – 2

• Use FF excitation tables to determine in what

states the FF inputs must be to cause a

present state to next state transition.

• Find the output values for each present

state/input combination.

• Simplify Boolean logic for each FF input and

output equations and design logic.

9

FSM Design Example 1

• Gray Code Counter that sequences

{000, 001, 011, 010, 110, 111, 101, 100,

000}.

• From this the state and excitation table

is developed for D flip flops (see Table

10.2 in the textbook).

10

FSM Design Example 1

11

FSM Design Example 1

12

FSM Design Example 2

• From the K-Maps for the inputs D0, D1,

and D2, the following equations are

developed:

D2 Q1 Q0 Q2Q0

D1 Q1 Q0 Q2Q0

D0 Q2 Q1 Q2Q1

• Refer to Figure 10.6 in the textbook.

13

FSM Design Example 2

14

VHDL FSM Design

• Uses an enumerated type to declare

state variables.

• Enumerated Type: A user-defined type

in which all possible values of a named

identifier are listed in a type definition.

• An FSM uses a CASE statement on the

enumerated type state variable.

15

FSM VHDL Example

-- gray_ct1.vhd

-- 3-bit Gray code counter

-- (state machine with decoded outputs)

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

16

FSM VHDL Entity

ENTITY gray_ct1 IS

PORT(

clk

: IN

STD_LOGIC;

q

: OUT STD_LOGIC_VECTOR(2 downto 0));

END gray_ct1;

17

FSM VHDL Architecture – 1

ARCHITECTURE a OF gray_ct1 IS

TYPE STATE_TYPE IS (s0,s1,s2,s3,s4,s5,s6,s7);

SIGNAL state

:STATE_TYPE;

BEGIN

PROCESS(clk)

BEGIN

18

FSM VHDL Architecture – 2

IF (clk’EVENT AND clk = ‘1’) THEN

CASE state IS

WHEN s0 => state <= s1;

WHEN s1 => state <= s2;

WHEN s2 => state <= s3;

WHEN s3 => state <= s4;

WHEN s4 => state <= s5;

19

FSM VHDL Architecture – 3

WHEN s5 => state <= s6;

WHEN s6 => state <= s7;

WHEN s7 => state <= s0;

END CASE;

END IF;

END PROCESS;

20

FSM VHDL Architecture – 4

WITH state SELECT

q <= “000” WHEN s0,

“001” WHEN s1,

“011” WHEN s2

“010” WHEN s3,

“110” WHEN s4,

“111” WHEN s5,

“101” WHEN s6,

“100” WHEN s7;

END a;

21

VHDL Output Assignment

• The output assignment for the following

example could have also been in the

CASE test statements (in the process).

WHEN s0 => state <= s1;

q <= “001”;

WHEN s1 => state <= s2;

q <= “011”;

22

FSM with Control Inputs

• Same design approach used for FSM

such as counters.

• Uses the control inputs and clock to

control the sequencing from state to

state.

• Inputs can also cause output changes

not just FF outputs.

23

FSM with Control Inputs

24

SM Diagram Notation – 1

• Bubbles contain the state name and

value (StateName/Value), such as

Start/000.

• Transitions between states are

designated with arrows from one bubble

to another.

• Each transition has an ordered

Input/Output, such as in1/out1.

25

SM Diagram Notation – 2

• For example, if SM is at State = Start

and if in1 = 0, it then transitions to State

= Continue and out1 = 1, out2 = 0.

• The arrow is drawn from start bubble to

continue bubble.

• On the arrow the value 0/10 is given to

represent the in1/out2,out1.

26

SM Design – 1

• State Table for the State Diagram

Present Status

Q

0

0

1

1

Input

in1

0

1

0

1

Next State Sync. Inputs

Outputs

Q

JK

out1 out2

1

1X

1

0

0

0X

0

0

0

X1

0

1

0

X1

0

1

27

SM Design – 2

• The State Excitation Tables for the JK

Inputs

Transition

0 1

0 1

1 0

1 0

JK

0X

1X

X1

X0

28

SM Design – 3

• The following equation represents the

next state and output logic of the state

machine.

J Q in1 Q in1 in1

K 1

out1 Q in1

out2 Q in1 Q in1 Q

29

SM Design – 4

• The pulser SM has two outputs that are

not always synchronized to clock.

• The pulse out2 is always synched to a

change in clock, but out1 could change

if in1 changes.

• The following slides show a VHDL

implementation of the Pulser SM.

30

SM Design – 4

31

SM Design – 4

32

SM Pulser Architecture – 1

• Uses an enumerated type state listing of

start and continue.

ARCHITECTURE a OF state_x1 IS

TYPE PULSER IS (start, continue);

SIGNAL sequence : PULSER;

BEGIN

PROCESS(clk)

BEGIN

33

SM Pulser Architecture – 2

• A portion of the case statement:

IF(clk’EVENT AND clk = ‘1’) THEN

CASE sequence IS

WHEN start =>

IF in1 = ‘1’ THEN

sequence <= start;

out1 <= ‘0’;

out2 <= ‘0’;

34

SM Pulser Architecture – 3

• In the VHDL case statement, an IF

conditional test statement was used to check

the Input Signal (in1) for State = Start.

• IF in1 = 1, stay at State = Start; IF in1 = 0,

then move to State = Continue (next clk).

• If the present state was continue, the next

state is always start, so an IF statement is

not required.

35

Switch Debouncer

• A digital circuit that is used to remove

the mechanical “bounce” from a switch

contact.

• When a switch is closed, the contacts

bounce from open to closed to cause

false transitions.

• A simple debouncer is a cross-coupled

NAND Latch.

36

Switch Debouncer

37

Shift Register Debouncer – 1

• An SR can be used to delay the glitches

(bounces) with a slow clock (T = 2.6

ms).

• The input of the SR is from the switch,

and it is clocked through a 4-bit register.

• The output of the SR is compared to the

input, and if it is equal, the SR is still

loaded.

38

Shift Register Debouncer – 2

• When the switch bounces, the SR input

and output are not equal, so the register

stops loading to allow the delay to be

added.

• The comparison is done by an XNOR

gate to control the SR Load.

39

Shift Register Debouncer – 3

• 4-bit LPM SR clocked every 2.6 ms

• If pb_in pb_out for 10.4 ms, the output

changes.

• If not, then the output remains the same.

• Change on the input must be stable for 4

clock cycles before the output changes.

40

Shift Register Debouncer – 3

41

SR Debounce Entity

• Uses an in from SW (pb_in) and a

debounced output (pb_out).

ENTITY debouncer IS

PORT(

pb_in, clock

: IN

STD_LOGIC;

pb_out

: OUT STD_LOGIC);

END debouncer;

42

SR Debounce Architecture – 1

ARCHITECTURE debounce OF debouncer IS

SIGNAL ctr_q

:STD_LOGIC_VECTOR (15 downto 0);

SIGNAL srg_parallel_in :STD_LOGIC_VECTOR (3 downto 0);

SIGNAL srg_serial_in

:STD_LOGIC;

SIGNAL srg_serila_out :STD_LOGIC;

SIGNAL srg_load

:STD_LOGIC;

43

SR Debounce Architecture – 2

BEGIN

clock_divider : lpm_counter

GENERIC MAP (LPM_WIDTH => 16)

PORT MAP (clock => clock, q => ctr_q);

44

SR Debounce Architecture – 3

-- shift register clocked by MSB of counter 216

delay_ element : lpm_shiftreg

GENERIC MAP (LPM_WIDTH => 4)

PORT MAP (clock

=> ctr_q (15),

load

=> srg_load,

data

=> srg_parallel_in,

shiftin

=> srg_serial_in,

shiftout

=> srg_serial_out);

45

SR Debounce Architecture – 4

srg_load <= (not pb_in) xnor srg_serial_out;

srg_parallel_in (3) <= srg_serial_out;

srg_parallel_in (2) <= srg_serial_out;

srg_parallel_in (1) <= srg_serial_out;

srg_parallel_in (0) <= srg_serial_out;

srg_serial_in <= not pb_in;

pb_out <= srg_serial_out;

END debounce;

46

Unused States – 1

• Some modulus counters, such as MOD10, have states that are not used in the

counter sequence.

• The MOD-10 Counter would have 6

unused states (1010, 1011….1111)

based on 4-bits.

47

Unused States – 2

• An FSM can also have unused states,

such as an SM, with only 5 bubbles in

the state diagram (5-states). This FSM

still requires 3 bits to represent these

states so there will be 3 unused states.

• These unused states can be treated as

don’t cares (X) or assigned to a specific

initial state.

48

Unused States – 2

49

Unused States Example Slide – 1

• A five-variable state diagram is shown in the

previous slide, with unused states assigned

to the initial state = Start.

• The normal state sequence is Start Wait1

Wait2 Pulse1 Pulse2 and then back

to Start.

• Any other states cause a transition back to

Start.

50

Unused States Example Slide – 2

• The Input (in1) Sequence of 101 causes the

machine to advance from Start Wait1

Wait2. Then it does two unconditional

transitions to Pulse1 and Pulse2.

• The Pulse1 and Pulse2 States generate two

pulses on the Outputs (out1 and out2).

51

Unused States Example Slide – 3

• Any unused states are given the value

of Start (000) for its next state.

• For the FSM 3-Bit Register (FF), this

generates the equations shown on the

next slide.

52

Unused States Example Slide – 4

D2 Q2Q1Q0

D1 Q2Q1Q0 Q2Q1Q0 in1

D0 Q2Q0 in1 Q2Q1in1

out1 Q2Q1Q0

out2 Q2Q1Q0

53

Traffic Light FSM – 1

• The FSM controls are for a North-South

Road and an East-West road (see

Figure 10.38 in textbook).

• This generates 3 Outputs for each road

(nsr, nsy, nsg, and ewr, ewy, ewg) for

the Red, Yellow, and Green Lights (Low

= ON).

54

Traffic Light FSM – 1

55

Traffic Light FSM – 1

56

Traffic Light FSM – 2

• An Input called TIMER controls the

length of a light cycle (TIMER = 1

causes a S0 to S1 or a S2 to S3

transition).

• When one light is green (S0(EW) or

S2(NS)), the other is red.

57

Traffic Light FSM – 3

• There is an unconditional timed transfer

from yellow to red or red to green.

• A normal cycle is 4 clocks GREEN,

1 clock YELLOW, 5 clocks RED.

• Solution is left as an example problem.

58