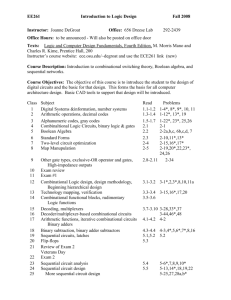

Course Description

advertisement

Introduction to Computer Engineering CPE 201 MW 07:00P-09:45P CED 331C 1/22/08 - 5/16/07 Instructor: Zehang Sun (PhD) Textbook: Digital Design, Fourth Edition, Prentice Hall, 2007. Authors: Morris Mano, Michael D. Ciletti Midterm Examination: 3-12 Final Examination: 5-14 Course Description Lecture + Lab: 3 + 3; Credit(s): 4 This course covers theoretical and practical topics in the operation of digital electronic circuits, a ubiquitous and critically important foundation for the ECE discipline. Binary data representation, Boolean algebra, combinatorial and sequential logic, and abstraction of standard design components are introduced to discuss the design and analysis of digital circuit designs. A discussion and software lab component reemphasize these concepts with examples and practical applications.Prerequisite: CS 135 with a “C” or better. (BS-EE students are exempt from the “C” requirement.) COURSE OBJECTIVES In this course your will learn: Fundamentals of number bases, specifically binary number systems Boolean logic and logic functions Combinational Circuits Sequential (state) Machines Registers and Counters Memory and Programmable logic devices Register transfer Level Verilog HDL Modern design tools METHOD OF INSTRUCTION Attendance will be taken at the beginning of each class session in accordance with WNC policy. All students are responsible for exercises, projects, discussions, or announcements missed due to their absence. The nature of this course makes successful completion of the class more difficult if more than two class labs are missed. If you develop a problem attending class or keeping up with your assignments, please talk to me before it affects your grade. There may be an occasion when it is unavoidable to be late or miss a class and these instances are acceptable within reason. If you have a conflict between this class and another class or a job, this should be brought to my attention immediately so other arrangements can be made. One class period will be made up of lecture and the other of hands on labs. Missed labs will need to be made up at the convenience of the instructor. STUDENT EVALUATION Two examinations are scheduled for the semester. In addition there will be homework assigned, with quizzes taken from the homework regularly. Reading assignments are to be done BEFORE you come to class. Quizzes Homework Lab Midterm Final 10% 20% 20% 15% 35% This class does not give “D” or “F” grades. A= 87 - 100% B= 76 - 86% C= 60 - 75% W= Withdrawal for < 60% Course Assignments And Class Schedule Week Class Topic Reading 1 1-22 Chapter 1: Digital system and binary numbers Chapter 1 1.1 1.2 1.3 (Computer Engineering, Binary numbers) 2 1-28 (Binary codes, binary arithmetic) 1-30 (Lab1 Binary Numbers, NI Multisim) 3 2-4 2-6 4 2-11 1.4-1.8 Chapter 2: Boolean Algebra And Logic Gates Chapter 2 (Theorems, properties, Boolean functions, canonical standard forms) 2.1-2.5 (Lab 2 Logic gates with breadboard) (Canonical standard forms, digital circuit design, gate level minimization) 2.6-2.9 2-13 (Lab 3 Logic gates with Multisim) 5 Chapter 3: Gate level minimization 2-20 (Map methods, product of sums, NAND and NOR gate implementations) 3.1-3.7 6 Chapter 4: Combinational Logic Chapter 4 2-25 (Circuits, analysis & design procedures; adders, subtractor) 2-27 (Lab 4 Logic expression) 7 3-3 3-5 8 3-10 3-12 (Decoder & encoders; multiplexers & Verilog HDL) (Lab 5 XILINX ISE) Review lecture Midterm Examination Chapter 3 4.1-4.7 4.9-4.11 Homework Week Class Topic Reading 9 Chapter 5: Synchronous Sequential Logic Chapter 5 3-24 3-26 10 3-31 4-2 11 (Sequential circuits: latches, flip flops) (Lab 6 XILINX FPGA: logic gates) Chapter 5 (Analysis of sequential circuits, synthesis of sequential circuits) Chapter 6: Registers and Counters (shift register and ripple counters Other counters) 4-14 4-16 13 (Verilog HDL for counters) 4-23 5.5 5.6 (Lab 7 XILINX FPGA: decoder) 4-7 4-9 12 4-21 5.1-5.4 Chapter 6 6.1-6.3 Chapter 6 6.6 (Lab 8 XILINX FPGA: counters) Chapter 7: Memory and programmable logic Chapter 7 (RAM, decoding, error detection and correction, ROM) 7.1-7.5 (Lab 9 XILINX FPGA: ripple counter) 14 4-28 4-30 15 (ROM, PAL, Sequential devices) 5-5 (Register transfer level design) 5-7 16 5-12 5-14 Review lecture 7.6—7.8 Chapter 8: Design at the register transfer level Exam Prep FINAL EXAM Chapter 8 8.1-8.4 Homework