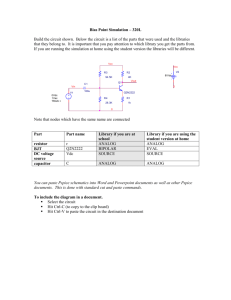

Abdul Azeez_FYP

advertisement