DOC - University of Southern California

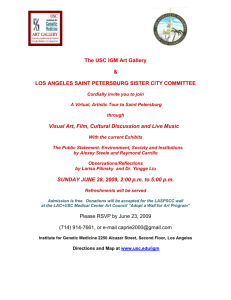

advertisement

S I RE E S H AD I M AD H YAM 720 W 27th St, Apt #9, Los Angeles, CA 90007 (213) 400-8306 adimadhy@usc.edu E D U C AT I O N University of Southern California (USC), Los Angeles, CA Master of Science in Electrical Engineering May 2012 Jawaharlal Nehru Technological University, Hyderabad, India Bachelor of Technology in Electronics and Communication Engineering May 2009 R E L E VA N T C O U R S E W O R K MOS VLSI System Design Solid State Processing and Integrated Circuits Laboratory Computer System Organization and Design MOS VLSI Circuit Design VLSI Computer Aided Design-1 Modern Solid State Devices T E CH NIC A L SKILL S & TOOL S EDA Tools: Cadence 6.0; NC-Verilog; DC Shell; DxDesigner, TINA Pro; Active-HDL; LABVIEW Characterization Equipment:HP4145; HP4155; Tektronics 576 Programming Skills: C++; MATLAB 7.0; Verilog; Assembly; VHDL; Perl (beginner) Operating Systems: Windows 7/Vista/XP; Linux PROFESSIONAL EXPERIENCE Engineering Project Trainee at Nuclear Fuel Complex, Hyderabad, India Spring 2009 Project: Data Acquisition using RS- 232 Serial Communication For Advanced Weld Shear Strength Test Machine Programmed a PLC(Programmable Logic Controller) and developed an interface for acquiring shear strength values through RS232 cable using VB 6.0 Summer Engineering Trainee at Indian Space Research Organization, Sriharikota, A.P, India Summer 2008 Project: Jet Noise Measurement Analyzed method of sound level measurement in GSLV MARK-3 model test using charge amplifiers, special microphones and acquired data using a high-speed data acquisition system (Nl DAQ- LABVIEW). R E L E VA N T P R O J E C T W O R K Design of DDR2 SDRAM Controller, USC Spring 2011 Front & Back-End Design of DDR2 SDRAM Memory Controller, starting from hardware implementation using Verilog, followed by synthesis and layout simulation, then finally post-layout analysis & verification. The Controller has a FIFO based front-end architecture & designed to carry out Scalar & Block Read/Write operations. Directed Research-Border Ownership Neuron -The BioMimetic Real-Time Cortex Project, USC Fall 2010 Guide: Dr. Alice Parker Designed the border ownership neuron model using inhibitory and excitatory synapse circuits designed in 0.18um technology using Cadence Virtuoso Schematic tool and simulated it using Spectre. Latch and FlipFlop Based Pipelined Domino Adder, USC Fall 2010 Designed a 32-bit domino adder (pipelined using latches and flip-flops) using Cadence Virtuoso schematic and layout design tool and simulated it using Spectre. Performed DRC, LVS, Timing Analysis from netlist simulation. Integrated Circuit Fabrication, USC Summer 2010 Fabricated a ring oscillator circuit on a 3-inch Si wafer in a Class-100 clean room. Performed electrical characterization on the various devices fabricated such as diodes, MOSFET's, resistors and capacitors using HP4155, Tektronics 576. 5 Stage Pipelined MIPS Processor, USC Spring 2010 Designed a data path and control unit for Single Cycle and Multi Cycle CPU with support for R-type, load word, store word, jump and branch instructions including full forwarding and hazard detection units and provision to stall when required. LEADERSHIP EXPERIENCE Regional Leader, Mozilla Communities October 2008 - December 2009 Organized Firefox 3.5 Launch event in Hyderabad as a Mozilla Regional Leader. Received state wide press.