Mixer design

advertisement

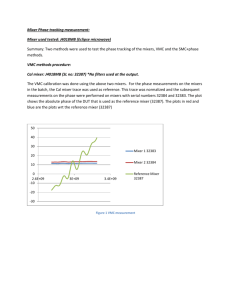

EE 5390 RFIC Design Project Juan Escalera and Hector Garces ABSTRACT The purpose of this project is to employ the knowledge gather in EE 5390 class to design two CMOS integrated circuits; a Low Noise Amplifier and a Mixer to be used in RF wireless applications. This project will be implemented using the Agilent Electronic Design Automation (EDA) product; Advanced Design System (ADS) software for highfrequency system, circuit, and modeling applications tool. To review and understand designs developed for other authors, several IEEE papers and technical books were read and then we select a circuit to be implemented in ADS. Multiple simulations were developed in order to tune up our designs for project specifications. For LNA; Frequency Range, Voltage Gain and Noise Figure were satisfied. Magnitude of input impedance is close to specification, but phase is almost π radians. Total current is much bigger than the project stipulation. We were not able to measure the IIP3 and P1dB. For Mixer all specifications were satisfied. INTRODUCTION The project consist in the design of 2 of the most important sub-circuits in an RF front end. These blocks are the LNA and the mixer. The focus of the LNA design is on the voltage gain, and the input impedance as this block has to be matched to the antenna of the transceiver. The LNA must provide amplification without adding noise to the low power signal received from the antenna (in the order of 10 to 100 V). The amplifier must be linear enough to avoid the distortion from blocking signals. The specifications are: Frequency Range: 940 MHz to 980 MHz Input Impedance: Magnitude 50 10%, Phase 0 2.5 Voltage gain > 20 dB Total Current < 5mA For the mixer design, the purpose of this block is to perform frequency conversion from the incoming RF signal to the low IF frequency, by multiplying it by the LO frequency specified. The specifications for the mixer design are presented: RF input 0.001sin(2fRFt) volts, where fRF is 960 MHz LO (positive node) 2+0.2 sin(2fLOt), where fLO is 950 MHz LO (negative node) 2-0.2 sin(2fLOt), where fLO is 950 MHz METODOLOGY Initially, we spend some sessions working with ADS to get familiarity with the basic function like; create a new project and design, use the component pallet list, know the simulation options, design guide, etc. Then, we were able to use ADS to plot a curve family for CMOS transistors. Low Noise Amplifier Design We reviewed the class notes, textbook “VLSI for Wireless Communication by Bosco Leung”, reference book “RF Microelectronics by Behzad Razavi” and several IEEE papers. Then, we selected the Single-ended half of the complete differential narrowband LNA shown on figure 3.8 (b), at page 100 of textbook and study the design process develop in that book. Using project specifications, we made the computations need to get the components values. We implement the design mention above in ADS and through AC Simulation we were able to measure voltage gain for the frequency range. We observed that, to have a voltage gain grater that 20 dB the load impedance is bigger than 300 ohms. We conclude that a matching network is needed. On the IEEE paper “CMOS LNA in Wireless Applications by Shijun Yang, Ralph Mason and Calvin Plett” publish on 1999 we found a matching network implemented using a CMOS transistor, an inductor and a capacitor. Now we were able to fulfill the voltage gain specification with 50 ohms load impedance. Now, we change to S Parameter Simulation in order to measure the input impedance, output impedance and Noise Figure NF. The complete LNA design is shown in Figure 1 Figure 1. LNA Design Mixer design Basic topology After the study of the theory of mixers from Bosco Leung, Razavi and several technical papers, a single ended mixer is designed. The basic topology of a single ended active mixer consist of a single NMOS transistor M1 acting as a V-I converter and then a current switching block for the Local Oscillator to switch the output currents consisting of 2 NMOS devices. The circuit has a current source on the source of the V-I converter NMOS for biasing purposes. The output of the mixer is taken differentially from the gate terminals of the LO switching pair (not shown). This simplified topology is shown in Figure 2. Figure 2. Simple single ended active mixer DC Biasing The DC biasing is performed first. As mentioned above a constant current source is placed at the source terminal of the V-I NMOS. However it is difficult to achieve the biasing levels required for desired operation point (determined from the device characterization). Therefore an additional biasing technique is adopted, namely applying a DC voltage at the gate terminals of the NMOS devices. This is achieved by a circuit using a PMOS device configured in saturation cascaded with a PMOS transistor observed from Steve Long’s ADS tutorials on mixer design guide examples. In order to achieve the desired voltage drops and to minimize the current drawn from this divider, the ratio of channel width to length for both devices is controlled. It should be mentioned that one voltage divider branch is needed for each NMOS transistor in figure 1 since the small AC signal is superimposed on the DC bias and, using only one voltage divider is impossible without using resistors. Additionally, the current source circuit uses a similar voltage divider, thus the elevated number of transistors in the device (14). This is a design tradeoff between relative high number of transistors and the use of resistors, which is avoided in potentially monolithic integration due to their high noise contributions and difficulty to implement in silicon. AC Sources and load For AC testing purposes, a coupling capacitor of 100 pF is placed between the signal ports and the gates of the NMOS devices. This prevented any DC biasing from the gate terminals to propagate back to the AC small signal sources. To convert the single ended signal from the LO AC source to double balanced, a transformer is used in the following configuration (Figure 3): Figure 3. Single ended to differential conversion For loading purposes, resistors are being used to produce the IF output voltage differentially at the outputs of the drain terminals of the LO NMOS pair. Figure 4 shows the complete mixer circuit; a VDD voltage source of 3.3 V is being used (not shown). Figure 4. Complete single ended mixer SIMULATIONS AND RESULTS Low Noise Amplifier Design For the frequency range of interest, Figure 5 shows the voltage gain and Figure 6 displays the Noise Figure. Magnitude and phase for input impedance are shown at Figure 7. Figure 5. Voltage Gain Figure 6. Noise Figure Figure 7. Magnitude and phase of input impedance Mixer design The simulations performed after the DC biasing, is the Harmonic Balance simulation. This simulation allows for the calculation of mixing terms in the frequency domain and to simulate certain number of harmonics always present in non-linear circuits. To configure the Harmonic Balance block it is only necessary to declare the frequencies at which all your AC sources are working and specify the number of harmonic terms to be simulated for each source. Figure 4 shows the Harmonic Balance simulation block. For this project the RF frequency is 960 MHz and the LO frequency is 950 MHz giving an IF frequency of 10 MHz. Figure 8. Harmonic Balance block The parameters measured to determine the mixer performance are the conversion gain, the LO to IF and LO to RF isolation or leakage. The following graphs (Figure 9) represent the frequency spectrum measured at the RF port and the LO ports. Figure 9. Frequency Spectrum for RF and IF ports From the graphs we can calculate the Conversion Gain, LO to IF leakage and LO to RF isolation by measuring the amplitudes in dB of the components in the Harmonic Balance simulation. Table 1 summarizes the obtained results. Conversion Gain 7.993 dB LO to IF leakage LO to RF isolation 11.172 dB 16.53 dB Table 1. Mixer simulation results CONCLUSION AND FUTURE WORK The remaining Challenges of the Mixer design could be to replace the load resistors for active loads and to minimize the LO to IF leakage to have a more linear path between the RF and the IF ports. Another potential improvement is to reduce the number of transistors by biasing the NMOS devices using only one current source at the bottom to the mixer circuit. Regarding the LNA design, the 25 input resistance must be replaced by an active load and some parameter needs to be changed in order to reduce the total current from ~75 mA to less than 5 mA. Also a higher voltage supply for the LNA should be used; probably using the same value for VDD as the mixer of 3.3 V. BIBILOGRAHPY 1. 2. 3. 4. 5. VLSI for Wireless Communications, Bosco Leung RF Microelectronics, Behzad Razavi RFIC MOS Gilbert Cell Mixer Design (Design Semminar), Steve Long A 2.5 V high linearity CMOS mixer for 1.9 GHz Applications, Vikas Chandra CMOS LNA in wireless applications, Shijun Yang, Ralph Mason and Calvin Plett