Main memory

Main memory

Hardware

CPU is faster than main memory, we need to add a ”gearbox” between the cpu and the memory; cache!

Base + limit registers protect processes from each other. (Used for comparison at addressing)

Adress binding

Giving a user program a physical adress space

(Using a programming analoug here…)

Compile time; absolute code is generated (”constant” addresses, recompilation is needed if changed).

Load time; relocatable code (”static” addresses, can change, but not without reloading user code)

Execution time; (”variable” addresses; can change at runtime)

Logical vs physical addresses

Logical = cpu’s view

Physical = memory unit’s view

Address space; the set of all addresses as seen by a user (logical) or the corresponding cpu (physical)

Mapping between theses is done by MMU

Relocation register (in the MMU)

Dynamic loading (load only when used); programmers responsibility

Dynamic linking; at execution time using a ”stub”

Swapping

Swap out a process to free memory (and resources).

Swapped out process; in a ready queue

Swap time (one way!) o (process_size / backing_store_transfer_rate) + latency + seek_time

Time quantum > swap time; if not, time is wasted.

Only swap idle processes!

Memory allocation

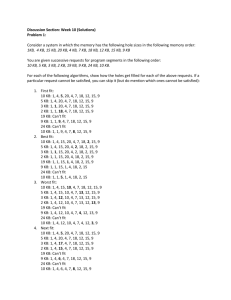

Contigous allocation

Partitions; fixed/variable size

Allocation algorithms o First-Fit, Best-Fit,Worst-Fit

External/Internal fragmentation (possible solution; compaction)

If non-contiguous allocation is ok;

Paging

Logical adress: page number (translated into a frame number via page table) + offset = physical address

Page/frame-size = hardware defined o Logical address space = 2 m bits, page size 2 n

bits, give a logical address: page number = m-n and page offset = n

Small page size = less internal fragmentation; if too small = I/O overhead

Example:

size of page table entry: 4 Bytes (32 bits) -> 2

32

physical page frames

Hardware

Registers for page table

Big tables; store table in main memory (pointed to by the Page-Table Base

Register) and introduce TLB to reduce overhead in memory access. o Effective memory access time =

(TLB_hit_ratio * mem_access) + (TLB_miss_ratio*(mem_access[page table] + mem_access[data]))

Protection; associate extra bits to each frame-entry

Page Table Structure

Problem : large page tables (2

32

logical address with page size 4 Kb

2

32

/2

12

entries

(1 milion) in the page table. 4 Byte entries = 4 MB PER PROCESS!

Solution : page the page table!

Split the page number bits in two (page + page[off_page_table] offset)

So, 64 bit architectures? With 3 (!) level paging we may have a page size of

2

34 bits. Do’h! o Introduce hashing

Inverted page table

Paging

Problem

: addresses are like a long array of bytes. User’s view; different segments, some contain function, other variables (and so on).

Solution : something very similar to basic memory management

Split a logical address space into segments.

Let the user use a two-dim. address; <segment-number; offset>

Segment table

Registers; segment base and limit

Segmentation fault (sounds familiar, eh?)