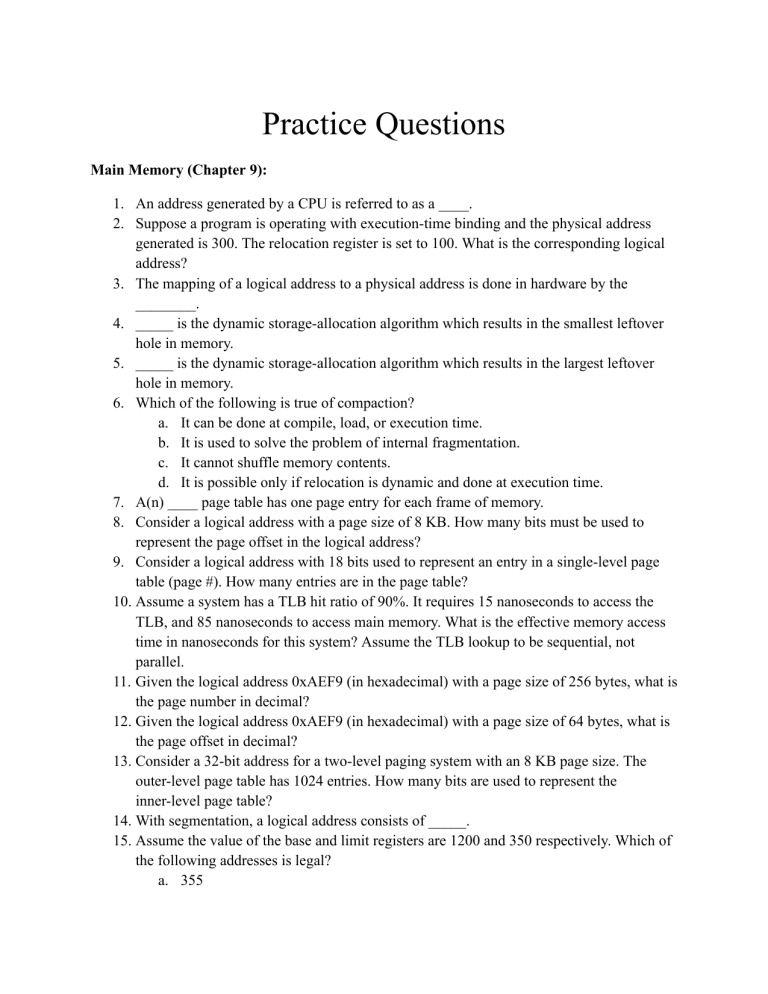

Practice Questions Main Memory (Chapter 9): 1. An address generated by a CPU is referred to as a ____. 2. Suppose a program is operating with execution-time binding and the physical address generated is 300. The relocation register is set to 100. What is the corresponding logical address? 3. The mapping of a logical address to a physical address is done in hardware by the ________. 4. _____ is the dynamic storage-allocation algorithm which results in the smallest leftover hole in memory. 5. _____ is the dynamic storage-allocation algorithm which results in the largest leftover hole in memory. 6. Which of the following is true of compaction? a. It can be done at compile, load, or execution time. b. It is used to solve the problem of internal fragmentation. c. It cannot shuffle memory contents. d. It is possible only if relocation is dynamic and done at execution time. 7. A(n) ____ page table has one page entry for each frame of memory. 8. Consider a logical address with a page size of 8 KB. How many bits must be used to represent the page offset in the logical address? 9. Consider a logical address with 18 bits used to represent an entry in a single-level page table (page #). How many entries are in the page table? 10. Assume a system has a TLB hit ratio of 90%. It requires 15 nanoseconds to access the TLB, and 85 nanoseconds to access main memory. What is the effective memory access time in nanoseconds for this system? Assume the TLB lookup to be sequential, not parallel. 11. Given the logical address 0xAEF9 (in hexadecimal) with a page size of 256 bytes, what is the page number in decimal? 12. Given the logical address 0xAEF9 (in hexadecimal) with a page size of 64 bytes, what is the page offset in decimal? 13. Consider a 32-bit address for a two-level paging system with an 8 KB page size. The outer-level page table has 1024 entries. How many bits are used to represent the inner-level page table? 14. With segmentation, a logical address consists of _____. 15. Assume the value of the base and limit registers are 1200 and 350 respectively. Which of the following addresses is legal? a. 355 b. 1200 c. 1551 d. all of the above 16. Distinguish between internal and external fragmentation. 17. Explain the basic method for implementing paging. 18. Describe how a Translation Look-aside Buffer (TLB) assists in the translation of a logical address to a physical address. 19. How is a limit register used for protecting main memory in contiguous memory allocation ? 20. (T/F) A relocation register is used to check for invalid memory addresses generated by a CPU. 21. (T/F) There is a 1:1 correspondence between the number of entries in the TLB and the number of entries in the page table. 22. (T/F) Hierarchical page tables are appropriate for 64-bit architectures. 23. (T/F) Fragmentation does not occur in a paging system. 24. (T/F) Inverted page tables require each process to have its own page table. 25. (T/F) A 32-bit logical address with 8 KB page size will have 219 entries in a single-level page table. 26. Given five memory partitions of 100 KB, 500 KB, 200 KB, 300 KB, and 600 KB (in order), how would each of the first-fit, best-fit, and worst-fit algorithms place processes of 212 KB , 417 KB , 112 KB , and 426 KB (in order)? Which algorithm makes the most efficient use of memory? Assume remaining spaces in holes are reused. 27. Most systems allow programs to allocate more memory to its address space during execution. Data allocated in the heap segments of programs are an example of such allocated memory. What is required to support dynamic memory allocation in the following schemes: a. contiguous-memory allocation b. pure segmentation c. pure paging 28. Compare the main memory organization schemes of contiguous memory allocation, pure segmentation, and pure paging with respect to the following issues: a. external fragmentation b. internal fragmentation c. ability to share code across processes 29. Assuming a 1 KB page size, what are the page numbers and offsets for the following logical address references (provided as decimal numbers): a. 256 b. 16385 30. Consider a logical address space of 32 pages with 1024 bytes per page; mapped onto a physical memory of 16 frames. a. How many bits are required in the logical address? b. How many bits are required in the physical address? 31. Consider a computer system with a 32-bit logical address and 4-KB page size. The system supports up to 512 MB of physical memory. How many entries are there in each of the following? a. A single-level page table? b. An inverted page table? 32. Consider the following segment table: Segment Base Length 0 219 600 1 2300 14 2 90 100 3 1327 580 4 1952 96 What are the physical addresses for the following logical addresses? a. 0,430 b. 1,10 c. 2,500 d. 3,400 e. 4,112 33. What is a piece of hardware that caches page number to frame number mappings? 34. Consider 64-bit logical addresses for a two-level paging system with 16 KB page size. The outer page table has 65,536 entries. How many inner-level page tables are needed for a process with 1 PB of size? 35. Derive a formula for question 34. 36. A hypothetical machine that is using virtual memory has 64 bit virtual addresses and 64 GB physical memory. Assume the page size is 4 KB and each page table entry requires 8 bytes of storage in memory. Compute the required page table size in bytes for a single process with 16 TB of size if: a. a single level page table is used. b. an inverted page table is used. c. a two-level page table is used with a 32 bit index for the outer-level page table. 37. Assume the portion of the page table for a process that is currently executing in CPU is as follows: Page size is 4 bytes, logical addresses are 5 bits, and the physical memory is 256 bytes. Convert the given logical addresses to corresponding physical addresses. All numbers are provided in decimal, and the answer should be given in decimal as well. a. Logical address 15 b. Logical address 23 Answer Key: 1. 2. 3. 4. 5. 6. 7. 8. 9. logical address 200 Memory-management-unit (MMU) Best fit Worst fit d Inverted 13 218 10. 11. 12. 13. 14. 15. 16. (15+85)x0.9 + (15+85+85)x0.1 = 90 + 18.5 = 108.5 174 57 9 segment number and offset b Fragmentation occurs when memory is allocated and returned to the system. As this occurs, free memory is broken up into small chunks, often too small to be useful. External fragmentation occurs when there is sufficient total free memory to satisfy a memory request, yet the memory is not contiguous, so it cannot be assigned. Some contiguous allocation schemes may assign a process more memory than it actually requested (i.e. they may assign memory in fixed-block sizes). Internal fragmentation occurs when a process is assigned more memory than it has requested and the wasted memory fragment is internal to a process. 17. Physical memory is broken up into fixed-sized blocks called frames while logical memory is broken up into equal-sized blocks called pages. Whenever the CPU generates a logical address, the page number and offset into that page is used, in conjunction with a page table, to map the request to a location in physical memory. 18. Two memory accesses are needed to access a byte in physical memory (one for the page-table, one for the byte), causing memory access to be slowed by a factor of 2. The standard solution to this problem is to use a TLB, a special, small fast-lookup hardware cache for the logical to physical address translation. If the translation is found in the TLB, then memory is accessed only for the byte, not for the page table. 19. When the CPU is executing a process, it generates a logical memory address that is added to a relocation register in order to arrive at the physical memory address actually used by main memory. A limit register holds the maximum logical address that the CPU should be able to access. If any logical address is greater than or equal to the value in the limit register, then the logical address is an invalid address and an error results. 20. F 21. F 22. 23. 24. 25. 26. F F F T First-fit: a. 212K is put in 500K partition b. 417K is put in 600K partition c. 112K is put in 288K partition (new partition 288K = 500K − 212K) d. 426K must wait Best-fit: e. 212K is put in 300K partition f. 417K is put in 500K partition g. 112K is put in 200K partition h. 426K is put in 600K partition Worst-fit: i. 212K is put in 600K partition j. 417K is put in 500K partition k. 112K is put in 388K partition l. 426K must wait In this example, best-fit turns out to be the best as it can place all four processes. 27. a. contiguous-memory allocation: might require relocation of the entire program since there is not enough space for the program to grow its allocated memory space. b. pure segmentation: might also require relocation of the segment that needs to be extended since there is not enough space for the segment to grow its allocated memory space. c. pure paging: incremental allocation of new pages is possible in this scheme without requiring relocation of the program’s address space. 28. The contiguous memory allocation scheme suffers from external fragmentation as address spaces are allocated contiguously and holes develop as old processes die and new processes are initiated. It also does not allow processes to share code, since a process’s virtual memory segment is not broken into noncontiguous fine-grained segments. Pure segmentation also suffers from external fragmentation as a segment of a process is laid out contiguously in physical memory and fragmentation would occur as segments of dead processes are replaced by segments of new processes. Segmentation, however, enables processes to share code; for instance, two different processes could share a code segment but have distinct data segments. Pure paging does not suffer from external fragmentation, but instead suffers from internal fragmentation. Processes are allocated in page granularity and if a page is not completely utilized, it results in internal fragmentation and a corresponding wastage of space. Paging also enables processes to share code at the granularity of pages. Contiguous memory allocation and segmentation do not suffer from internal fragmentation. 29. a. page # = 0; offset = 256 b. page # = 16; offset = 1 More explanation: This question does not mention anything about the total number of bits in logical addresses. Also, it does not mention the structure of the page table being used. If this happens, then assume there are enough bits to hold the given logical address, and also assume that the structure of the page table is single-level. Since page size is 1KB, the number of bits for the offset/displacement is 10 (as 2^10 = 1024). Just write the given logical address in binary; the right 10 bits will represent the offset and the rest of the bits on the left-hand side will represent the page number. 256 = 1 0000 0000. Please note that I did not write all the bits on the left of 1 as I don't know, or need to know, how many there are. What matters is that they are all 0! So, the address division is: 0000..0000 | 0100000000 Offset is 256 (right 10 bits), page number is 0 (the remaining bits on the left). 16385 = 100 0000 0000 0001. The address division is: 0000..0010000 | 0000000001 Offset is 1 (right 10 bits), page number is 16 (the remaining bits on the left). 30. a. 25 = 32 for the page number, and 210 = 1024 for the page offset, so a total of 15 bits for logical addresses. b. 24 = 16 for the frame number, and 210 = 1024 for the frame offset, so a total of 14 bits for the physical addresses. 31. a. 220 entries. b. 512 MB/4KB = 217 entries. 32. a. 219 + 430 = 649 b. 2300 + 10 = 2310 c. illegal reference, trap to operating system (segfault) d. 1327 + 400 = 1727 e. illegal reference, trap to operating system (segfault) 33. Translation Lookaside Buffer (TLB) or Associate Memory 34. 4 35. Every entry of an inner-level page table translates “page-size” amount of the process’ size. So, I full inner-level page table translates: (Number of entries in an inner-level page table) x (page size) bytes Therefore, the formula giving the number of inner-level page tables needed is: 𝑃𝑟𝑜𝑐𝑒𝑠𝑠 𝑆𝑖𝑧𝑒 𝐶𝑒𝑖𝑙𝑖𝑛𝑔( (𝑁𝑢𝑚𝑏𝑒𝑟 𝑜𝑓 𝑒𝑛𝑡𝑟𝑖𝑒𝑠 𝑖𝑛 𝑎𝑛 𝑖𝑛𝑛𝑒𝑟 𝑙𝑒𝑣𝑒𝑙 𝑝𝑎𝑔𝑒 𝑡𝑎𝑏𝑙𝑒) 𝑥 (𝑝𝑎𝑔𝑒 𝑠𝑖𝑧𝑒) ) 36. a. LA = 52,12, so Size = 252 x 8B = 255B or 32PB b. 64GB memory means 36 bit PA, which is divided as 24,12 Size = 224 x 8B = 227B or 128MB c. LA = 32,20,12 𝑃𝑟𝑜𝑐𝑒𝑠𝑠 𝑆𝑖𝑧𝑒 Inner tables needed = 𝐶𝑒𝑖𝑙𝑖𝑛𝑔( (𝑁𝑢𝑚𝑏𝑒𝑟 𝑜𝑓 𝑒𝑛𝑡𝑟𝑖𝑒𝑠 𝑖𝑛 𝑎𝑛 𝑖𝑛𝑛𝑒𝑟 𝑙𝑒𝑣𝑒𝑙 𝑝𝑎𝑔𝑒 𝑡𝑎𝑏𝑙𝑒) 𝑥 (𝑝𝑎𝑔𝑒 𝑠𝑖𝑧𝑒) ) = 𝐶𝑒𝑖𝑙𝑖𝑛𝑔( 16𝑇𝐵 20 12 2 𝑥2 44 ) = 𝐶𝑒𝑖𝑙𝑖𝑛𝑔( 2 𝐵 32 2 𝐵 12 ) = 2 Total Size = 1 outer and 212 inners = 1x232x8B + 212x220x8B = 235B+235B = 236B or 64GB 37. a. 15 = (011)(11). (011) is the page number portion, which is 3 in decimal, and it is mapped to frame 3 based on the page table given in the question (see table index 3). The corresponding physical address is: (000011)(11) = 15. b. 23 = (101)(11). (101) is the page number portion, which is 5 in decimal, and it is mapped to frame 63 based on the page table given in the question (see table index 5). The corresponding physical address is: (111111)(11) = 255.