Lab #11

advertisement

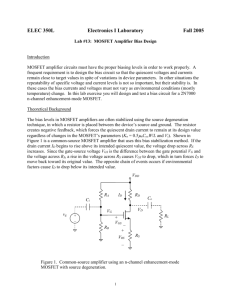

ELEC 350L Electronics I Laboratory Fall 2011 Lab #11: MOSFET Amplifier Bias Design Introduction Biasing is the process of selecting component values in an amplifier so that the proper quiescent voltages and currents in the circuit are established to meet a set of design goals. A frequent requirement is to have the quiescent voltages and currents remain close to target values in spite of variations in device parameters. In other situations the repeatability of specific voltage and current levels is not so important, but their stability in spite of temperature changes or other environmental variations is important. In this lab exercise you will design and test a bias circuit for a 2N7000 n-channel enhancement-mode MOSFET. Theoretical Background Bias levels in MOSFET amplifiers are often stabilized using the source degeneration technique, in which a resistor is placed between the device’s source and ground. The resistor introduces negative feedback that forces the quiescent drain current to remain close to its design value regardless of changes in the MOSFET’s parameters (kn or kp, and Vt) or environmental conditions. Shown in Figure 1 is a common-source MOSFET amplifier that uses this bias stabilization method. If the drain current ID begins to rise above its intended quiescent value, the voltage drop across RS increases. Since the gate-source voltage VGS is the difference between the gate potential VG and the voltage across RS, a rise in the voltage across RS causes VGS to drop, which in turn causes ID to move back toward its original value. Gate voltage VG is usually very stable because it is established by the voltage divider formed by RA and RB. The opposite chain of events occurs if ID begins to drop below its intended value. VDD RA ID RD Ci vg VG + VGS + − RB − VD + VDS − VS Co RL RS Figure 1. Common-source amplifier using an n-channel enhancement-mode MOSFET with source degeneration. The capacitors, source vg, and load RL are connected by dashed lines to indicate that they do not affect the DC biasing of the circuit. 1 of 6 The quiescent drain current ID in an amplifier with source degeneration must simultaneously satisfy the two relations 1 2 I D k n VGS Vt and VGS VG I D RS , 2 where Vt is the threshold voltage of the MOSFET, and kn is its transconductance parameter, given by W k n n C ox , L where n is the mobility of the free electrons in the inversion channel, Cox is the capacitance per unit area between the gate and the inversion channel, and W and L are the width and length, respectively, of the channel. The quantity VG is the gate voltage measured with respect to ground. Combining the two ID-VGS equations by eliminating VGS leads to a quadratic equation: 1 1 2 2 k n VG I D RS Vt k n VG Vt I D RS 2 2 1 2 I D k n VG Vt 2VG Vt I D RS I D2 RS2 2 2I D 2 VG Vt 2VG Vt I D RS I D2 RS2 kn ID 2 2 RS2 I D2 2 RS VG Vt I D VG Vt 0 . kn The solution is V Vt 1 1 ID G 2 RS k n RS 2 RS2 2 2 2 2 2 RS VG Vt 4 RS VG Vt k n VG Vt 1 1 2 RS k n RS 2 RS2 VG Vt R 1 1 4 8 S VG Vt 2 2 2 RS kn k n RS 2 RS kn VG Vt 1 1 2 RS k n RS 2 RS2 VG Vt 1 1 1 2k n RS VG Vt 2 RS k n RS k n RS2 4 RS2 VG Vt 8 2 RS VG Vt 42 4 RS2 VG Vt 2 kn kn . 4 2k n RS VG Vt 1 k n2 The sign ambiguity is resolved by applying the constraint VGS > Vt. Since VGS = VG – IDRS, then VGS Vt VG I D RS Vt 2 of 6 VG Vt ID . RS Substituting the expression for ID into the inequality makes it evident that the lower sign (− in the expression above) corresponds to the physically meaningful solution: VG Vt ID RS VG Vt VG Vt 1 1 1 2k n RS VG Vt 2 RS RS k n RS k n RS2 1 1 0 1 2k n RS VG Vt 2 k n RS k n RS2 1 1 1 2k n RS VG Vt (lower sign is correct) 2 k n RS k n RS2 Thus, ID VG Vt 1 1 1 2k n RS VG Vt . 2 RS k n RS k n RS2 A plot of this expression for ID versus kn shows that the drain current is relatively insensitive to this parameter. However, changes in the threshold voltage Vt can cause significant changes in ID. Nevertheless, the changes are much less severe than if the source resistor RS were not present. The complicated expression for ID derived above does not suggest a straightforward approach for selecting values of VG and RS to achieve a target bias level. Furthermore, the voltage transfer characteristic for this circuit, even with a source degeneration resistor, is nonlinear. It is therefore difficult to determine an optimum value to which the quiescent drain voltage VD and/or the quiescent drain current ID should be set. Because of the square-law nature of the relationship between ID and VGS, the output voltage swing is not symmetrical. In practice, many designers turn to a common rule of thumb in which the quiescent voltages across RD, the drain-source terminals of the MOSFET, and RS are simply each set equal to approximately one-third of VDD. That is, 1 I D RD VDS I D RS VDD , 3 from which the values for RD and RS can be found directly if the nominal value of ID is specified. (The bias level of the drain current is often dictated by the desired value for the small-signal transconductance gm.) The appropriate value of the quiescent gate voltage VG can then be found by once again combining the relationships ID 1 2 k n VGS Vt 2 and VGS VG I D RS , but this time solving for VG, which leads to 1 2 k n VG I D RS Vt 2 2I D VG I D R S V t kn ID VG I D R S Vt 3 of 6 2I D . kn The positive value of the square root is used because it corresponds to the requirement that VGS > Vt → VG − IDRS > Vt. Of course, this method for selecting the value of VG depends on knowing the values of kn and Vt, which vary considerably because of manufacturing tolerances and temperature effects. (The parameters n and Vt are especially sensitive to temperature.) For example, a typical range for Vt might be 1-3 V. It is therefore difficult, if not impossible, to set a quiescent drain current value that is repeatable from circuit to circuit. Bear in mind, however, that the presence of the source degeneration resistor RS will force the drain current to remain close to whatever value it happens to have. Thus, even though we cannot set ID to a specific value with much precision, we can make sure that it has negligible drift. In practice the nominal values of kn and Vt, obtained either from a data sheet or via measurements, are used to set VG. Since the value of VGS must be greater than Vt in order to avoid the cut-off region, it is often advisable to set VG slightly higher than the value suggested by the formula above. The voltage divider network formed by RA and RB establishes the value of VG in the circuit. Since zero current flows into the gate, VG is related to VDD by VG VDD RB . R A RB The parallel combination of the gate biasing resistors (i.e., RA || RB) is typically set to a large value (1 M or more) in order to maintain a high input impedance for the amplifier. In most design situations the actual value of ID is less important than ensuring that the MOSFET operates in the saturation region. Amplifiers like the one shown in Figure 1 are usually used with very small signals (peak-to-peak amplitudes of a few mV or less). In those cases the output voltage swing, and therefore the drain current swing, will be tiny compared to the corresponding quiescent values (a few millivolts vs. a few volts). Although the transfer characteristic of a MOSFET amplifier is nonlinear over its full extent, even in the saturation region, it is approximately linear over small portions of that range. The small-signal voltage gain is equal to the slope of the transfer characteristic at the Q-point. If the actual quiescent output voltage differs from its intended value, the small-signal voltage gain will differ from the target value as well, but usually the difference is not too great and can be tolerated in a practical circuit. If many copies of a circuit are needed with predictable bias levels, then it might be necessary to screen the stock of MOSFETs that will be used in the production of the circuit to eliminate those devices that have parameters outside the acceptable limits. If very precise bias control is required, however, then other types of biasing circuits should be used, such as those based on constant-current sources (e.g., current mirrors). Experimental Procedure Select a 2N7000 n-channel enhancement mode MOSFET from the available stock. Devise a way to use the circuit shown in Figure 2 to determine the parameters Vt and kn for the MOSFET without measuring any currents directly (i.e., make only voltage measurements). Use the 0-6 V power supply to create a variable gate-to-source voltage VGS, and adjust the 0-25 V power supply to provide a VDD of around 12 V. You will have to select an appropriate value for the drain resistor RD. Record the values of Vt and kn for the MOSFET. Demonstrate your test circuit and your parameter determination method to the instructor. 4 of 6 VDD ID RD VGS + − Figure 2. Test configuration for determining Vt and kn. Design a four-resistor bias circuit like the one shown in Figure 1 (with RD , RS, RA, and RB) for your 2N7000 MOSFET. Assume that the design specification calls for a power supply voltage VDD of 12 V, a quiescent drain current of ID = 10 mA, and a quiescent drain voltage of VD = 8 V (measured with respect to ground). Use any reasonable rule of thumb for the quiescent voltage across RS. Base your design on values for Vt and kn either deduced from the data sheet or measured by you. Each bias resistor should be a single unit with the standard value closest to the calculated value. For the gate biasing resistors, use values in the hundreds of k or M range. Insert three different MOSFETs into the four-resistor bias circuit, and measure the quiescent drain voltage VD for each one. In each case, calculate the percentage error by which the measured value of VD differs from the target value. Hold each MOSFET between your fingers for 30 seconds to warm it up, record the new VD value at the higher temperature, and calculate the percentage departure from the target value. Comment on the stability of the biasing circuit relative to device variation and temperature change. Demonstrate the biasing circuit to the instructor for one of the MOSFETs. Rebuild the circuit shown in Figure 2 using the same value for RD as you used in your fourresistor bias circuit. Insert one of the MOSFETs into the circuit, and adjust the value of VGS (the 6-V supply) until VD = 8 V. Hold the MOSFET between your fingers for 30 seconds, and then measure the new value of VD. Compare the temperature stability of this circuit to that of the four-resistor bias circuit. On a piece of paper separate from the notebook, list the Vt and kn values on which you based your bias circuit design, and list the resistor values (RD , RS, RA, and RB) you used. Provide a few calculations showing that the target quiescent values of ID and VD should have been achieved. Include some explanatory text. Grading Notebook entries will be assigned grades according to the criteria outlined in the “Policies and Grading Guidelines.” Notebooks must be submitted by 5:15 pm on the day of the lab session. The lab performance grade will be assigned according to the following guidelines. Each lab group member will receive the same grade. 5 of 6 40% 30% 30% Effective four-resistor bias network design Demonstration of an effective parameter determination method Demonstration of a properly operating biasing circuit © 2005-2011 David F. Kelley, Bucknell University, Lewisburg, PA 17837. 6 of 6