Address Decoders & Sample/Hold Circuits Assignment

advertisement

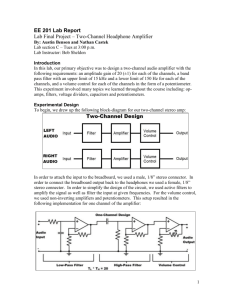

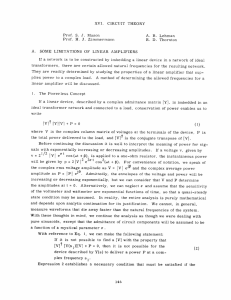

Basic addresses decoders and sample/hold circuits. (Range 1 exercise) Assignment: 1. Realize a simple decoder for an address 0EFh by multy inputs gate in combination with inverters. 2. Realize a full address decoder with integrated decoder and simple logic circuits. You have eight-bit address bus. Selection signals CS0-CS7 assign ascending. Address space is located in 0F8h-0FFh. 3. Realize a basic connection of sampling amplifier (S/H circuit) with LF398 to demonstrate its features. Check the influence of frequency of sampling on the credibility of the transmitted rectangular and triangular wave. Evaluate the effect of capacitor storage capacity and time of sampling on the accuracy of the processed signal. Theory: Basic decoders. When we have full decoding, the ADRIA address has assigned only one signal of the DEADRi and vice versa. Fig. 1 shows connection of the full address decoder. Fig. 2 is an example of the full address decoder based on 74138 circuit. If we have incomplete decoding, some place values of the system addresses aren’t considered because to signal DEADRi belongs address space ADRk, where k = 1, 2, 3... 74LS138 A0 A1 A2 A3 A4 A5 A6 A7 & DEADR\ 1 A0 A1 A2 A3 A4 A5 A6 A7 & 6,11,12 5V Fig. 1. Full address decoding 1 2 3 4 1 A 2 B 3 C 0 1 2 3 4 5 6 7 15 DEADR0\ 7 DEADR7\ 6 4 G1 /G2 5 /G3 74LS30 Fig. 2. Address decoder with 74138 circuit 7430 - 8 input NAND gate 74138 - 3bit demultiplexer with negated inputs. Input address is led to the inputs C, A, B. In this case, the address of the CAB determined which of the outputs Y0 - Y7 is set to log. 0. Other outputs are set to log.1. Circuit is suitable for the selection of circuits, which share part of the address bus and to be activated with log.0. 74139 - their behavior is very similar to the circuit 74138. These are two independent 2bit demultiplexer with negated outputs. For retrieve the addresses is used inputs A and B. The sampling amplifier (Sample-Hold circuit). Universal sampling amplifier tracer type (eg LF398) contains a memory, output amplifier and switching circuit with the exciter, enclosed in the feedback at input of charging amplifier. Memory capacitor is connected on the outside of package. Entrance of charge amplifier determines the accuracy of sensing the input voltage in the condition monitoring (S). Output of memory amplifier with input unipolar transistors determines the accuracy of remembering, whilst off the input voltage in a state of remembering (H). Threshold logic voltage of exciter is used for all logical lines. Size of external capacitor voltage is set as a compromise between speed and accuracy. Sampling amplifier is stable for any value of the memory capacitor. Active pins of sampling amplifiers are sensitive to noise leakage and capacitive currents from the power distribution and control input. LF398