Global routing

advertisement

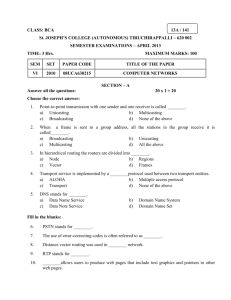

A Fast Crosstalk- and Performance-Driven Multilevel Routing System Tsung-Yi Ho, Yao-Wen Chang, Sao-Jie Chen D. T. Lee Graduate Institute of Electronics Engineering Department of Electrical Engineering National Taiwan University Taiwan Institute of Information Science Academia Sinica Taiwan 1 Agenda • • • • Introduction Multilevel Routing Framework Experimental Results Conclusions Performance-Driven Routing Tree Construction Crosstalk-Driven Layer/Track Assignment 2 Agenda • • • • Introduction Multilevel Routing Framework Experimental Results Conclusions 3 Routing Trends • Billions of transistors may be fabricated in a single chip with nanometer technology. • • Need tools for very large-scale designs. Framework evolution for CAD tools: Multilevel Hierarchical Flat Source: Intel at ISSCC-03 4 Two-Stage Routing • Global routing Partition the routing area into tiles. Find tile-to-tile paths for all nets. Optimize given objectives. • Detailed routing Assign actual tracks and vias for nets. 5 Flat and Hierarchical Routing Frameworks Flat Drawback: hard to handle larger designs Hierarchical Drawback: lack the global information for the interaction among subregions 6 Multilevel Framework • It has been successfully applied to partitioning, floorplanning, placement and routing in VLSI physical design and many more. • Ingredients: Bottom-up Coarsening: Iteratively groups a set of circuit components. Top-down Uncoarsening: Iteratively ungroups clustered components and refines the solution. 7 First Multilevel Router • Cong, Fang and Zhang, ICCAD 2001. Coarsening: Routing resource estimation Initial global routing: Multicommodity flow algorithm Uncoarsening: Refinement using constrained maze global routing algorithm … … 8 Routability- and Performance-Driven Multilevel Router • Lin and Chang, ICCAD 2002. This framework integrates global routing, detailed routing and resource estimation together at each level. 9 Our Multilevel Framework • An intermediate step (layer/track assignment) between coarsening and uncoarsening stage is introduced to do runtime and crosstalk optimization. Already-routed net To-be-routed net G0 Coarsening G1 Perform congestion-driven pattern routing for local connections and then estimate routing congestion for the next level. Uncoarsening G0 Coarsening Uncoarsening G 1 G2 G2 Use point-to-path maze routing to reroute failed nets level by level. Perform crosstalk-driven layer/track assignment for long segments, and short segments are routed by a point-to-path maze router. 10 Multilevel Routing Framework Comparison Coarsening stage Initial routing Uncoarsening stage Cong et al. in ICCAD 01 Resource estimation Multicommodity flow Global maze refinement Lin and Chang in ICCAD 02 Global routing Detailed routing Resource estimation No initial routing Global and detailed maze refinement Our Framework Global routing Resource estimation Track/layer assignment Global and detailed maze refinement 11 Multilevel Routing Framework Comparison Coarsening stage Initial routing Uncoarsening stage Cong et al. in ICCAD 01 Resource estimation Multicommodity flow Global maze refinement Lin and Chang in ICCAD 02 Global routing Detailed routing Resource estimation No initial routing Global and detailed maze refinement Our Framework Global routing Resource estimation Track/layer assignment Global and detailed maze refinement • Cong et al.’s framework Focus on global routing The precise relative positions of nets are not determined Insufficient information for addressing nanometer electrical effects (e.g., crosstalk) 12 Multilevel Routing Framework Comparison Coarsening stage Initial routing Uncoarsening stage Cong et al. in ICCAD 01 Resource estimation Multicommodity flow Global maze refinement Lin and Chang in ICCAD 02 Global routing Detailed routing Resource estimation No initial routing Global and detailed maze refinement Our Framework Global routing Resource estimation Track/layer assignment Global and detailed maze refinement • Lin & Chang’s framework Focus on routability-driven routing Most of nets are detailed routed (fixed) Not flexible to address nanometer electrical effects 13 Multilevel Routing Framework Comparison Coarsening stage Initial routing Uncoarsening stage Cong et al. in ICCAD 01 Resource estimation Multicommodity flow Global maze refinement Lin and Chang in ICCAD 02 Global routing Detailed routing Resource estimation No initial routing Global and detailed maze refinement Our Framework Global routing Resource estimation Layer/Track assignment Global and detailed maze refinement • Our new framework Fully utilizes the information of global router Nets are routed in parallel Suitable to address nanometer electrical effects 14 Agenda • • • • Introduction Multilevel Routing Framework Experimental Results Conclusions Performance-Driven Routing Tree Construction Crosstalk-Driven Layer/Track Assignment 15 Performance-Driven Routing Tree • Minimum Spanning Tree (MST) Has the smallest total wire length c May incur longer path length • Shortest Path Tree (SPT) SPT MST Has the shortest path length May incur larger total wire length c c Minimum Radius Minimum Cost Spanning Tree (MRMCST) is proposed for performance-driven routing tree construction. 16 Union of All MSTs • Construct union and intersection graphs of all MSTs to preserve the minimum cost. 4 3 5 1 2 6 No Only One Component? 7 Yes 17 Union of All MSTs • Construct union and intersection graphs of all MSTs to preserve the minimum cost. 4 3 5 1 2 6 7 Time complexity: O(n lgn) How to choose the right optional edges? 18 Preprocessing • Every blue component should keep Pseudo-center (pc): center of the longest path Distance of every node to its pc Radius from pc Optional edges incident to the blue component pc1 B2 B1 pc2 19 Locally Optimal Connection Strategy (LOCS) • LOCS: Choose an edge e = (p, q) to minimize the cost f(e, T) = dist(s, p) + cost(e) + dist(q, pc(T)) + RT • Prim-like algorithm • RT O(n+moptlogmopt) Number of nodes needed to update the distance from the source s Use a heap structure to choose optional edges s p T pc q 20 Routing Model • • Partition a chip into tiles Multilevel routing graph G = (V, E) Each node in V denotes a tile Each edge in E denotes the boundary of adjacent tiles 21 Global Routing • Pattern routing Uses L-shaped and Z-shaped connections to route nets. Has lower time complexity than maze routing. ! " " ! " #! " 22 Resource Estimation • Global routing cost is the summation of congestions of all routed edges. • The congestion, Ce, of an edge e is defined by Ce = 1 2 ( pe − d e ) , where pe and de are the capacity and density, respectively. • We update the congestion of routed edges to guide the subsequent global routing. 23 Agenda • • • • Introduction Multilevel Routing Framework Experimental Results Conclusions Performance-Driven Routing Tree Construction Crosstalk-Driven Layer/Track Assignment 24 Coupling Capacitance Induced Crosstalk • Coupling capacitance is more significant than self capacitance in deep submicron era Devices and wires are placed in closer proximity Wire heights scale at a slower rate than widths • Coupling capacitance is proportional to coupling wire length and inversely proportional to spacing distance. smaller device sizes Coupling can account for up to 70% of interconnect Sylvester et al, in Proc. VLSI capacitance even in .25 micron designs. Symposium on Technology, 1998. 25 Coupling Capacitance Induced Crosstalk • Crosstalk Caused by coupling capacitance Leads to functional failure and wire delay • Global routing Precise net positions are not determined yet and thus only some sort of estimation can be done. • Detailed routing Most nets are fixed and thus it is not flexible to handle the wire coupling A Desirable Intermediate Step: Layer/Track Assignment 26 Crosstalk-Driven Layer Assignment b d e c a Chip Layout To avoid two segments with larger overlap adjacent to each other on the same layer, we need to separate them to different layers. f 1 2 3 4 a 1 1 2 Panel b 2 3 2 f 2 Graph k-coloring heuristic on MST to separate segments to k layers 1 1 c 4 2 1 2 1 3 d Interval Graph Maximum spanning tree heuristic to extract edges with larger cost e 27 Crosstalk-Driven Track Assignment b d e c a f 1 2 Extract the maximum clique in the interval graph 3 4 a 1 b 1 2 c 4 2 3 d Interval graph c d 1 e b 3 2 f a a e 1 2 3 4 f Bipartite assignment graph b 1 c 2 d 3 e 4 f Combined graph 28 Crosstalk-Driven Track Assignment b d e c a f b 1 2 Select the segment with the maximum degree in the clique as the starting point 3 4 a 1 b 1 2 c 4 2 3 d Interval graph c d 1 e b 3 2 f a a e 1 2 3 4 f Bipartite assignment graph b 1 c 2 d 3 e 4 f Combined graph 29 Crosstalk-Driven Track Assignment b d e c a f b 1 Remove edges corresponding to segments that can be allocated on track 1 but are overlapped with segment b 2 3 4 a 1 b 1 2 c 4 2 3 d Interval graph c d 1 e b 3 2 f a a e 1 2 3 4 f Bipartite assignment graph b 1 c 2 d 3 e 4 f Combined graph 30 Crosstalk-Driven Track Assignment b d e c a f b 1 f 2 e 3 Assign the remaining segments in the clique to tracks d 4 a 1 b 1 2 c 4 2 3 d Interval graph c d 1 e b 3 2 f a a e 1 2 3 4 f Bipartite assignment graph 1 c 2 d 3 e 4 f Combined graph 31 Crosstalk-Driven Track Assignment b d e c a f b 1 c a 2 Choose the next maximum clique for track assignment till all segments are assigned f e 3 d 4 a 1 b 1 2 c 4 2 3 d Interval graph c d 1 e b 3 2 f a a e 1 2 3 4 f Bipartite assignment graph 1 c 2 d 3 e 4 f Combined graph 32 Our Multilevel Framework Recap Already-routed net To-be-routed net G0 G0 Coarsening G1 Perform congestiondriven pattern routing for local connections and then estimate routing congestion for the next level. Coarsening G2 Uncoarsening Uncoarsening G1 G2 Use point-to-path maze routing to reroute failed nets level by level. Perform crosstalk-driven layer/track assignment for long segments, and short segments are routed by a point-to-path maze router. 33 Agenda • • • • Introduction Multilevel Routing Framework Experimental Results Conclusions 34 Experimental Settings • Language: C++ • Platform: 1GHz Sun Blade 2000 with 1GB memory • Library: STL, LEDA, LayoutDB (UCLA) • Benchmarks taken from previous works: Circuits Size ( m) #Layer #Nets #Pins S5378 4330x2370 3 3124 4734 S9234 4020x2230 3 2774 4185 S13207 6590x3640 3 6995 10562 S15850 7040x3880 3 8321 12566 S38417 11430x6180 3 21035 32210 S38584 12940x6710 3 28177 42589 35 Routability and Running Time • Obtained about the same routability • Achieved about 6.7X speedup, used 2X memory Circuits Results of Lin and Chang (ICCAD 2002) Our Results Time (s) Memory (MB) #Failed nets Time (s) Memory (MB) #Failed nets S5378 35 18 5 10.6 34 5 S9234 26.2 14 4 8.1 33 2 S13207 106.7 24 7 22.6 53 10 S15850 538.8 40 31 62.6 79 19 S38417 899.9 75 57 71.3 160 33 S38584 1953.7 496 59 255.6 977 54 Avg 6.7 1 1.4 1 2.1 1 36 Delay and Crosstalk Circuits Results of Lin and Chang (ICCAD 2002) Our Results Dmax Davg Cmax Cavg Dmax Davg Cmax Cavg S5378 37308 1403 507 25.4 27577 1258 342 20.2 S9234 25512 1072 579 21.7 23591 1009 426 17.8 S13207 55337 1262 1526 29.2 52034 1243 1211 22.7 S15850 76297 1302 2913 28.3 68317 1253 2274 22.9 S38417 121419 1170 5704 25.6 105575 1146 4732 20.9 S38584 150936 1208 23196 26.8 131877 1151 18810 22.6 avg 1.2 1.1 1.3 1.2 1 1 1 1 Dmax: Critical path delay (ps) Davg: Average net delay (ps) 15 % Reduced about Coupling capacitance is 5 % not included in delay computation for fair comparison Cmax: Maximum coupling length () 30 % Cavg: Average coupling length () 24 % 37 Routing of s5378 Example of a routing result with GUI (s5378) 38 Agenda • • • • Introduction Multilevel Routing Framework Experimental Results Conclusions 39 Conclusions $ We have proposed a novel multilevel routing framework that is suitable to address nanometer electrical effects. $ Compared with the state-of-the-art previous work, our approach achieved a 6.7X runtime speedup, reduced the respective maximum and average crosstalk by about 30% and 24%, reduced the respective maximum and average delay by about 15% and 5%. Future work lies in multilevel routing considering other nanometer electrical effects such as antenna effect. $ 40 Thank You !! 41