ECE471/571 Energy E cient VLSI Design Introduction Setup

advertisement

ECE471/571 Energy Ecient VLSI Design

Project 2 Cadence Setup and Creation of an Inverter

Due Date 11:30pm on Friday, January 30th 2015

Introduction

This project will rst walk you through the setup for use of the

0.25µm process with Cadence Design Framework II. Then

you will create the schematic, symbol, and layout of an inverter. Much of the information in this lab manual was taken

from Dr. Moon's Design Framework Tutorial. For more information you can refer to his page at:

http://web.engr.oregonstate.edu/~moon/ece423/cadence/

Setup

Following these steps will help you setup the Cadence Design Framework.

1. To run Cadence, you just need to have

/usr/local/apps/bin

in your path (this is valid both for the ECE and

for the ENGR machines). To check this go to your home directory and look at the

.cshrc

PATH

variable inside of your

le.

2. To setup Cadence you must create a directory inside of your ECE471 folder named cadence in which you can

save your Cadence projects. Change your current directory to

cadence.

Once you have changed your current

directory to your Cadence project directory, run the Cadence setup script by typing the following command at the

terminal:

/nfs/guille/u1/c/cdsmgr/cdsmgr/process/CDK1.4/tsmc025/setup

This sets your directory to work with the TSMC 0.25µm process and copies

3. Next you will need to edit your

.cshrc le.

the appropriate les to that directory.

This le is found in you home directory, and it is a hidden le (it starts

with a '.'). If you're using a graphical le browser, simply specify that hidden les should be displayed. If you use

a terminal window, you can nd the le by typing

.cshrc

setenv

setenv

setenv

setenv

ls -all

or many other commands. Once you've found the

le, open it in a text editor and append the following commands to the end of the le:

CDS_SITE /nfs/guille/u1/c/cdsmgr/cdsmgr/pdk/CDK1.4/local

SKIP_CDS_DIALOG 0

USE_NCSU_CDK 0

CDS_Netlisting_Mode Analog

4. You must also replace one of the cadence initialization les. The script above creates some basic init les. Unfortunately, the layout tool will not work unless you replace the

.cdsinit le that was placed in your cadence directory.

.cdsinit. Remember, this is

Simply save the cdsinit le from the lab webpage in your cadence directory as

a hidden le, so you won't be able to see it unless you specify that you want to view hidden les.

5. Now you'll need to change a location in one le.

Open cds.lib and change any line with

/nfs/guille/u1/c/cdsmgr/ This can be done with a simple sed if you prefer:

sed "s/~cdsmgr/\/nfs\/guille\/u1\/c\/cdsmgr\/cdsmgr/g" cds.lib

~cdsmgr/

to

6. Next you must add the local cadence icfb shortcut le. Download this le below and copy it into your newly created

cadence folder. Then change the permissions to ensure its executable (either

chmod u+x icfb

le in your le browser, right click, go to the permissions tab and select the executable box).

7. You can now start DFII by typing

./icfb

from that directory.

1

or browse to the

Creating a layout

This section will walk you through the process of creating a design and layout. In this case, we will make an inverter.

Create a library for your new design

From the library manager window go to:

F ile → N ew → Library

Type a new name, such as ECE471. Under the heading Technology File, choose Compile a new techle. Then

from the drop-down menu choose TSMC 0.24u CMOS025/DEEP (5M, HV FET) . Click OK.

Create a new cell, where you will design the inverter

In Library Manager, highlight your new library (ECE471 if that is what you chose). Go to:

F ile → N ew → Cellview

Choose library ECE471, cell name inverter, view name schematic, and Tool Composer- Schematic. Click OK.

Design your circuit

The next step is to create the schematic for your circuit.

Placing components

For this inverter, you will need a nmos transistor, a pmos transistor, and power and ground nodes.

•

From Schematic window:

Add → Instance

The Add Instance and Component Browser windows will open. Make

sure the Library in the Component Browser is set to

•

NCSU_Analog_Parts.

Use the Component Browser window ('i' is hot key for Component browser instantiate) and single click

then select

nmos4

N_Transistors,

pmos4) Esc

and place it. Place the component. Do the same for a pmos (P_Transistors and

hot key helps you to escape.

•

Also, from the

NCSU_Analog_Parts,

get the symbols for

vdd

and

gnd

from

Supply_Nets

(they dene the net

names for the power and ground nodes).

•

Create input and output pins by pressing 'p'. Give each pin an appropriate name and select the proper direction

(input or output).

•

To size the transistors properly rst highlight the NMOS transistor and press 'q', then change the width to 480nm.

Next change the PMOS width to 960nm. Be sure to include the 'nm' postx.

•

Use wires to connect the parts accordingly (Be sure that the PMOS bulk is connected to

is connected to

•

Go to:

gnd).

Design → Check and Save

vdd, and the NMOS bulk

to save the design and check for any errors. If there are errors, they will show

up in the icfb log window.

Some other hot keys are 'f' for re-centering screen and 'w' for placing wires.

Generating HSPICE netlist from schematic

T ools → Analog Environment → Simulation → N etlist → Create F inal. To save the

F ile → Save As and type in the full path to where you want it saved. (For example, mine would be save

location: ~/ECE471/Lab2/netlist.spi)

To create a netlist, go to

netlist go to

in the

2

Creating a symbol

Creating a symbol for your circuit is useful for integration into a larger design. If you are creating a circuit that uses

inverters, it is handy to view the inverters in a schematic as the inverter symbol, rather than just seeing it at transistor

level.

•

In your schematic window go to:

View Name

Design → Create Cell view → F rom Cell view.

To View Name eld is symbol. Press OK.

Make sure that the

From

eld is schematic, and the

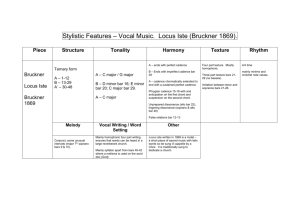

Figure 1: Schematic symbol of an inverter.

•

We want the our symbol to simply look like this inverter symbol seen in gure 1. To do this, go to

Add → Shape

and add the necessary shapes (use polygon to create a triangle). Your nal symbol should match gure 2.

Figure 2: Final symbol of an inverter.

Creating the layout

•

To start a new inverter layout, go back to the library manager window, highlight your ECE471 library and go to:

F ile → N ew →→ Cell view.

In the

View Name

eld put layout, and in the

Tool

eld select Virtuoso. Press

OK.

•

To add new parts, once again press 'i'. Choose Browse, and highlight:

layout.

N CSU T echLib → tsmc03d → nmos →

Change the width to 480nm, then go ahead and place the NMOS on the grid. Repeat this process with

the PMOS (changing the width to 960nm), and place it above the NMOS, and then press Shift+f keys. Your

screen should look similar to gure 3.

3

Figure 3: Layout with NMOS and PMOS mosfets.

•

Now we want to connect the drains of the transistors. To do this, go to the LSW window and highlight the

box, press 'r', and draw

metal1

metal1

connecting both drains to each other similar to gure 4.

Figure 4: Metal connecting mosfets.

•

Now we need to connect the gates, select the poly

drw

to gure 5.

4

box in the LSW window, and connect the gates similar

Figure 5: Gates connected.

•

Next we will place the ntap and ptap. For the ntap press 'i', then select browse and highlight:

tsmc03d → ntap → layout

N CSU → techLib →

and place it as shown in gure 6, then add the ptap in a similar manner.

Figure 6: Mosfets with taps.

•

Using M1 (metal1), connect the source of the NMOS to

5

gnd

and PMOS to

vdd

as shown in gure 7.

Figure 7: Connecting to supply rails.

•

We want for our in pin to connect on

to use vias. Press 'i', and highlight:

metal1, and our out pin to connect on metal3. To do this we will have

N CSU T echLib tsmc03d → M 1 − P oly → layout, and place the connector

as shown in gure 8 for the input. For the output, compound an M1-M2 connector with a M2-M3 connector as

shown in gure 8. We will also take both M1 and M3 and extend the input and output.

Figure 8: Input and output pins.

•

Next we want to place the pins. Go to:

input. Change Pin type to

metal1.

Create → P in, change the terminal name to in and set the I/O type to

Display Pin and change layer to metal1-dg. Repeat this process

Click on

for the out pin, making all the necessary changes. Make sure the pins are placed on the appropriate spots (on

the appropriate metal layers).

6

•

Finally, we want to add

vdd

and

gnd.

These will be added using pins, but this time, the I/O type will be set to

Input/Output. Set the metal layer properly and place the pins on the correct locations.

Running DRC/Parasitic Extraction

•

Go to

V erif y → DRC

and press OK. If your design has any errors they will show up in your icfb Log window. If

you have errors take a look at them and see if you can x them.

•

To do parasitic extraction go to:

V erif y → Extract, in that window select: Set Switches → Extract P arasitics Caps

and press OK. ICFB should show you no errors. There will be a new cell called extracted in your Cadence Library

Manager, open this up.

•

In this window go to:

T ools → Analog Environment → Simulations → N etlist → Create F inal.

This will

create the new netlist containing your extracted view.

What to turn in

Turn in a PDF to TEACH by Friday, January

30th

by 11:30pm with the following things:

•

Screenshots of your completed, error free schematic and HSPICE schematic netlist.

•

A screenshot of your completed symbol.

•

Screenshots of your completed, DRC clean layout, and your extracted HSPICE netlist.

•

An explanation of any problems you may have had.

•

Answer to the following question:

Why is it important to simulate your circuit both after schematic and post-layout? (after parasitic extraction)

7