Chapter 5

advertisement

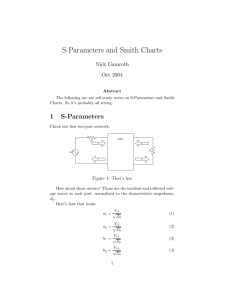

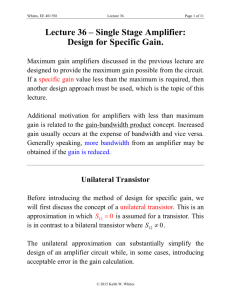

Chapter 5. Linear RF Amplifier Design 5.1 Understanding RF Transistor Data Sheet 5.2 S Parameter Charting for RF Design 5.2.1 Power Gain Equations 5.2.2 Amplifier Stability and Stability Circles 5.2.3 Constant Gain Circles 5.2.4 Constant Operating Power Gain Circles (Bilateral Case) 5.2.5 Constant Noise Figure Circles 5.3 DC Biasing Circuit Design 5.3.1 DC Biasing Circuits for RF Silicon Transistor 5.3.2 DC Biasing Circuit for RF GaAs MESFET 5.3.3 Biasing Circuit Design 5.4 Design Methodology 5.4.1 Initial Design Sequence 5.4.2 Design for Specific Unilateral Power Gain Greq 5.4.3 Design for Maximum Unilateral Power Gain 5.4.4 Design for Unilateral LNA with Specific NF and Power Gain 5.4.5 Design for Specific Power Gain with Bilateral Devices 5.4.6 Design for Optimum NF (Bilateral Method) 5.5 RF Amplifier Performance Parameters 5.5.1 1 dB Compression Point 5.5.2 Two Tone 3rd Order Intercept Point 77 5.1 Understanding RF Transistor Data Sheet • Gain band width product The transition frequency or gain bandwidth product ft is the theoretical frequency at which the common emitter current gain, hfe is equal to unity or 0 dB. This is basically the upper operation frequency limit of the transistor. In practice, ft is only useful as a criteria for comparing the transistors since when hfe is unity, we may still achieve power gain in the presence of voltage gain. In practice, ft should be as high as economically feasible, 3X ~ 5X that the highest operating frequency is a good guide. • DC Current Gain The DC current gain (hFE) is very important for bias circuit design of RF transistors. The range or variation of hFE is important, especially in the selection of biasing topologies (for example, passive or active) to ensure quiescent point stability. • Noise Figure Noise factor (F) of a transistor is simply a measure of how much noise the transistor adds to the signal during the amplification process or a measure of the degradation in the signal to noise ratio (SNR) between the input and output ports of the network. Noise figure is given as (NF = 10 log F dB). The potential NF of a transistor is critical in the design of low noise amplifier (LNA) for receiver’s front end. Noise quoted in data sheet is always optimum and is not realizable easily in the actual design. Noise Figure is dependant on: 1. ICQ or IDQ 2. Source impedance 3. Operating frequency. 78 • Intended application Pay attention to the intended applications of the transistor from the manufacturer as it is usually optimized for such applications. • Maximum Rating When operating at RF with high Q tuned circuit, it may result in circuit voltage exceeding supply voltage by a few times depending the circuit configuration. Basic RF Amplifier Design Sequence Using the data sheet and based on the design requirements (such as NF, frequency, gain, linearity etc.) we need to 1) Select a Q point Vceq & Icq for BJT and Vdsq & Idq for FET. In general, for linear amplifier design Vceq and Vdsq is usually taken at half the system supply voltage. This implies that the selection of Q point generally only requires the designer to choose an appropriate Icq and Idq. 2) Measure the S parameters The S parameters must be measured at the selected Q point and the desired operating frequency. This is because the S parameters are highly dependent on these two operating conditions. 3) Design and realize the amplifier following design methodology to be covered later in this module. 5.2 S Parameter Charting for RF design • In the microwave range, H, Y and Z parameters can’t be measured effectively because - Equipment is not readily available to measure total voltage and current at the ports of network at high frequencies. 79 - Short and open circuits are difficult to achieve at high frequencies. - Active devices usually are not stable under short or open circuit conditions. • H parameters V1 = h11I1 + h12V2 I2 = h21I1 + h22 V2 • Y parameters I1 = Y11 V1 + Y12V2 I2 = Y21V1 + Y22V2 • Z parameters V1 = Z11I1 + Z12I2 V2 = Z21I1 + Z22I2 • S parameters S parameters make use of travelling waves (rather than V or I) and are characterized at a known impedance (50 Ω). Fig.5-1: Two ports network for S parameters b1 = S11a1 + S12a2 b2 = S21a1 + S22a2 Where S11 = the input reflection coefficient S12 = the reverse transmission coefficient S21 = the forward transmission coefficient S22 = the output reflection coefficient 80 And b1, b2, a1 & a2 are travelling waves with direction as indicated above. • Linear RF Amplifier Design using S parameters Fig.5-2: Reference Block diagram for Linear Design Using S parameters Z’L = actual load impedance Z’s = actual source impedance ZL = transformed load impedance seen by the output of the active device Zs = transformed source impedance seen by the input of the active device • The RF amplifier design objective is to determine the proper values of Γs and ΓL to achieve a given gain target. Γ= Z − Zo Z + Zo Z = 1 + Γ Zo 1− Γ Z0 = characteristic impedance 5.2.1 Power Gain Equations 1. Transducer Power Gain Gt • Gt is the ratio of output power delivered to the load over the maximum input power available from the source to the network. 81 • It is the actual gain of an amplifier stage including the effects of input and output matching network and device gain. Gt = 1 − Γs 1 − ΓL 2 1 − Γin Γs S 21 2 2 2 1 − S 22 ΓL 2 or Gt = 1 − Γs 2 1 − S11Γs 2 S21 2 1 − ΓL 2 1 − Γout ΓL 2 where Γin = S11 + S12 S 21ΓL S11 − ∆ΓL = 1 − S 22 ΓL 1 − S 22 ΓL Γout = S 22 + ΓL = S12 S 21 Γs S 22 − ∆Γs = 1 − S11 Γs 1 − S11 Γs Z L − Zo Z L + Zo Γs = Z s − Zo Z s + Zo ∆ = S11 S 22 − S12 S 21 2. Operating Power Gain Gp • Gp is defined as the ratio of the power delivered to load PL to the power input to the network from the source Pin. • For Γs = Γin*, when the input is conjugately matched, from the transducer power gain equation we have: Gp = 1 − ΓL 2 PL 2 1 = S21 2 2 Pi n 1 − Γ 1 − S22 ΓL in Where 82 Γin = S11 + S12 S 21ΓL S11 − ∆ΓL = 1 − S 22 ΓL 1 − S 22 ΓL ∆ = S11S22 –S12S21 • This equation can be expressed as Gp = S212 gt Where gt = = = 1 − ΓL 2 S − ∆ΓL 1 − 11 1 − S 22 ΓL 1 − ΓL 2 1 − S 22 ΓL 2 1 − S 22 ΓL − S11 − ∆ΓL 2 1 − ΓL 2 2 1 − S11 + ΓL 2 2 2 S 22 − ∆ 2 2 − 2 Re ΓL C 2 C2 = S22 - ∆S11* 5.2.2 Amplifier Stability and Stability Circles • The tendency of a transistor toward oscillation can be determined by its S parameters. • The calculation can be made even before an amplifier is built and thus, it serves as a useful tool in finding a suitable transistor for your application. • The condition for a two-port to be unconditionally stable is (assumed |ΓS|<1 and |ΓL|<1): 83 Γin = S11 + S12 S 21ΓL <1 1 − S 22 ΓL Γout = S 22 + S12 S 21Γs <1 1 − S11Γs • These inequalities can be reformulated to: K > 1 and |∆| < 1, where ∆ = S11S22 –S12S21 2 K= 2 1 + ∆ − S 11 − S 22 2 2 S12 S 21 • K is called the Rolett Stability Factor. Thus, a simple stability check can be performed for a given device in the very beginning of the design work. The outcome of this stability check will determine the design methodology that should be used. • When we have |Γin| > 1 or/and |Γout| >1, the device is unstable and oscillation may occur. • So |Γin| =1, or/and |Γout| = 1 are the boundary condition, the maximum limit of input and output reflection coefficients before the amplifier become unstable. • |Γin| and |Γout| are function of ΓL and Γs respectively. For example, if we try to solve: Γin = S11 − S12 S 21ΓL =1 1 − S 22 ΓL It is found that the solution is not unique and they form a circle. 84 • The stability circle is simply a circle on a Smith Chart which represents the boundary between those values of source or load impedance (reflection coefficient) that cause instability and those that do not. • The perimeter of the circle represents the locus of points which forces |Γin| = 1 or |Γout| = 1. Either the inside or the outside of the stability circle may represent the unstable region. • Computation of center and radius of input and output stability circle. Input stability circle: radius center rs = cs = S12 S 21 S11 − ∆ 2 2 S11* − ∆*S 22 S11 − ∆ 2 2 Output stability circle: radius center rL = cL = S12 S 21 S 22 − ∆ 2 2 * S 22 − ∆* S11 S 22 − ∆ 2 2 • If the transistor is unconditionally stable, stability circles don’t need to be plotted. • However, if the transistor conditionally stable or potentially unstable, we must plot the stability circles. 85 • Once the stability circles are plotted on the Smith Chart, the next step is to determine which side of the circle represents the stable region. • When we measured the S parameters of transistor with a 50Ω source and load and if the transistor remained stable under these condition (S11 <1 and S22 < 1), then the center of the normalized Smith chart (which represents 50 Ω) must be part of the stable region. • If one of the circles surrounds the center of the chart, the inside of that circle must represent the region of stable impedances for that port. • Thus, the stability criteria are: K > 1 and |∆| < 1 - Unconditionally stable ||cs| - rs| > 1 and |S22| < 1 ||cL| - rL| > 1 and |S11| < 1 The stability circles have K > 1 and |∆| > 1 K < 1 and |∆| < 1 - Potentially unstable ||cs| - rs| < 1 and |S22| < 1 ||cL| - rL| < 1 and |S11| < 1 The stability circles have: Fig.5-3: Unconditionally stability circles 86 Fig.5-4: Conditionally stable circle. (a) Stability circle does not encircle the center of Smith Chart; (b) Stability circle encircles the center of Smith Chart 87 Example 5-1: A certain MESFET has the following S parameter measured at 9 GHz with a 50 Ω reference. S11 = 0.64∠ -170° S21 = 2.10∠ 30° S12 = 0.05∠ 15° S22 = 0.57∠ -95° Compute: (a) the delta factor ∆, (b) the stability factor K, and (c) plot the input and output stability circles. Solution: a) The delta factor is ∆ = 0.64∠ -170°x 0.57∠ -95°- 0.05∠ 15°x 2.1∠ 30°= 0.30∠ 111.45° |∆| = 0.30 < 1 b) The stability factor K is 1 + 0.30 − 0.64 − 0.57 = 1.71 > 1 K= 2 × 0.05 × 2.10 2 2 2 c) For input stability circle S11* - ∆*S22 = 0.64∠ 170° - 0.30∠ -111.45°x 0.57∠ -95° = 0.48∠ 176.42° The center and radius of the input stability circle are 176.42° = 1.50∠176.42° cs = 0.48∠ 2 2 0.64 − 0.30 rs = 0.05 × 2.10 0.64 − 0.30 2 2 = 0.33 For output stability circle S22* - ∆*S11 = 0.57∠ -95° - 0.30∠ -111.45°x 0.64∠ -170° = 0.39∠ 103.32° 88 The center and radius of the input stability circle are 103.32° = 1.70∠103.32° cL = 0.39∠ 2 2 0.57 − 0.30 rL = 0.05 × 2.10 0.57 − 0.30 2 2 = 0.48 5.2.3 Constant Gain Circles 1. Unilateral Case (S12 = 0) • It is practical to plot the input and output gain circles for unilateral devices. • From the transducer power gain equation, we substitute S12 = 0 Gt = 1 − Γs 2 1 − S11Γs 2 89 S21 2 1 − ΓL 2 1 − S22 ΓL 2 Fig.5-5: Reference block diagram for linear amplifier design • We defined gs = gL = 1 − Γs 2 1 − S11Γs 1 − ΓL 2 2 1 − S22 ΓL 2 Where gs = gain contribution from input matching network gL = gain contribution from output matching network It is obvious that gs is maximum when Γs = S11* and gL is maximum when ΓL = S22*. g s , max = 1 2 1 − S11Γs g L , max = 1 2 1 − S22 ΓL Now define the normalized gain value gns and gnL given as g ns = gs g nL = g s , max gL g L , max Thus, we can rewrite the transducer power gain as Gt = gs g s ,max gL 2 g s ,max S 21 g L ,max g L ,max 90 = g ns Gtu ,max g nL Where Gtu,max = gs,max|S21|2gL,max represents the maximum unilateral transducer power gain. Thus, our design goal can be related to Gtu,max and the gain back off, gs and gL. By solving gs and gL for Γs and ΓL, respectively, we obtain circles in the Γs-plane and ΓL-plane that satisfy fixed gs and gL. These circles are given by: Input Gain Circle • The center of the constant gain circle is ds = g ns S11* 1 − S11 1 − g ns 2 Note that the centres of the input constant gain circles are located along the S11* vector. • The radius of the constant gain circle is rs = ( 1 − g ns 1 − S11 2 ) 1 − S11 1 − g ns 2 Output Gain Circle • The center of the constant gain circle is dL = * g nL S 22 1 − S 22 1 − g nL 2 Note that the center of the input constant gain circle is along the S22* vector. • The radius of the constant gain circle is rL = ( 1 − g nL 1 − S22 2 ) 1 − S22 1 − g nL 2 91 Example 5-2: A certain RF transistor has the following S parameters measured at 500 MHz with a 50 Ω reference: S11 = 0.8∠ -80° S22 = 0.8∠ -80° S12 ≈ 0 S21 ≈ 2 Determine the maximum unilateral transducer power gain and plot the input constant gain circle for 3, 2, 1, 0, -1. Solution: The maximum unilateral transducer power gain is obtained when input and output are conjugately matched (Γs = S11* and ΓL = S22*) |S21|2 = 4 = 6 dB gs,max = 1 / (1 - |S11|2) = 1 / (1 – 0.64) = 2.78 = 4.4 dB gL,max = 1 / (1 - |S22|2) = 1 / (1 – 0.64) = 2.78 = 4.4 dB Then the maximum unilateral transducer power gain is Gtu,max = 4 x 2.78 x 2.78 = 30.91 = 14.8 dB Input constant gain circle For 3 dB gain (a ratio of 2) g ns = rs = ds = gs g s , max = 2 = 0.72 2.78 ( 1 − g ns 1 − S11 2 1 − S11 1 − g ns 2 g ns S11 1− S * 1− g 2 11 )= ns 92 = 1 − 0.72 1 − 0.8 2 1 − 0.8 1 − 0.72 2 = 0.23 0.72 × 0.8 = 0.70∠80 0 2 1 − 0.8 1 − 0.72 Repeat for different power gain levels and the results are tabulate as follow: Gs dB Gs ratio gns ds rs -1 0.79 0.29 0.43 0.55 0 1 0.36 0.49 0.49 1 1.26 0.45 0.55 0.41 2 1.59 0.57 0.63 0.33 3 2 0.72 0.70 0.23 2. Unilateral Figure of Merit • When |S12| is not zero but because it is very small and is assumed to be zero. In such case, the error introduced by the approximation may be determined using the unilateral Figure of Merit. • The magnitude ratio of the transducer power gain to the unilateral transducer power gain is 93 Gt 1 = Gtu 1 − X 2 Where X = S12 S 21Γs ΓL 1 − S11Γs 1 − S 22 ΓL • The boundary condition for the ratio is 1 1 + X 2 < Gt 1 < Gtu 1 − X 2 • Gtu,max occurred when Γs = S11* and ΓL = S22*. Thus, the maximum error introduced when using Gtu,max is bounded by Gt 1 1 < < 2 Gtu ,max 1 − M 2 1 + M Where M = S12 S 21 S11 S 22 1 − S11 2 1 − S 22 2 • M is known as the Unilateral Figure of Merit. • If |S12 | ≠ 0 and it is decided to design the amplifier using the unilateral method (to have control of selective mismatch at the input and output), it is advisable to compute the maximum error based on the Unilateral Figure of Merit to determine if the method could be applied. • If not, the designer should either 1. 2. proceed with design based on bilateral method, or choose another device where |S12| = 0 or it is very small. 94 5.2.4 Constant Operating Power Gain Circles (Bilateral Case) • The bilateral case occurred when S12 can’t be neglected, S12≠0 • From the transducer power gain equation Gt = 1 − Γs 2 1 − Γin Γs 2 S21 2 1 − ΓL 2 1 − S22 ΓL 2 And Γin = S11 + S12 S 21ΓL S11 − ∆ΓL = 1 − S 22 ΓL 1 − S 22 ΓL • We notice that the input coefficient of reflection (Γin) is dependent on (ΓL). It is difficult to plot separate input & output gain circles as the input gain circle now depends on the load (ZL or ΓL) and not the transistor alone. • This implies that Γs and ΓL are inter-dependent on each other for a given gain objective. To have a close form solution in the face of these inter-dependencies, we take Γs = Γin* to obtain the operating gain equation Γs = Γin * S S Γ = S11 + 12 21 L 1 − S 22 ΓL * • There are two cases to be studied: Unconditionally Stable and Conditionally Stable. 1. Unconditionally Stable • Operating power gain is given as Gp = 1 − ΓL 2 1 S21 2 2 1 − Γin 1 − S22 ΓL 2 95 ΓL may be solved for a given operating gain required. Plotting ΓL on the Smith Chart for a given gain results in various circles. The smaller the gain is, the larger the circle will be. Any value of ΓL (and its associated, computed Γs) will result in an amplifier with that gain. • To design an amplifier with an operating gain of Gp, we need to compute a number of intermediate variables in order to determine the location and radius of the gain circle on the Smith Chart. gp = S 21 2 1 − ΓL = 2 2 S − ∆ΓL 1 − 11 1 − S 22 ΓL 1 − ΓL = = Gp 1 − S 22 ΓL 2 1 − S 22 ΓL − S11 − ∆ΓL 2 1 − ΓL 2 2 1 − S11 + ΓL 2 K= 2 S 22 − ∆ 2 2 1 + ∆ − S 11 − S 22 2 2 2 − 2 Re ΓL C L 2 2 S11S 22 |∆| = |S11S22 – S12S21| CL =S22 - ∆S11* • The radii of the operating gain circle 1 − 2 K S12 S 21 g p + S12 S 21 g p 2 rpL = 1 + g p S 22 − ∆ 96 2 2 2 • The center of the circle is d pL = g pCL * 1 + g p S 22 − ∆ 2 2 • The maximum value of gp is g p ,max = ) ( G p ,max 1 K − K2 −1 = 2 S12 S 21 S 21 • Thus the maximum operating power gain is given as G p ,max ( S 21 = K − K2 −1 S12 ) • This maximum operating power gain is obtained when a conjugate match is realized at the input side (Γs = Γin*). This implies that the input matching network must transform the source impedance Zs into Γs (after matching network) such that Γs = Γin* Example 5-3: A certain GaAs MESFET has the following S parameters measured at 1.8 GHz with a 50 Ω resistance: S11 = 0.26∠ -55° S12 = 0.08∠ 80° S21 = 2.14∠ 65° S22 = 0.82∠ -30° Plot the power gain circles. Solution: 97 1. Compute the delta factor ∆ and the stability factor K: ∆ = 0.26∠ -55°x 0.82∠ -30°- 0.08∠ 80°x 2.14∠ 65°= 0.36∠ -62.7° |∆| = 0.36 < 1 |∆|2 = 0.13 1 + 0.36 − 0.26 − 0.82 = 1.15 > 1 K= 2 × 0.08 × 2.14 2 2 2 This transistor is unconditionally stable 2. The maximum operating power gain is ( ) G p ,max = 2.14 1.15 − 1.152 − 1 = 15.51 = 11.91 dB 0.08 3. Compute gp,max gp,max = 15.51 / 2.142 = 3.39 4. The circle center is computed as CL* = S22* - ∆*S11 = 0.82∠ 30° – 0.36∠ 62.7° x 0.26∠ -55° = 0.73∠ 32.83° d pL = 3.39 × 0.73∠32.83° = 0.87∠32.83° 2 1 + 3.39 0.82 − 0.13 5. The radius of the circle is computed as 1 − 2 × 1.15 0.08 × 2.14 × 3.39 + 0.08 × 2.14 3.39 2 rpL = 1 + 3.39 0.82 − 0.36 2 2 2 = 0.00 6. Compute the distances and radii of the circles for power gain of 10, 8 and 6 dB. 7. The computed values are tabulated as follow 98 Gp dB 11.91 10 8 6 Ratio 15.52 10 6.31 3.98 gn 3.39 2.18 1.38 0.87 dpL 0.87 0.73 0.58 0.43 rpL 0.00 0.25 0.41 0.56 8. Plot the power gain circles on the Smith Chart as shown in Figure. 9. The normalized load impedance for 11.91 dB power gain is read from the plot at ΓL as zL = 0.80 + j3.20 Then the load impedance is ZL = 40 + j160 Ω 10.For each value of the distance dp use for the power desired, maximum output power occurs with a conjugate match at the input. ( ) * Γs = Γin = 0.26∠ − 55° + 0.08∠80° × 2.14∠65° × 0.87∠32.83° = 0.31∠ − 76.87° 1 − 0.82∠ − 30° × 0.87∠32.83° Then read normalized source impedance zs at Γs as zs = 0.95 – j0.70. Thus the actual source impedance is Zs = 47.5 – j35 Ω 99 2. Potentially Unstable • In practice, you should choose a transistor that is unconditionally stable. However if you have no choice, the design procedure for a conditionally stable transistor is as follow: - Compute the maximum stable power gain at K =1, make sure it is higher than the desired amplifier gain. - Draw the constant operating power gain circle for a given power gain Gp in dB. - Draw the output stability circle. - Choose ΓL in the stable region. - Compute Γin and determine if a conjugate match at the input is possible. - Draw the input stability circle and determine if Γs = Γin* is within the input stable region. - If Γs = Γin* is not in the stable region (or in the stable region very close to the stability circle), a new value ΓL must be selected arbitrarily or a value of Gp is chosen again. ΓL and Γs should not be too close to their respective stability circles as oscillation may occur when input and output circles are not matched. Example 5-4: A certain GaAs MESFET has the following S parameters measured at 9 GHz with a 50 Ω resistance: S11 = 0.45∠ -60° S12 = 0.09∠ 70° S21 = 2.50∠ 74° S22 = 0.80∠ -50° Design an amplifier for an operating power gain of 10 dB. Solution: 1. Compute the delta factor ∆ and the stability factor K: 100 ∆ = 0.45∠ -60°x 0.848∠ -50°- 0.09∠ 70°x 2.50∠ 74°= 0.20∠ 74° |∆| = 0.20 < 1 1 + 0.02 − 0.45 − 0.80 = 0.44 < 1 K= 2 × 0.09 × 2.50 2 2 2 This transistor is potentially unstable because K < 1. 2. Compute the maximum stable power gain at K =1 Gmax = |S21| / |S12| = 2.5 / 0.09 = 27.78 = 14.44 dB Thus, a 10 dB power gain is possible. 3. Compute dp and rp for the 10 dB operating power gain circle. gp = Gp S 21 2 = 10 2 = 1.60 2.5 CL* = S22* - ∆*S11 = 0.80∠ 50° – 0.20∠ 70.7° x 0.45∠ -60° = 0.73∠ 54.55° d pL = 1.60 × 0.732∠54.55°2 = 0.60∠54.55° 1 + 1.6 0.8 − 0.20 1 − 2 × 0.44 × 0.99 × 2.5 × 1.6 + 0.09 × 2.5 1.6 2 rpL = 1 + 1.6 0.8 − 0.20 2 2 4. Compute cL and rL for the output stability circle. 54.55° = 1.22∠54.55° cL = 0.73∠ 2 2 0.80 − 0.20 rL = 0.09 × 2.50 0.80 − 0.20 2 2 = 0.38 101 2 = 0.46 5. The stable region is the region outside the output stability circle. The load reflection coefficient ΓL is chosen on the 10 dB power gain circle at the location A. Then ΓL = 0.38∠ 104° zL = 0.70 + j0.50 Ω 6. Compute Γs for a possible conjugate match ( ZL = 35 + j25 Ω ) Γs = Γin = 0.45∠ − 60° + 0.09∠70° × 2.50∠74° × 0.38∠104° = 0.535∠ − 66.2° 1 − 0.80∠ − 50° × 0.38∠104° * 7. Compute ds and rs for the input stability circle. Cs* = 0.45∠ 60° - 0.20∠ 70.7°x 0.80∠ -50°= 0.35∠ 76.37° cs = 0.352∠76.37°2 = 2.19∠76.37° 0.45 − 0.20 rs = 0.09 × 2.50 0.45 − 0.20 2 2 = 1.41 8. From the figure, Γs is stable source reflection coefficient because it is located in the stable region outside the stability circle. 102 5.2.5 Constant Noise Figure Circles • Noise Figure, F= SNRin SNRout Represent the amount of degradation to the SNR by the amplifier. • The noise figure of a two port RF amplifier is given by F = Fmin + [ rn r 2 2 2 y s − yo = Fmin + n (g s − g o ) + (bs − bo ) gs gs ] Where Fmin = minimum noise figure, which is a function of the device operating frequency and current. rn = Rn / Z0 is the normalized noise impedance of the two ports ys = gs + jbs is the normalized source admittance yo = go + jbo is the normalized optimum source admittance which results in the minimum noise figure. • Substitute ys = 1 − Γs 1 + Γs yo = 1 − Γo 1 + Γo • The noise figure equation become F = Fmin + 4rn Γs − Γo 1 − Γs 2 2 1 + Γo 2 103 • To determine the noise figure circles for a given noise figure Fi, we define an intermediate NF parameter Ni = Fi − Fmin 1 + Γo 4rn 2 Where Fi = noise figure required (ration value) Fmin = device minimum noise figure (ration value) rn = Rn / Zo ( from data sheet or measured) Γ0 = optimum source reflection coefficient which results in the minimum noise figure • The center of the noise figure circle is C Fi = Γo 1 + Ni • The radii of the noise figure circle is rFi = 1 1 + Ni ( Ni + Ni 1 − Γ 2 2 ) • Generally, Rn may not be available in the data sheet at the desired condition. In this case, we have to determine the source resistance / impedance and the bias point that produce the minimum noise figure. Once determined, the actual source resistance or impedance is forced (through impedance matching network) to present the “optimum” value to the device. • The implication is that you may have to compromise gain for noise performance. Example 5-5: A certain GaAs MESFET has the following noise figure parameters measured at Vds = 5V, Ids = 20mA with a 50 Ω resistance for a frequency of 2 GHz. Fmin = 2 dB , Γ0 = 0.485∠ 155°, Rn = 4 Ω Plot the noise figure circles for given values of Fi at 2.5, 3.0, 3.5 and 5 dB. 104 Solution: For NF of 2.5 dB Ni = Fi − Fmin 2 2 1 + Γo = 1.78 − 1.59 1 + 0.485∠155° = 0.21 4rn 4× 4 50 C F i = 0.485∠155° = 0.40∠155° 1 + 0.21 rF i = 1 1 + 0.21 (0.21)2 + 0.21(1 − 0.485 2 ) = 0.37 The values of Ni, CFi and rFi for different Fi are tabulated as follow: Fi dB 2.5 3 3.5 4 5 ratio 1.78 2 2.24 2.5 3.16 Ni 0.21 0.45 0.73 1.03 1.755 105 CFi 0.40∠ 155° 0.33∠ 155° 0.28∠ 155° 0.24∠ 155° 0.18∠ 155° rFi 0.37 0.51 0.603 0.66 0.76 5.3 DC Biasing Circuit Design • The RF amplifiers are usually classified into small signal mode and large signal mode. Fig.5-6: Small signal operation of RF amplifier • In small signal mode - Relatively higher load impedance (small gradient). - Signal variation is small relative to Q point value. - Have minimal non-linearity problem Fig.5-7: large signal operation of RF amplifier 106 • In large signal mode - Relatively low impedance (steeper gradient for AC load line). - Signal strength variation is comparable in magnitude to Q point value. - Have more / greater non-linearity giving rise to poorer 1 dB compression and 3rd order intercept. • The DC biasing operating point of a RF amplifier depends on its specific application. • The safe operating point for a Silicon Transistor and GaAs MESFET can be determined by: Silicon Transistor Max collector –emitter voltage Max collector current Secondary breakdown Max power dissipation GaAs MESFET Max drain-source voltage Max drain current Max input signal power Max power dissipation • The above maximum settings need to be checked in small signal design. • It is usually an ISSUE when it comes to the selection of devices for large signal, high output power design. • The main objectives of DC biasing are: - Establish quiescent point to set S parameters and hence the RF amplifier performance - Provide Q point stabilization over the temperature and device parameter to variations. - Transparent to RF operation. 107 5.3.1 DC Biasing Circuits for RF Silicon Transistor • RF transistor circuit for a high power gain or low noise figure often requires that the emitter lead be DC ground as close to the package as possible so that the emitter series feedback is kept at minimum. • If the emitter bypass capacitor has poor or low self resonant frequency, it may become inductive and leads to excessive feedback or oscillation. Passive DC biasing circuit: • Fig.5-8 shows three configurations of DC biasing circuits for RF silicon transistors in the order of increasing stability. Fig.5-8: Passive DC biasing Circuits for RF amplifier 108 • The two grounded emitter DC biasing circuits as shown in (a) and (b) are suitable for high RF frequency operation. • The DC biasing circuit with bypass emitter resistor provides excellent stability and is suitable to be used at the lower RF frequency. • Radio frequency chokes (RFCs) may not be always needed. It depends on the AC circuit layout as well as the value of the biasing resistor (especially in the base circuit where biasing resistance value is usually quite high). Example 5-6: A certain RF transistor has the following parameters: VCC = 30 V, VBB = 3 V, VBE = 1 V, IBB = 1.5 mA, ICBO = 0, hFE = 50 Quiescent point: VCE = 10V, IC = 15 mA To hold the quiescent point constant with temperature changing, it is necessary to design passive DC biasing circuit as shown in Fig.5-8. Solution: 1. Design a passive DC biasing circuit with voltage feedback. IB = −3 IC = 15 × 10 = 0.3 mA hFE 50 RB = VCE − VBE = 10 − 1−3 = 30 KΩ IB 0.3 × 10 RC = VCC − VCE 30 − 10 = = 1.3 KΩ IC + I B 15 × 10 −3 + 0.3 × 10 −3 2. Design a passive DC biasing circuit with feedback and constant base current RB = VBB − VBE = 3 − 1 −3 = 6.67 KΩ IB 0.3 × 10 109 RB1 = VCE − VBB 10 − 3 = = 3.89 KΩ I BB + I B 1.5 × 10 −3 + 0.3 × 10 −3 RB 2 = RC = VBB 3 = = 2 KΩ I BB 1.5 × 10 −3 VCC − VCE 30 − 10 = = 1.19 KΩ −3 I C + I BB + I B 15 × 10 + 1.5 × 10 −3 + 0.3 × 10 −3 3. Design a passive DC biasing circuit with a bypass emitter resister RE = VBB − VBE 3 −1 = = 130 Ω −3 −3 IC + I B 1.5 × 10 + 0.3 × 10 Active DC biasing circuits • Provides very stable Q point even if temperature changes or design parameters vary. Fig.5-9: Active DC basing circuit for RF Silicon transistor • The quiescent point can be adjusted by RB2 and RE where RB2 is adjusted to provide for proper voltage VCE and RE is adjusted to supply the collector current IC. 110 5.3.2 DC biasing circuit for RF GaAs MESFET Passive DC basing ciruict • For GaAs MESFET, the range of gate voltage is given as Vp < Vgs <0 Where Vp is the pinch off voltage. • There are 3 types commonly used passive biasing circuit for MESFET. a) Bipolar power supply Fig.5-10: Bipolar power supply circuit - Direct connection from the source to ground terminal gives better gain and noise performance. - The proper turn on method is first to apply a negative bias to the gate and then apply the positive drain voltage. This is to prevent burnout of a GaAs MESFET in case there are residue charges on the gate and the drain is biased positive before the gate. b) Single power supply Fig.5-11: Single power supply circuit 111 - For single positive power supply, Vs must be apply applied first before Vds is applied so that Vgs is negatively biased before the drain voltage Vds is applied. - For single negative power supply, -Vgs must be turned on before the source voltage –Vds is on. - This type of biasing circuits require very good RF bypass capacitors at the source since any small series source impedance could degrade the noise performance. c) Unipolar power supply Fig.5-12: Unipolar power supply circuit - Self bias with Vgs entirely depends on Id and Rs. - The turn on and turn off transient protection is provided by Rs. - However the source resistor degrades the amplifier efficiency and noise performance. - Good RF bypass capacitors are also required. Active DC biasing circuit • Can provide very stable Q pointy against temperature effects and device parameter variation. Fig.5-13: Active DC biasing circuit 112 • The quiescent point is controlled by RE and RB2 where RE is adjusted to provide for proper Ids,q and RB2 is adjusted to provide for proper Vds,q • VE(BJT) or Vds,q = VB + VBE (constant) ⇒ IRE = constant • IRE = ID, so that ID is held constant regardless of thermal effect in MESFET. • ID is constant implies - Q point remains constant - S parameter is constant - Stable performance 5.3.3 Biasing Circuit Design • In general, the Class A amplifier can provide low noise, low power and high power gain. • Class B or Class AB amplifier can generate higher power and high efficiency. Fig.5-14: DC quiescent points for GaAs MESFET amplifier 113 5.4 Design Methodology 5.4.1 Initial Design Sequence The following steps serve as a quick guide for the design of the RF amplifiers using either unilateral or bilateral devices: 1. List the specifications of the RF amplifier to be designed, such as frequency, power gain, output power, characteristic impedance, noise figure etc. 2. Choose a device that will meet the specifications, paying attention to intended applications, power supply requirements, potential gain and noise improvements. 3. Determine the DC Q point and design the DC biasing circuit after RF design completed. In general, for small signal linear amplifier, Q point is usually taken at Class A mid-point bias. 4. Measure the S parameters of the chosen device at the appropriate Q point and operating frequency. 5. Check stability performance and plot respective stability circle to determine the potentially unstable region in the Smith Chart for Zs and ZL. 6. Compute the unilateral figure or merit and error range for unilateral assumption (not necessary if designed approach is already decided). 7. Decide on design approach, either Bilateral or Unilateral. - Unilateral Approach Best method to use if S12 = 0. If not, check “Unilateral Figure of Merit” to determine maximum error range before deciding if you still want to use this approach. - Bilateral Approach This is the most generic approach and potential limitations or difficulties with this method is minimized using EDA tools. Note that this approach is also applicable to unilateral devices. 114 5.4.2 Design for Specific Unilateral Power Gain Greq • Below is the steps to design an amplifier with specific gain using unilateral devices: - Carry out the initial design sequence. - Compute the forward transducer power gain Gf = 10 log |S21|2 (dB) - Assign the gain requirements to the input and output networks: Greq = Gs + Gf +GL (dB) - Plot the input and output constant gain circles. - Design the input matching network to achieve the gain assigned to the input matching network by stopping at the appropriate input constant gain circle. - Design the output matching network to achieve the gain assigned to the output matching network by stopping at the appropriate output constant gain circle. Example 5-7: A RF transistor has the following S parameters measured with a 50 Ω resistance at VCE = 4 V and IC = 0.5 Ic,max for a frequency of 3 GHz. S11 = 0.707∠ -155° S12 = 0° S21 = 4∠ 180° S22 = 0.51∠ -20° Design the input and output matching networks of the amplifier for a power gain of 15 dB at the frequency of 3GHz. Solution: 115 1. The forward transducer power gain, Gf = 10 log |4|2 = 12 dB For a total of 15 dB gain, 2 dB may come from the input network and 1 dB from the output network. 2. Plot the input and output constant gain circles. Gs dB gs gm ds rs 2 1.59 0.8 0.63 0.25 1 1.26 0.63 0.55 0.38 0 1 0.5 0.47 0.47 Values for input constant gain circles GL dB gL gnL dL rL 1 1.26 0.93 0.48 0.2 Values for output constant gain circles 116 0 1 0.74 0.41 0.41 3. Determine the output matching network from Smith Chart The first element of the L matching network is a series capacitor jX = -j1.45 x 50 = -j72.50 Ω CL = 1 / (ωX) = 1 / (2π x 3 x 109 x 72.5) = 0.73 pF The second element is a shunt inductor jB = -j0.43 / 50 = -j 8.6 x10-3 Ω LL = 1/ (ωB) = 1 / (2π x 3 x 109 x 8.6 x 10-3) = 6.17 nH 4. Determine the input matching network from the Smith chart The first element of the L matching network is a shunt capacitor jB = j2.18 /50 = j43.60 x 10-3 Ω Cs = B / ω = 43.6 x 10-3 / (2π x 3 x 109) = 2.31 pF The second element is a series inductor jX = j0.43 x 50 = j21.50 Ω Ls = X / ω = 21.50 / (2π x 3 x 109) = 1.14 nH 117 5.4.3 Design for maximum unilateral power gain • Generally use mid-point Class A circuit. • The input and output matching circuit must be conjugately match: Γs = S11* ΓL = S22* • Steps to design for maximum unilateral power gain: - Carry out the initial design sequence. - Compute maximum transducer power gain. Gtu ,max = 2 1 1 S 21 2 1 − S11 1 − S 22 2 = g s ,max g f g L ,max = Gs ,max + G f + G L ,max dB - Design the input and the output matching network for maximum power gain (impedance matching to S11* and S22*). Example 5-8: A GaAs MESFET has the following S parameter measured with a 50 Ω resistance at Vds = 4V and Ids = 0.5 Idss at 9 GHz. S11 = 0.55∠ -150° S12 = 0.04∠ 20° S21 = 2.82∠ 180° S22 = 0.45∠ -30° Design the input and output matching networks of the amplifier for maximum power gain at 9 GHz. Solution: 118 1. Calculate maximum transducer power gain (assumed S12 = 0) Gtu , max = = 2 1 1 S 21 2 1 − S11 1 − S 22 2 2 1 1 2 . 82 2 2 1 − 0.45 1 − 0.55 = 1.43 × 7.95 × 1.25 = 14.21 = 1.55dB + 9dB + 0.97dB = 11.92 dB 2. The delta factor is ∆ = 0.55∠ -150° x 0.45∠ -30° – 0.04∠ 20° x 2.82∠ 180° = 0.25∠ -180° – 0.11∠ 200° = 0.16∠ 165° | ∆ | = 2.28 > 1 The stability factor 2 1 + ∆ − S 11 − S 22 2 K= 2 2 S11S 22 1 + 0.16 − 0.55 − 0.45 = 2 × 0.02 × 2.82 2 2 2 = 2.28 > 1 The device is unconditionally stable. 3. Compute the unilateral figure of merit M= S12 S 21 S11 S 22 2 11 1− S 1− S 2 22 = 0.04 2.82 0.55 0.45 1 − 0.55 119 2 1 − 0.45 2 = 0.05 The error Gt 1 1 < < 2 Gtu ,max 1 − 0.05 2 1 + 0.05 0.91 < Gt Gtu ,max − 0.41dB < < 1.11 Gt Gtu ,max < +0.45dB The maximum error if from +0.45 to –0.41 dB which is small enough to justify the unilateral assumption. 4. Plot S11* and S22* on the Smith Chart. 5. Determine the output matching network from the Smith Chart. The first element of the L matching network is a series capacitor jX = -j1.2 x 50 = -j60 Ω CL = 1 / ωX = 1 / ( 2π x 9 x 109 x 60) = 0.29 nF The second element is a shunt inductor jB = -j0.73 / 50 = -j14.6 x 10-3 Ω LL = 1/ ωB = 1 / (2π x 9 x 109 x 14.60 x 10-3) = 1.21 nH 6. Determine the input matching network from the Smith Chart. The first element of the L matching network is a shunt capacitor jB = j1.66 /50 = j33.31 x 10-3 Ω Cs = B / ω = 33.32 x 10-3 / (2π x 9 x 109) = 0.59 nF The second element is a series inductor jX = j0.71 x 50 = j 35.50 Ω 120 Ls = X / ω = 35.50 / (2π x 9 x 109) = 0.63 nH 5.4.4 Design for unilateral LNA with specific NF and power gain • LNA with high power gain is critical to receiver design. 121 • In general, we need to trade gain for low noise performance. This implies that more stages may be introduced to have both low noise and specific gain. • Design sequence: - Carry out the initial design sequence. - Compute the forward transducer gain Gf = 10 log |S21|2 dB - Assign gain requirements (dB) to input and output matching network: Greq = Gs + Gf + GL (dB) - Plot the required constant noise figure circle. - Plot the input and output constant gain circles. - Design the output matching network by stopping at the output constant gain circles. - Design for input matching network for low noise by stopping along the input constant gain circle within the constant noise figure circle. Example 5-9: A RF transistor has the following S parameters and noise parameters measured with a 50 Ω resistance at VCE = 4V and IC = 30 mA at 3 GHz. S11 = 0.707∠ -155° S12 = 0 S21 = 5.00∠ 180° S22 = 0.51∠ -20° Fmin = 3 dB, Γ0 = 0.45∠ 180°, R0 = 4 Ω 122 Design the input and output matching networks of the amplifier for a power gain of 16 dB and low noise figure of 3.5 dB. Solution: 1. Calculate the max transducer power gain Gtu , max = = 2 1 1 S 21 2 2 1 − S11 1 − S 22 2 1 1 5 2 2 1 − 0.51 1 − 0.707 = 2 × 25 × 1.35 = 67.50 = 3dB + 14dB + 1.30dB = 18.30 dB to have a total power gain of 16 dB, we can have 1.22 dB from the input matching network and 0.78 dB from the output matching network. 2. Plot the 3.5 dB constant noise figure Fi = 3.5 dB = 2.24 Ni = Fi − Fmin 2 2 1 + Γo = 2.24 − 2 1 + 0.45∠180° = 0.23 4rn 4× 4 50 CF i = rF i = Γo = 0.45∠180° = 0.37∠180° 1+ Ni 1 + 0.23 1 = 1 1 + N i 1 + 0.23 (0.23)2 + 0.23(1 − 0.45 2 ) = 0.39 3. Plot the input 1.22 dB power gain circle Gs = 1.22 dB = 1.32 123 g ns = ds = rs = ( gs ) = 1.32 1 − 0.707 = 0.66 g s , max 2 g ns S11 = 1 − S11 1 − g ns 2 ( 1 − g ns 1 − S11 2 1 − S11 1 − g ns 2 0.66 × 0.707 = 0.56 2 1 − 0.707 1 − 0.66 )= 1 − 0.66 1 − 0.707 2 1 − 0.707 1 − 0.66 2 = 0.35 4. Plot the output 0.78 dB power gain circle GL = 0.78 dB = 1.20 g nL = dL = rL = ( gL ) = 1.20 1 − 0.51 = 0.89 g L, max 2 g nL S22 1 − S22 1 − g 2 nL ( 2 1 − g nL 1 − S22 1 − S22 1 − g 2 nL = 0.89 × 0.51 = 0.47 2 1 − 0.51 1 − 0.89 )= 1 − 0.89 1 − 0.51 2 2 1 − 0.51 1 − 0.89 = 0.25 5. Determine the output matching network from Smith Chart: The first element of the L matching network is a series capacitor jX = -j1.40 x 50 = -j70 Ω CL = 1 / ωX = 1 / (2π x 109 x 70) = 2.27 pF The second element is a shunt inductor jB = -j0.40 / 50 = -j 8 x 10-3 Ω LL = 1 / ωB = 1 / (2π x 109 x 8 x 10-3) = 19.89 nH 124 6. Determine the input matching network from the Smith Chart: The first element of the L matching network is a shunt capacitor jB = j0.75 /50 = j 15 x 10-3 Ω Cs = B / ω = 15 x 10-3 / (2π x 109) = 2.39 pF The second element is a series inductor jX = j0.44 x 50 = j22 Ω CL = X / ω = 22 / (2π x109) = 3.5 nH 125 5.4.5 Design for specific power gain with bilateral devices • This method of design using bilateral devices is also applicable to unilateral devices. • In this section we consider the case of arbitrary selection of ΓL with the input conjugately matched. • Design sequence: - Carry out the initial design sequence. - Compute the maximum operating power gain G p ,max = ( S 21 K − K2 −1 S12 ) - Plot the desired constant operating power gain circle. - Design the output matching network to achieve the gain required by starting at the actual load impedance position (Z’L) and stopping at the desired point on the constant operating power gain circle (for maximum gain, the radius = 0). Note: the value of ΓL selected 126 - The value of ΓL selected would produce the required operating power gain if the input of the transistor is conjugately matched to source. Therefore, compute Γs = Γin * S S Γ = S11 + 12 21 L 1 − S 22 ΓL * Design the input matching network to transform the actual source impedance Z’L to the required Γs as computed above. 5.4.6 Design for optimum NF (Bilateral Method) • This section consider the case of arbitrary selection of Γs with the output conjugately matched, i.e. ΓL =Γout*. Method may also be used for unilateral devices. • To be able to design a LNA with specific NF requires the following information of the devices: Fmin – minimum noise figure (depend on frequency and Iq) Rn – equivalent noise resistance referred to the input. Γ0 – optimum source reflection coefficient • Many data sheet does not provide Rn and even if provided, the value of Fmin and Rn may not be measured under the conditions that the intended application may have. • It is still possible to design an optimum NF LNA if only Γ0 is given, following the steps outline below. However, it would not be possible to predict its NF and must be verified after realization. • Design sequence: - Carry out initial design sequence. - Plot Γs = Γ0 on the Smith Chart, the optimum input reflection coefficient for lowest noise. - Design the input matching network to transform Z’s to Γ0. 127 - Compute the value of ΓL so that the load is conjugately matched to the output of the transistor. ΓL = Γout * S S Γ = S 22 + 12 21 o 1 − S 22 Γo * Design the output matching network to transform the actual load impedance Z’L to the required ΓL as computed above. - Compute the power gain of the optimized LNA GL = 1 − Γo 2 1 − S11Γo 2 S21 2 1 2 1 − Γout 5.5 RF Amplifier Performance Parameters Besides the usual power gain, power output, noise figure, band width and other specifications, the 1 dB compression point and two tone 3rd order intercept point are also important parameters in measuring the performance of RF amplifier. 5.5.1 1 dB compression Point • The gain of the RF amplifier G = Pout – Pin (dB) • As Pin is increased, Pout increases up to the saturation point of the RF amplifier. • Towards the saturation point, the Pout doesn’t follow the rate of increase in Pin. This results in an effective decrease in gain of amplifier. • The decrease in effective gain is termed gain compression. • The output power at which the gain is compressed by 1 dB is termed the 1 dB compression point. This usually stated in dBm. 128 • Gain compression is a measurement of the dynamic range of the RF amplifier and 1 dB compression point is usually used a standard of measurement. • Dynamic range is the power range over which an RF amplifier provides useful linear operation, with the lower limit dependent on the noise figure and the upper limit a function of the 1 dB compression point. • Obviously, the higher the 1 dB compression point, the better the dynamic range. 5.5.2 Two Tone 3rd order intercept point • When two or more sinusoidal frequencies are applied to an RF amplifier that is not perfectly linear, the output contains additional frequencies components. This addition signals at the output are called ‘Intermodulation Products” or IMD. • If f1 and f2 are the frequencies of the two signals arriving at the input of the RF amplifier, the amplifier generates intermodulation products at its output due to inherent nonlinearity, in the form of : [±mf1 ± nf2] where m, n are positive integers which can assume any value from 0 to infinity. • The example, if 100 and 101MHz are the frequencies of the applied signals, then 99 and 102 MHz are the two tone 3rd order products. • The two tone 3rd order products are a major concern because of their proximity to the original / desired frequencies (f1 & f2) and they can not be filter effectively. Hence they are of great importance in system design. • In the linear region, 3rd order products decrease / increase by 3 dB for every 1 dB decrease / increase of input power, and the output signal (desired signal) power decrease / increase by 1 dB for every 1 dB decrease / increase of input power. 129 • By extending the linear portions of the response, they intercept at a point. This interception point is called the 3rd order intercept or IP3, or TOI. The IP3 is a measurement of the linearity of the RF amplifier as should be as high as possible. • It is also possible to predict the IP3 without plotting the lines / curves as follows: IP3 = P0 + (P0 – P3) / 2 dBm Where P0 = Pout of individual test frequencies P3 = Pout of 3rd order IMD products. Fig.5-15: RF amplifier 3rd order intercept point 130