Sentaurus Topography

advertisement

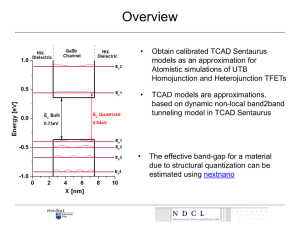

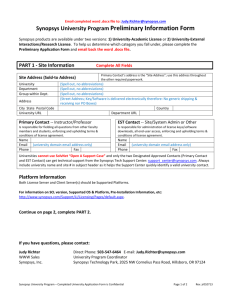

TCAD Sentaurus Общий обзор Радченко Дмитрий Alternative Solutions Alt-S Технический директор Predictable Success CONFIDENTIAL INFORMATION The Following Material Is Being Disclosed To You Pursuant To A Non-disclosure Agreement Between You Or Your Employer And Synopsys. Some Information Disclosed In This Presentation Is Pending Patent Application. Information Disclosed In This Presentation Shall Be Used Only As Permitted Under Such An Agreement. LEGAL NOTICE Information Contained In This Presentation Reflects Synopsys Plans As Of The Date Of This Presentation. Such Plans Are Subject To Completion And Are Subject To Change. Products Shall Be Offered And Purchased Only Pursuant To An Authorized quote And Purchase Order. © 2008 Synopsys, Inc. (2) Predictable Success Predictable Success © 2008 Synopsys, Inc. (3) Predictable Success Recent TCAD Milestones Sentaurus Lithography Launch PA-DFM Launch 02/08 10/06 SIGMA-C Integration 8/06 Sentaurus Launch 10/05 New Generation Standard for TCAD Simultaion Robust numerics & software implementimplementations Advanced, calibrated physical models TFM Introduction SelfSelf-consistent 2D & 3D modeling capabilities Accurate & predictive results Synopsys ISE + Many New Features Sentaurus 5/05 © 2005 Synopsys, Inc. (13) CONFIDENTIAL ISE Integration 11/04 © 2008 Synopsys, Inc. (4) Predictable Success Extending TCAD into Manufacturing & Design Analyze • Process variability • Design for Manufacturing Technology LifeProcess-Aware Cycle CoreProcess TCAD Process Module Device Research Development Explore Explore • New processes • Virtual devices Integration DFM New Product Introduction Optimize Optimize • Performance • Manufacturability Production Ramp Volume Manufacturing TCAD for Control Manufacturing Control • Yield analysis • Statistical process control • Advanced process control • Manufacturing for Design (MFD) © 2008 Synopsys, Inc. (5) Predictable Success Synopsys TCAD Product Portfolio Sentaurus Workbench Lithography Sentaurus Litho. EUV (8/08) Sentaurus Lithography Sentaurus Litho. E-Beam (12/08) Raphael Example Library Sentaurus Topography Sentaurus Structure Editor Sentaurus Process Sentaurus Device Technology Development Raphael NXT Interconnect Fammos Calibration PCM Studio Manufacturing Seismos Paramos Process-Aware Design For Manufacturing © 2008 Synopsys, Inc. (6) Predictable Success Core TCAD © 2008 Synopsys, Inc. (7) Predictable Success Sentaurus Process Sentaurus Process Mechanical Stress Multidimensional 2D/3D General Purpose Process Simulator Multidimensional 1D/2D/3D Advanced Models for: Implantation Diffusion Laser/Flash Annealing Oxidation Deposition and Etching Adaptive Meshing User-Defined Model Interface Flash/Laser Annealing Kinetic Monte Carlo © 2008 Synopsys, Inc. (8) Predictable Success Sentaurus Device Quantum Effects Device Monte Carlo Multidimensional 2D/3D Optoelectronics Sentaurus Device Heterostructure Capabilities General Purpose Device Simulator Silicon and Compound Semiconductors Advanced Transport Models State-of-the-Art Linear Solvers Efficient, full 3D Meshing Full-Wave Electromagnetic Solver User-Defined Model Interface Mixed-Mode Simulation © 2008 Synopsys, Inc. (9) Predictable Success Sentaurus Topography Tench Filling with Void Formation RIE Sentaurus Topography CMP Robust Level-Set Numerical Models Deposition Models LPCVD, PECVD, HDP-CVD, APCVD Spin-on-Glass Reflow Etching Models Wet etching High-density plasma Reactive ion etching Ion milling Chemical Mechanical Polishing Ion Milling External ion angular/energy distributions Interface to Sentaurus Process Topography simulation of NAND flash cell © 2008 Synopsys, Inc. (10) Predictable Success Sentaurus Structure Editor Easy to use GUI Scripting Language Advanced Geometric Modeling Process Emulation Capability Analytic Doping Definitions Direct Interface to Meshing Engines Sentaurus Structure Editor Process Emulation Mode Advanced Geometric Operations: Swadowing, etc Sweeping of 2D Structures Complex 3D Device Structures © 2008 Synopsys, Inc. (11) Predictable Success Sentaurus Workbench Sentaurus Workbench TCAD framework environment Project management Design-of-Experiments Job Farming Advanced Visualization Advanced Visualization X-Y Data Plotting TCAD Project Management © 2008 Synopsys, Inc. (12) Predictable Success Sentaurus Lithography SENTAURUS LITHOGRAPHY Rigorous EM Simulation of Lithography simulator for process development Simulation of Topography Wafer Topography Accounts for optical aberrations on Wafer 3D topographic mask simulation Rigorous calculations of electromagnetic field on wafer Full range of resist systems, including chemically amplified resists Models exposure, reaction, amplification and diffusion during post-exposure bak Rigorous models for image formation and resist development Cell size imaging simulations and hot spot detection at resist level Efficient algorithms enable large cell simulation Imaging contours with hot spot detection Rigorous Simulation of 3D Masks © 2008 Synopsys, Inc. (13) Predictable Success Raphael Process Effects Flexible Structure Generation with Sentaurus Structure Editor Capacitance Extraction Raphael Gold standard interconnect field solver Capacitance Resistance Inductance Automatic generation of Parasitic Database Calibration of LPE rule decks Sentaurus Structure Editor interface Advanced Visualization L and R Extraction © 2008 Synopsys, Inc. (14) Predictable Success Raphael NXT 4500 4000 Time (min) 3500 3000 2500 2000 1500 1000 500 0 1 Lithography Based Extraction 2 4 6 8 Processors (#) Distributed Processing Periodic Boundary Conditions Layout Raphael NXT StarXtract Star-RCXT RANXT DB Star-RCXT DB Critical Nets Parasitic Netlist RA NXT Chip-level critical net capacitance extractor xTractor Seamless integration with Star-RCXT Highly accurate full 3D capacitance extraction Efficient Floating Random Walk Algorithm High capacity: handles layouts with millions of polygons Distributed processing with excellent scaling Comparison Report Final Parasitic Netlist © 2008 Synopsys, Inc. (15) Predictable Success TCAD for Manufacturing © 2008 Synopsys, Inc. (16) Predictable Success Calibration Wafer Processing Initial Lots Integration Optimization Manufacturability Next Generation Technology Initial Scaling Process/Device Modeling Performance Optimization TCAD Process compact model Baseline Technology Ion5[ A/um] 800 600 400 200 0 0.01 0.1 1 Lact[um] 10 Calibration Vth5[V] 0.34 0.3 0.26 0.22 0.18 0.01 0.1 Lact[um] 1 Electrical Data 10 Saves technology development time Reduces number of development wafers Optimizes technology performance Improves manufacturability and yield SIMS Profiles © 2008 Synopsys, Inc. (17) Predictable Success Sentaurus TFM Parallel Coordinate Plots Process Parameters ri= f(fi) Correlation Studies Device Characteristics Sentaurus TFM Process Compact Models Process window optimization Manufacturing control Process variation to device performance correlation Process Compact Models derived from TCAD simulations © 2008 Synopsys, Inc. (18) Predictable Success TCAD-Driven Process Control Slow Parts High Leakage Parts Power Gate oxide Gate CD Controlled Uncontrolled Good Parts Slow Parts slow Halo implant Frequency Good Parts Controlled Number of Parts Frequency Uncontrolled S/D XT implant good Power leaking RTA temp High Leakage Parts Ioff Ion Spec limit Nominal Spec limit Measure Control © 2008 Synopsys, Inc. (19) Predictable Success Process-Aware DFM © 2008 Synopsys, Inc. (20) Predictable Success Paramos Lg Manufacturing Calibration Nchannel Tox TCAD I-V, C-V database Process Parameters Some Variability Sources in CMOS SPICE Extraction Process-Aware Compact SPICE Model SPICE Simulation Paramos Model Extraction Flow using Paramos Delay Variation 30% Gate oxidation temperature (Pox) 20% n-Halo implant (Phn) 10% L (Plg) 0% -10% analysis of the impact of global variations at the circuit level Based on rigorous TCAD simulations Provides bi-directional link between process information and circuit behavior 100% 50% 0% -50% Extracts process-aware SPICE parameters for detailed -100% -20% Normalized process variation Correlating Delay Variation to Process Paramos © 2008 Synopsys, Inc. (21) Predictable Success TCAD for Manufacturing Seismos LX and Seismos CX Gate Spacer Layout Cap layer STI Schematic Runset SiGe S/D Drawn GDSII Z Hercules LVS X Y Star-RCXT PrimeYield LCC Netlist (RC, xy) Contour GDSII Seismos LX + CX Annotated Spice Netlist Baseline BSIM HSPICE / HSIM / Nanosim Simulates and analyses changes to transistor characteristics due to proximity variations arising from layout-induced stress, well proximity and Lithography effects Seismos Annotates compact models to reflect impact on Vt and mobility Integrates into existing design flows © 2008 Synopsys, Inc. (22) Predictable Success Fammos Visualization of Stress Components Stresses in Metal 2 and Metal 3 Cu Lines Simulates mechanical stress in BEOL process flows Accounts for all major stress sources, including external stresses Design specifically for semiconductor applications Models key problems affecting process design and reliability of Cu/low k interconnect structures Fammos Stress Gradient at Bottom of Via © 2008 Synopsys, Inc. (23) Predictable Success TCAD Applications CMOS •Deep submicron transistors •Sophisticated models •Atomistic modeling Opto •LEDs, LASERs •Image sensors •Photodetectors Memory Synopsys TCAD Products RF •Flash •DRAM Emitter •High-speed devices Al0.3Ga0.7As Base •Compound semiconductors Power GaAs Collector •Complex structures & processes •Mixed mode simulation © 2008 Synopsys, Inc. (24) Predictable Success Synopsys TCAD Used by 19 out of 20 top semiconductor companies worldwide Synopsys TCAD Today Technical and market leadership across all technologies: DSM, Power, Memory, Analog and Optoelectronics Strong R&D program with research & academia Dedicated support organization focusing on customer success Complementary Consulting and Engineering Service Offerings © 2008 Synopsys, Inc. (25) Predictable Success Predictable Success © 2008 Synopsys, Inc. (26) Predictable Success