IPC-SA156A-HI

SATA Host

AHCI

Core

HYDRA SATA Bridge

with

NCQ

Overview

IntelliProp’s IPC-SA156A-HI is an industry standard Serial-ATA

(SATA) host interface core that enables host application

companies to use high throughput SATA storage devices. The

protocol interface is compliant to the SATA 3.0 specification as

defined by the Serial ATA International Organization (SATA-IO).

The IPC-SA156A-HI is fully verified in pseudo random simulation

IPC-SA156A-HI

SATA Host AHCI Core

Applications

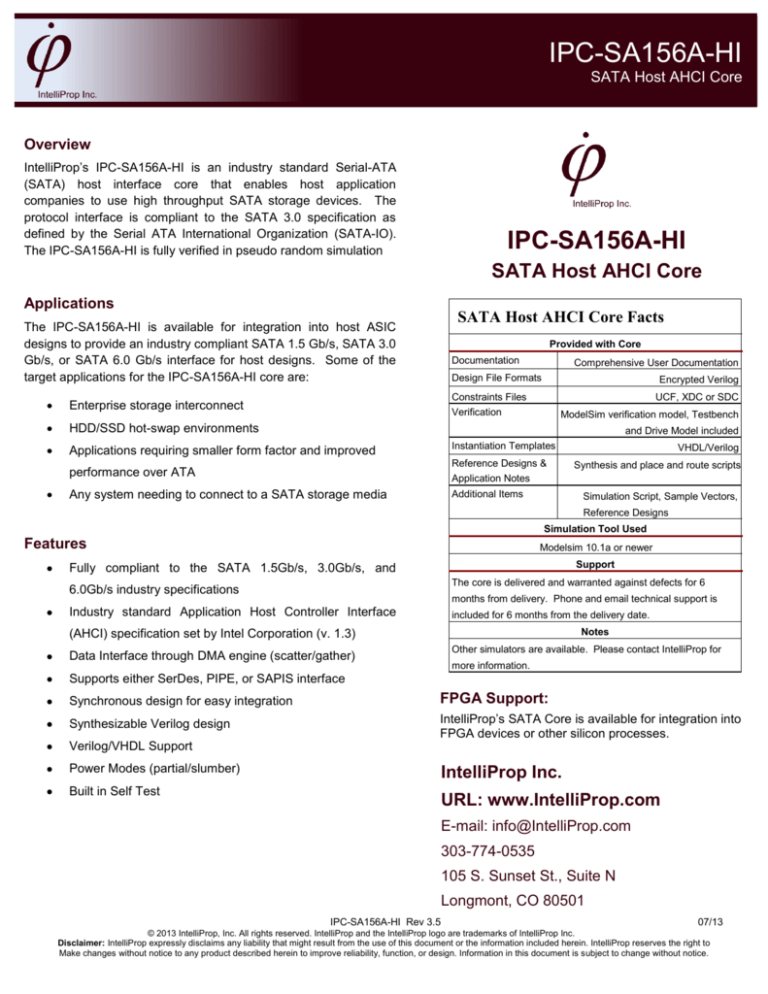

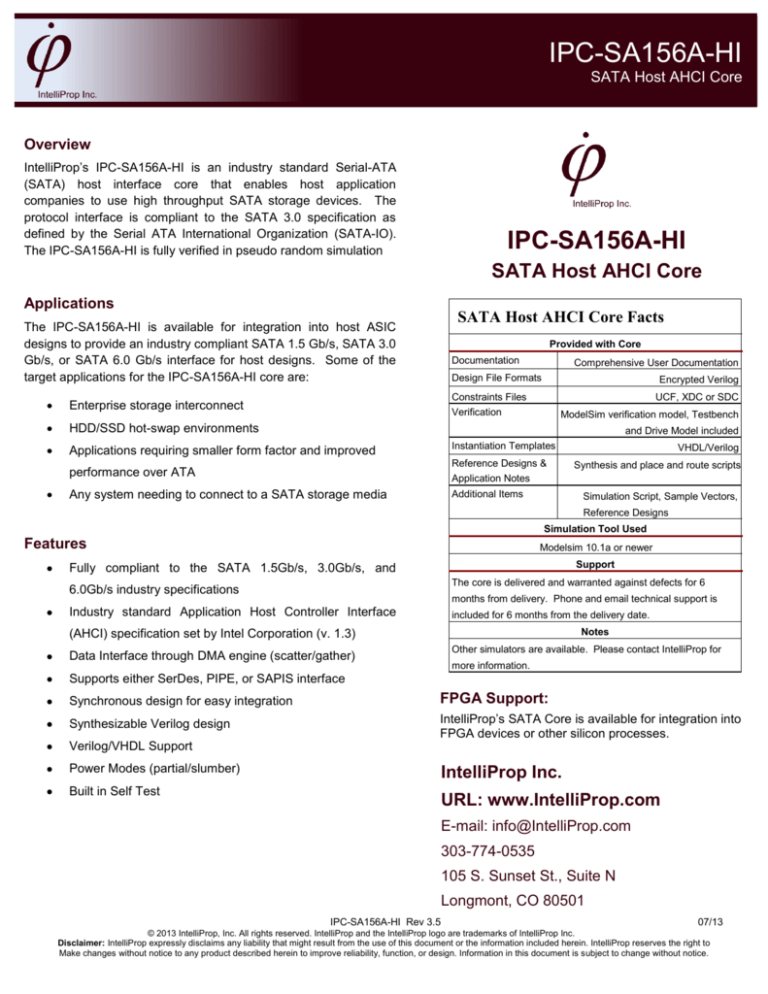

SATA Host AHCI Core Facts

The IPC-SA156A-HI is available for integration into host ASIC

designs to provide an industry compliant SATA 1.5 Gb/s, SATA 3.0

Gb/s, or SATA 6.0 Gb/s interface for host designs. Some of the

target applications for the IPC-SA156A-HI core are:

Enterprise storage interconnect

HDD/SSD hot-swap environments

Provided with Core

Documentation

Comprehensive User Documentation

Design File Formats

Encrypted Verilog

Constraints Files

UCF, XDC or SDC

Verification

ModelSim verification model, Testbench

and Drive Model included

Applications requiring smaller form factor and improved

Instantiation Templates

performance over ATA

Reference Designs &

Application Notes

Any system needing to connect to a SATA storage media

Additional Items

VHDL/Verilog

Synthesis and place and route scripts

Simulation Script, Sample Vectors,

Reference Designs

Simulation Tool Used

Features

Modelsim 10.1a or newer

Support

Fully compliant to the SATA 1.5Gb/s, 3.0Gb/s, and

The core is delivered and warranted against defects for 6

6.0Gb/s industry specifications

months from delivery. Phone and email technical support is

Industry standard Application Host Controller Interface

included for 6 months from the delivery date.

Notes

(AHCI) specification set by Intel Corporation (v. 1.3)

Other simulators are available. Please contact IntelliProp for

Data Interface through DMA engine (scatter/gather)

Supports either SerDes, PIPE, or SAPIS interface

Synchronous design for easy integration

FPGA Support:

Synthesizable Verilog design

IntelliProp’s SATA Core is available for integration into

FPGA devices or other silicon processes.

Verilog/VHDL Support

Power Modes (partial/slumber)

Built in Self Test

more information.

IntelliProp Inc.

URL: www.IntelliProp.com

E-mail: info@IntelliProp.com

303-774-0535

105 S. Sunset St., Suite N

Longmont, CO 80501

IPC-SA156A-HI Rev 3.5

07/13

© 2013 IntelliProp, Inc. All rights reserved. IntelliProp and the IntelliProp logo are trademarks of IntelliProp Inc.

Disclaimer: IntelliProp expressly disclaims any liability that might result from the use of this document or the information included herein. IntelliProp reserves the right to

Make changes without notice to any product described herein to improve reliability, function, or design. Information in this document is subject to change without notice.

IPC-SA156A-HI

www.IntelliProp.com

SATA Host AHCI Core

SATA Core Block Diagram

Functional Description

The IPC-SA156A-HI is designed to be connected to a SATA-compliant device application to send and receive Out of

Band (OOB) signals, primitives, and SATA Frame Information Structures (FIS). The SATA host core, as shown in the

block diagram, is comprised of three blocks (Phy Layer, Link Layer, and Trn Layer), and the Application, AHCI block,

SerDes, and FIFO Interfaces.

Block Descriptions

2

Phy Layer and SerDes Interface.

The PHY layer block includes the OOB state machine, 8b/10b encoder and decoder, speed negotiation logic,

running disparity checker and logic to check valid Dwords and align primitives. The PHY layer also includes a

SerDes that can connect to an analog PHY using 10-bit or digital 1-bit interface.

LINK Layer

The Link layer block includes the link state machine, Cyclic Redundancy Check (CRC) generator, and scrambler.

The Link layer includes logic to handle Partial and Slumber power down modes and BIST.

IPC-SA156A-HI Rev 3.5

07/13

© 2013 IntelliProp, Inc. All rights reserved. IntelliProp and the IntelliProp logo are trademarks of IntelliProp Inc.

Disclaimer: IntelliProp expressly disclaims any liability that might result from the use of this document or the information included herein. IntelliProp reserves the right to

Make changes without notice to any product described herein to improve reliability, function, or design. Information in this document is subject to change without notice.

IPC-SA156A-HI

www.IntelliProp.com

SATA Host AHCI Core

TRN (Transport) Layer

The Transport layer of the SATA host core includes a transport state machine, FIS Header RAM, shadow register

block, FIFO interface, and interrupt mechanism. It is also used to process the received FIS.

Application Interface

The Application block provides a pathway for the host system to monitor and control the SATA host core. The

Application layer handles all ATA protocol sequences.

AHCI Interface

Alternative to the Application block, the AHCI also provides a pathway for the host system to monitor and control

the SATA host core. The figure below shows how these interfaces work with the host core and in possible host

systems.

Support

IntelliProp’s SATA Host core is delivered and warranted against defects for six (6) months. Purchase of the SATA core

includes phone and email technical support for six (6) months from the delivery date.

Deliverables

The core includes everything required for successful implementation:

3

RTL encrypted code

Self-checking test bench in Verilog Modelsim 10.1a (or newer). Other simulators may be supported, please check

with IntelliProp.

Simulation script, vectors, and expected results

Synthesis or place and route script

Comprehensive user documentation

IPC-SA156A-HI Rev 3.5

07/13

© 2013 IntelliProp, Inc. All rights reserved. IntelliProp and the IntelliProp logo are trademarks of IntelliProp Inc.

Disclaimer: IntelliProp expressly disclaims any liability that might result from the use of this document or the information included herein. IntelliProp reserves the right to

Make changes without notice to any product described herein to improve reliability, function, or design. Information in this document is subject to change without notice.

IPC-SA156A-HI

www.IntelliProp.com

SATA Host AHCI Core

Core Modifications

Modifications are generally not permitted to the SATA host core. Any modifications that are requested must be presented

to IntelliProp to determine the plausability of integrating such changes.

Verification Methods

The SATA Host AHCI Core design is used in multiple SATA applications in which it has been tested with multiple hosts at

Gen 1, Gen 2, and Gen 3 speeds as well as multiple drives. Verification done internally at IntelliProp was completed using

a constrained random testbench, Specman e and Cadence IUS tools, and a coverage driven methodology.

Recommended Design Experience

Users of the SATA Host Core are expected to have a good working knowledge of the SATA Specification and Application

layer knowledge of the SATA protocol.

FPGA Support

IntelliProp’s SATA Core is available for integration into devices offered by most vendors.

Contact IntelliProp:

105 S. Sunset St., Ste N

Longmont CO 80501

303-774-0535

E-Mail: info@IntelliProp.com

URL: www.IntelliProp.com

4

IPC-SA156A-HI Rev 3.5

07/13

© 2013 IntelliProp, Inc. All rights reserved. IntelliProp and the IntelliProp logo are trademarks of IntelliProp Inc.

Disclaimer: IntelliProp expressly disclaims any liability that might result from the use of this document or the information included herein. IntelliProp reserves the right to

Make changes without notice to any product described herein to improve reliability, function, or design. Information in this document is subject to change without notice.