Simple FET DC Bias Circuits

advertisement

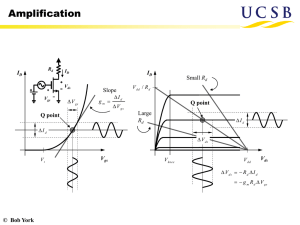

Simple FET DC Bias Circuits © Bob York Load-Line and Q-point +Vdd KVL: RD Id Vout Vds Vgs Vdd I d Rd Vds Id Vdd 1 Vds Rd Rd Id Smaller Rd Vdd / Rd Vgs= Vtn + 2.0 Q point Larger Rd Vgs= Vtn + 1.5 This is the equation of a line that can be superimposed on the FET I-V characteristics as shown at right. This is the “load-line”. Vgs= Vtn + 1.0 Vknee Vdd Increasing Vgs Consider the effect of a drain resistor in the comnon-source configuration: Vds • The points of intersection represent the allowed device voltages and drain current for the resistor-FET combination. These are the “quiescent” operating conditions or “Q points”, i.e. the DC bias conditions. • There are a number of possible Q-points along the load-line, depending on the gate voltage. It is the job of the circuit designer to choose this Q-point. • The choice of Q-point will vary with the circuit application. For simple amplifier circuits a Qpoint in the middle of the saturation region is often desirable. © Bob York Back to TOC FET DC Biasing Consider the design of the circuit to set a certain Q-point: FET Parameters: +10 V Design goal: Vout Vds Vgs= 4 45mA K n 5mA/V 2 RD Id Vt 1V Id Vout 6 V I d 20 mA Vgs= 3 20mA Vgs= 2 5mA To get a 4V drop across the drain resistor @ 20mA current requires a resistor value Vgs Rd The design goal puts the Q-point right in the middle of the saturation region in the I-V curves where 6 10 Vds 10 V 6 V 200 20mA I d K n (Vgs Vt ) 2 Vgs Vt Id 20 mA 1V 3V Kn 5mA/V 2 With a plot of the FET I-V curves we can quickly tell at a glance whether the Q-point is in the saturation or ohmic region. Without the visual plot we could make an initial guess and then check to see whether the answer is consistent with this assumption: Saturation requires: © Bob York Vds Vgs Vt 10 3 1 Back to TOC Simple NMOS Gate Bias Network The previous design example required two DC sources: a drain supply (+10V) and a gate supply (+3V) A simpler solution for enhancement-mode devices is to use just a single supply at the drain and generate the required gate voltage using a resistor divider: +10 V Voltage divider to set the gate voltage required for a certain Id +10 V 700 kΩ +3 V 200 Ω +6 V 20 mA Remember: no current flows into the gate. This simplifies the design and analysis of the gate bias circuit 300 kΩ In discrete circuits the gate bias resistors usually have large values. You will learn why in ECE 2C when we discuss AC amplifiers. In Integrated Circuit (IC) designs, large resistors take up too much space and a different approach is taken. We will explore this later. © Bob York Back to TOC Simple PMOS Biasing Example +9 V 1 MΩ Vsg Vg 2 MΩ Problem: Find the drain voltage and current assuming the following FET parameters: Vsd Vout Id 1 kΩ K p 1mA/V 2 The voltage at the gate node is: 2M Vg 9 V 6V 2 M 1M The source-gate voltage is then: Vsg 9 V 6 V 3V Assuming the device is in saturation, the drain current is: I d 1mA/V 2 3V 1V 4 mA and the output voltage is: ? Vsg Vtp 2 Vout I d Rd 4 mA 1k 4 V Double-check that the device is in saturation: Vsd Vtp 1V Vsd 9 V Vout 5V 5 3 1 Note: if the drain resistor was increased to 2kΩ the device would no longer be in saturation and we would need to re-analyze the circuit using the equations appropriate to the ohmic region. © Bob York Back to TOC Stabilizing the Bias Point: Source Resistance Device #1 All examples so far have used a constant Vgs bias scheme. The problem with this approach is evident when we consider things like temperature variations or manufacturing tolerances on device parameters. As shown at right, two different devices can yield a large difference in drain current when biased at the same voltage Vg Id ID Device #2 Vg I d Vds Vgs Vt1 Vt2 A simple solution is to add a source resistance. This provides negative feedback to stabilize the drain current with respect to device parameter variations Vg Vgs I d Rs Id Vg Rs 1 Vgs Rs Another “load-line” If drain current increases due to parameter change, Vs will rise and this lowers Vgs which in turn reduces Id © Bob York ID Id Vg Vg slope Rs Vgs Vgs Vg Vs 1 Rs I d RS Vt1 Vt2 Vg Vgs Back to TOC The Four-Resistor Bias Network The standard bias network for discrete designs +Vdd Vdd Rd Rs Design Procedure for a given FET • Specify Q-point (Id and Vds) Rg1 Vg Rg2 Id RD Vd Ig = 0 Vdd I d ( Rd Rs ) Vds Rd Rs Vs RS slope • Net resistance can be determined from load-line: Vds Vgs Load-line now a function of both Rd and Rs Vdd Vds Id 1 Rd Rs Increasing Vgs Id Vdd Vds • Often there will be constraints on Rd or Rs imposed by the application. If Vd or Vs is specified, then Rd Vdd Vd Id or Rs • Once Rs and Rd are known we can design the gate bias network. Required Vgs determined from I-V curves. In saturation: Vs Id Vgs Vt Id Kn • Then gate voltage and voltage-divider can be designed according to: Vg Vgs I d Rs © Bob York Rg 2 Vdd Vgs I d Rs Rg1 Rg 2 Always double-check that the design is consistent with assumptions! Back to TOC FET Bias Building Blocks Vdd A FET with drain and gate connected is a common building block in IC bias networks Rd This connection forces the device into saturation such that I d K n Vout Vt Id 2 Vout Vgs Vds Vdd Vout Rd W /L Common design problems: • Find the Rd that gives a specified Vout or Id Vout specified Rd 1 K n Vout Vt Id specified or Rd Vdd Vt Id 1 Kn Id Remember: the device W/L ratio can also be manipulated to vary Kn: 1 W K n kn 2 L • Find the Vout or Id for a given Rd Vout Vt Id © Bob York 1 1 4 K n Rd (Vdd Vt ) 1 2 K n Rd Vdd Vt 1 1 1 4 K n Rd (Vdd Vt ) 2 2 K n Rd Rd Back to TOC Some Examples with Drain-Gate Connection Can you find Id and Vout in each case? +5 V +5 V 4 mA +5 V 3 kΩ Vout Vout Vout Vout 4 mA 3 kΩ Assume: Vt 1V +5 V +5 V +5 V K 1mA/V 2 4 mA Vout 3 kΩ Vout Vout 4 mA 3 kΩ -5 V © Bob York Vout -5 V -5 V Back to TOC