MSP Debuggers User's Guide

advertisement

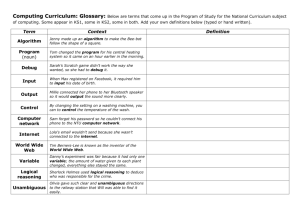

User's Guide SLAU647C – July 2015 – Revised February 2016 MSP Debuggers This manual describes the use and the features of all MSP debug probes. It includes information about the debugger probe hardware and software. It documents frequently asked questions on how to enable and disable certain features. It shows the differences between the debug probes and offers a guide on how to identify the specific version of the debug probe hardware. 1 2 3 4 5 Contents Introduction ................................................................................................................... 3 MSP Debug Probe Overview ............................................................................................... 4 Hardware Identification ...................................................................................................... 6 Hardware Installation ........................................................................................................ 8 Debug Probes Hardware and Software ................................................................................. 12 List of Figures 1 eZ-FET Windows Enumeration ............................................................................................ 6 2 eZ-FET Emulation IP ........................................................................................................ 6 3 eZ-FET Lite Emulation IP ................................................................................................... 6 4 eZ430 Emulation IP 5 eZ430 Windows Enumeration .............................................................................................. 7 6 MSP Flasher Driver Install Notification .................................................................................. 10 7 CCS Cloud Agent Installation ............................................................................................. 11 8 Successful CCS Cloud Agent Installation ............................................................................... 11 9 MSP Ecosystem ............................................................................................................ 12 10 MSP-FET Top View ........................................................................................................ 14 11 MSP-FET Bottom View .................................................................................................... 14 12 MSP-FET 14-Pin JTAG Connector 13 MSP-FET USB Debugger, Schematic (1 of 5) ......................................................................... 19 14 MSP-FET USB Debugger, Schematic (2 of 5) ......................................................................... 20 15 MSP-FET USB Debugger, Schematic (3 of 5) ......................................................................... 21 16 MSP-FET USB Debugger, Schematic (4 of 5) ......................................................................... 22 17 MSP-FET USB Debugger, Schematic (5 of 5) ......................................................................... 23 18 MSP-FET USB Debugger, PCB (Top)................................................................................... 23 19 MSP-FET USB Debugger, PCB (Bottom) ............................................................................... 23 20 MSP-FET430UIF Version 1.4a Top and Bottom Views ............................................................... 25 21 MSP-FET430UIF Version 1.3 Top and Bottom Views 22 MSP-FET430UIF 14-Pin JTAG Connector.............................................................................. 26 23 MSP-FET430UIF USB Interface, Schematic (1 of 4) .................................................................. 28 24 MSP-FET430UIF USB Interface, Schematic (2 of 4) .................................................................. 29 25 MSP-FET430UIF USB Interface, Schematic (3 of 4) .................................................................. 30 ......................................................................................................... ...................................................................................... ................................................................ 7 17 25 MSP430, E2E, EnergyTrace are trademarks of Texas Instruments. OS X is a registered trademark of Apple, Inc. IAR Embedded Workbench is a trademark of IAR Systems. Linux is a registered trademark of Linus Torvalds. Windows is a registered trademark of Micosoft Corporation. All other trademarks are the property of their respective owners. SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 1 www.ti.com 26 MSP-FET430UIF USB Interface, Schematic (4 of 4) .................................................................. 31 27 MSP-FET430UIF USB Interface, PCB .................................................................................. 32 28 eZ-FET and eZ-FET Lite (Top View) .................................................................................... 33 29 eZ-FET Rev1.3 (Top View) 30 31 32 33 34 35 36 37 38 39 40 41 42 ............................................................................................... eZ-FET or eZ-FET Lite Debug Connector .............................................................................. MSP-FET to LaunchPad Pin Assignments ............................................................................. MSP-FET to LaunchPad Wiring Diagram ............................................................................... eZ-FET Schematic (USB Connection) ................................................................................... eZ-FET Schematic (Emulation MCU) .................................................................................... eZ-FET Schematic DCDC (No eZ-FET Lite) ........................................................................... eZ430 Emulation ........................................................................................................... eZ430 Debug Connector on MSP-EXP430G2 LaunchPad ........................................................... eZ430 Schematic (Emulation MCU) ..................................................................................... eZ430 Schematic (USB Connection) .................................................................................... MSP-FET430PIF ........................................................................................................... MSP-FET430PIF FET Interface Module, Schematic .................................................................. MSP-FET430PIF FET Interface Module, PCB ......................................................................... 33 35 36 36 37 38 39 40 41 42 43 44 45 46 List of Tables 2 1 Debug Probes Features and Device Compatibility ...................................................................... 4 2 MSP-FET Backchannel UART Implementation ........................................................................ 15 3 MSP-FET Backchannel UART Activation Commands 4 MSP-FET MSP Target BSL Activation Commands .................................................................... 16 5 MSP-FET LED Signals .................................................................................................... 17 6 MSP-FET Pin States ....................................................................................................... 18 7 MSP-FET430UIF LED Signals 8 MSP-FET430UIF Pin States .............................................................................................. 27 9 eZ-FET and eZ-FET Lite Backchannel UART Implementation....................................................... 34 10 eZ-FET and eZ-FET Lite Backchannel UART Activation Commands ............................................... 35 11 eZ-FET LED Signals ....................................................................................................... 35 12 eZ-FET and eZ-FET Lite Pin States ..................................................................................... 36 13 eZ430 Backchannel UART Implementation 14 eZ430 Pin States ........................................................................................................... 41 MSP Debuggers ................................................................ ........................................................................................... ............................................................................ 16 26 41 SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Introduction www.ti.com 1 Introduction 1.1 Related Documentation From Texas Instruments MSP430™ Hardware Tools User's Guide (SLAU278) IAR Embedded Workbench™ Version 3+ for MSP430™ User's Guide (SLAU138) Advanced Debugging Using the Enhanced Emulation Module (EEM) With Code Composer Studio™ Version 6 (SLAA393) MSP430™ Programming With the Bootloader (BSL) (SLAU319) MSP430™ Programming Via the JTAG Interface (SLAU320) 1.2 1.3 Terms and Abbreviations Term Definition BSL Bootloader CCS Code Composer Studio development tool for MSP430 CDC Communications device class CPU Central processing unit CRC Cyclic redundancy check CTS Clear to send FET Flash emulation tool I2C Inter-Integrated Circuit 2-wire communication bus IAR EW430 IAR Embedded Workbench development tool for MSP430 JTAG Joint Test Action Group JTAG 4-wire 4-wire JTAG protocol communication MCLK Master clock MSP Mixed signal processor MSP-FET MSP debug probe MSP-FET430 UIF MSP debug probe MSPDebugStack Dynamic library (Windows®), shared object (Linux®), or dy library (OS X®) that offers functions to access and debug MSP430 devices using an MSP debug probe PC Personal computer RTS Request to send RX Receive data SBW Spy-Bi-Wire (2-wire JTAG protocol) communication TX Transmit data UART Universal asynchronous receiver/transmitter UIF USB interface to debug and access MSP derivatives USB Universal serial bus If You Need Assistance Support for the MSP microcontrollers and the development tools is provided by the TI Product Information Center (PIC). Contact information for the PIC can be found on the TI website at www.ti.com/support. The TI E2E™ Community support forums for the MSP microcontrollers also provide open interaction and support from a community of peer engineers, TI engineers, and other experts. Additional device-specific information can be found on the MSP website. SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 3 MSP Debug Probe Overview 2 www.ti.com MSP Debug Probe Overview Table 1 is an overview of the capabilities and features for the available MSP debug probes. CAUTION Never disconnect the JTAG or emulator USB cable during an active debug session. Always terminate a running debug session properly, by clicking on the "Terminate" icon, before disconnecting the target device. Supports only F20xx, G2x01, G2x11, G2x21, G2x31 MSP-FET430UIF MSP-FET eZ-FET Emulation IP eZ-FET Lite Emulation IP Supports all programmable MSP430 and CC430 devices MSP-FET430PIF MSP-EXP430F5529 MSP-EXP430FR5739 LaunchPad (MSP-EXP430G2) eZ430-Chronos MSP-WDSxx Metawatch eZ430-RF2560 eZ430-RF2480 eZ430-F2013 Feature and MSP430 Device Support eZ430-RF2500 Table 1. Debug Probes Features and Device Compatibility (1) (2) (3) ✓ ✓ ✓ ✓ ✓ ✓ Supports F20xx, F21x2, F22xx, G2x01, G2x11, G2x21, G2x31, G2x53 ✓ Supports F20xx, F21x2, F22xx, G2x01, G2x11, G2x21, G2x31 ✓ ✓ Supports F5438, F5438A ✓ Supports BT5190, F5438A ✓ ✓ ✓ Supports only F552x ✓ Supports FR57xx, F5638, F6638 ✓ Supports only CC430F613x ✓ Supports MSP432Pxx Allows JTAG access protection (Fuse Blow) (4) Adjustable target supply voltage ✓ ✓ ✓ ✓ ✓ Fixed 2.8-V target supply voltage ✓ ✓ ✓ ✓ ✓ ✓ ✓ Fixed 3.3-V target supply voltage Fixed 3.6-V target supply voltage ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ 4-wire JTAG 2-wire JTAG (5) ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ BSL tool or mode Backchannel UART ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ Supported by CCS for OS X ✓ ✓ ✓ ✓ (1) (2) (3) (4) (5) 4 ✓ Supported by CCS for Linux Supported by CCS for Windows ✓ ✓ ✓ The MSP-FET430PIF is for legacy device support only. This emulation tool does not support any devices released after 2011. Refer to Section 3.1 to identify the hardware. The eZ-FET Emulation IP and eZ-FET Lite Emulation IP are used as the onboard emulation for the MSP LaunchPad tools. Refer to Section 5.5 for more information. The 2-wire JTAG debug interface is also referred to as Spy-Bi-Wire (SBW) interface. MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debug Probe Overview www.ti.com eZ430-F2013 eZ430-RF2500 eZ430-RF2480 eZ430-RF2560 MSP-WDSxx Metawatch eZ430-Chronos LaunchPad (MSP-EXP430G2) MSP-EXP430FR5739 MSP-EXP430F5529 MSP-FET430PIF MSP-FET430UIF MSP-FET eZ-FET Emulation IP eZ-FET Lite Emulation IP Table 1. Debug Probes Features and Device Compatibility (1) (2) (3) (continued) ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ Feature and MSP430 Device Support Supported by IAR EnergyTrace™, EnergyTrace++ SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated ✓ ✓ MSP Debuggers 5 Hardware Identification www.ti.com 3 Hardware Identification 3.1 How to Determine If Your Hardware is Based on eZ-FET or eZ-FET Lite • • • Check the installed tool drivers by using the Windows Device Manager. eZ-FET tools enumerate as CDC "MSP Debug Interface" and CDC "MSP Application UART1" devices (see Figure 1). Check the Experimenter Board or LaunchPad emulation section to find out if it is based on an eZ-FET tool. If it is based on an MSP430F5528 device, it is an eZ-FET tool. There is a small print on the silkscreen that indicates eZ-FET or eZ-FET Lite (see Figure 2 and Figure 3). Figure 1. eZ-FET Windows Enumeration Figure 2. eZ-FET Emulation IP Figure 3. eZ-FET Lite Emulation IP 6 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Hardware Identification www.ti.com 3.2 How to Determine If Your Hardware is Based on eZ430 • • Check the installed tool drivers by using the Windows Device Manager (see Figure 5). eZ430 tools enumerate as HID (Debugger port) and CDC (Backchannel UART) devices. Check the Experimenter Board to find out if it is based on an eZ430 tool (see Figure 4). If it is based on an MSP430F1612 and a TUSB3410, it is an eZ430 tool. Figure 4. eZ430 Emulation IP Figure 5. eZ430 Windows Enumeration 3.3 Signal Connections for In-System Programming and Debugging For details about the hardware connections of all debug probes refer to the "Signal Connections for InSystem Programming and Debugging" section of the MSP430 Hardware Tools User's Guide (SLAU278). 3.4 Using the Power Supply Feature of the eZ-FET and eZ-FET Lite The eZ-FET and the eZ-FET Lite only support a fixed voltage power supply. The maximum supply current is 75 mA. For more details, refer to the specific LaunchPad or experimenter board user's guide. NOTE: 3.5 These debug probes do not support externally powering of the device while debugging – if an external voltage is needed for stand-alone testing, the eZ-FET emulation section should not be connected through USB. If both external power and the USB power are connected, there could be a conflict that can damage the device. Using the Power Supply Feature of the MSP-FET430UIF and MSP-FET All MSP debug probes can supply targets with up to 100 mA through pin 2 of the 14-pin JTAG connector. NOTE: The target should not consume more than 60 mA at peak current, as it may violate the USB specification. Details can found on www.USB.org. Example: If the target board has a capacitor on the VCC line with a capacity of more than 10 µF, it may cause an inrush current during capacitor charging that may exceed 60 mA. In this case, the current should be limited by the design of the target board, or an external power supply should be used. SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 7 Hardware Installation www.ti.com Target VCC is selectable in a range between 1.8 V and 3.6 V in steps of 0.1 V. Alternatively, the target can be supplied externally. In this case, the external voltage should be connected to pin 4 of the 14-pin JTAG connector. MSP-FET tools adjusts the level of the JTAG signals to automatically match the external VCC. NOTE: Only pin 2 (MSP-FET tool supplies target) or pin 4 (target is externally supplied) must be connected. Both connections are not supported at the same time. Even if an external supply powers the target device on the target socket module and any user circuitry connected to the target socket module, the MSP-FET tool continues to be powered from the PC through the USB interface. NOTE: MSP-FET430PIF only The PC parallel ports with a connected MSP-FET430PIF can source a maximum current of 25 mA. Because of the ultra-low-power requirement of the MSP430, a stand-alone MSP430 does not exceed the provided current. However, if additional circuits are added, the current limit could be exceeded. In this case, the MSP430 must be supplied externally. 4 Hardware Installation This section describes how to install the drivers for all MSP debug probes. The drivers are needed to enable the IDE (integrated development environment) to use the debug probe that is connected to the system. There are four different ways to install the drivers. 1. CCS desktop: During the CCS setup, all MSP debug probe drivers are installed automatically for all supported operation systems. 2. CCS cloud: The automatic driver installer is included inside the TI Cloud Agent Application, which must be downloaded when connecting a local MSP debug probe to CCS cloud. 3. Stand-alone driver installer: The stand-alone driver installer is only available for Windows. It installs all MSP debug probe drivers automatically. 4. Using another supported IDE such as IAR EW430 or the MSP-Flasher: During the setup, all MSP debug probe drivers are installed automatically. 4.1 MSP-FET430PIF The MSP-FET430PIF has the following system requirements: It supports only Windows XP with IAR EW430 version 5.xx.x and Code Composer Studio version 5.x.x. No new development is scheduled to support MSP-FET430PIF. Follow these steps to install the hardware for the MSP-FET430PIF tool: 1. Use the 25-pin ribbon cable to connect the debugger interface module to the parallel port of the PC. The necessary driver for accessing the PC parallel port is installed automatically during CCS or IAR Embedded Workbench installation. Note that a restart is required after the CCS or IAR Embedded Workbench installation. 2. Use the 14-pin ribbon cable to connect the parallel-port debug interface to a target board which contains the target MSP430 device. 4.2 MSP-FET430UIF, MSP-FET, eZ-FET, and eZ-FET Lite NOTE: The built-in DC-DC converter of the MSP-FET and eZ-FET emulators causes a loaddependent amount of ripple on the output voltage (fripple = 1 kHz to 50 kHz, Vrms_ripple = 5 mV to 50 mV), which might affect sensitive analog and RF circuits that are supplied by the emulator. For such sensitive circuits, TI recommends temporarily increasing the amount of power supply decoupling used during development, using an emulator with an integrated linear regulator (MSP-FET430UIF or eZ-FET430), or using a separate bench supply. 8 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Hardware Installation www.ti.com Installation steps for the MSP-FET430UIF, MSP-FET, eZ-FET or eZ-FET Lite: 1. Install the IDE (TI CCS or IAR EW430) before connecting the debug probe to the PC. During IDE installation, the USB drivers for the debug probes are installed automatically. Make sure to use the latest IDE version; older versions might install USB drivers that do not recognize the connected debug probe. 2. Connect the debug probe to a USB port on the PC using the provided USB cable. 3. The following procedure applies to operation under Windows: (a) After connecting to the PC, the debug probe should be recognized automatically, as the USB device driver has been already installed together with the IDE. (b) However, if the driver is not automatically detected, the "Found New Hardware wizard" starts. Follow the instructions and point the wizard to the driver files. The default location for CCS is: c:\ti\ccsv6\ccs_base\emulation\drivers\msp430\USB_CDC. The default location for IAR Embedded Workbench is: <Installation Root>\Embedded Workbench x.x\430\drivers\<Win_OS>. 4. After connecting the debug probe to a PC, the probe performs a self-test. If the self-test passes, the green LED stays on. For a complete list of LED signals, refer to the "LED Signals" of each debug probe in Section 5.6 through Section 5.8. 5. Connect the debug probe with the target board using the 14-pin ribbon cable. 6. When using a target socket board, make sure that the MSP430 device is properly inserted in the socket and that pin 1 of the device (indicated with a circular indentation on the top surface) aligns with the "1" mark on the PCB. NOTE: 4.3 To use the debug probe without an IDE, install the stand-alone driver package. The standalone driver installer can be found at http://www.ti.com/mspds under the heading MSPDSUSB-DRIVERS. eZ430-Based Experimenter Boards and LaunchPad Kits For driver installation on a Windows operating system, follow the steps in Section 4.2. NOTE: 4.4 eZ430-tools are not supported on USB3.0 ports. eZ430 tools are supported on Windows operating systems only—Linux and OS X are not supported. Hardware Installation Using the MSP Flasher MSP Flasher is an open-source shell-based interface for programming any MSP430 device through a MSP Debug Stack and provides the most common functions on the command line. MSP Flasher can be used to download binary files (.txt or .hex) directly to the MSP430 memory without the need for an IDE like CCS or IAR. It can also be used to extract firmware directly from a device, set hardware breakpoints, and lock JTAG access permanently. MSP Flasher supports the following operating systems: • Windows 10 32-bit or 64-bit • Windows 8 32-bit or 64-bit • Windows 7 32-bit or 64-bit • Windows XP 32-bit or 64-bit • Ubuntu 32-bit • OS X 64-bit SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 9 Hardware Installation www.ti.com Installation steps for the MSP-FET430UIF, MSP-FET, eZ-FET or eZ-FET Lite: 1. After successfully downloading and executing the MSP Flasher installer, it prompts you to execute the stand-alone driver installer for the MSP debug probes. Figure 6. MSP Flasher Driver Install Notification 2. Follow the steps given by the stand-alone driver installer for debug probe driver installation. 3. After successful driver installation, connect the debug probe to a USB port on the PC using the provided USB cable. 4. After connecting the debug probe to a PC, it performs a self-test. If the self-test passes, the green LED stays on. For a complete list of LED signals, refer to the "LED Signals" of every debug probe in Section 5.6 through Section 5.8. 5. Connect the debug probe with the target board using the 14-pin ribbon cable. 6. When using a target socket board, make sure that the MSP430 device is properly inserted in the socket and that its pin 1 (indicated with a circular indentation on the top surface) aligns with the "1" mark on the PCB. 10 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Hardware Installation www.ti.com 4.5 Hardware Installation Using CCS Cloud CCS Cloud is web-based IDE that allows you to create, edit, and build CCS and Energia projects. After a project is successfully built, it can be downloaded and run on the connected LaunchPad or any other debug probe. Basic debugging features, like setting breakpoints or viewing values of target variables are now supported. CCS Cloud can be used with the local debug probe connected to the PC through USB. To support this configuration, install the "CCS Cloud browser extension", and download and install the "TI Cloud Agent Application". For more details, refer to the CCS cloud documentation at http://processors.wiki.ti.com/index.php/TI_Cloud_Agent. Figure 7. CCS Cloud Agent Installation Figure 8. Successful CCS Cloud Agent Installation After the successful Agent installation, download the application by clicking the Flash or Debug button in CCS Cloud. SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 11 Debug Probes Hardware and Software 5 www.ti.com Debug Probes Hardware and Software This section includes all specifications and features of all MSP debug probes. The debug probe hardware and different debug mode configuration and setting are descried. Figure 9 is an overview of the MSP ecosystem showing the relations between IDE and debug probe and the MSP device itself. MSP-Flasher MSPDebugStack USB connection SBW2 JTAG/ SBW2 JTAG/SBW2 MSP430 Figure 9. MSP Ecosystem 5.1 MSPDebugStack The MSPDebugStack is the host side interface to all MSP debug probes. It is a library for controlling and debugging Texas Instruments MSP ultra-low power microcontrollers during software development phase. For this purpose the MSP microcontroller is controlled by the MSPDebugStack using the MSP device's JTAG interface. The MSPDebugStack provides device control (for example, run and stop), memory programming and debugging functionality (for example, breakpoints). The MSPDebugStack supports Windows, Linux, and OS X operating systems. The debug probe firmware for all field updatable tools is included in the MSPDebugStack. It automatically detects if an update of the debug probe is required. For more details and information see www.ti.com/mspds. 12 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Debug Probes Hardware and Software www.ti.com 5.2 Ultra-Low-Power Debug Support Ultra-low power (ULP) debug support enables users to debug in the low-power modes that are used in their application software. If this option is enabled during an active debug session in IAR EW430 or Code Composer studio, the target MSP430 device enters the low-power modes. Wake-up times can be measured on F5xx, F6xx, FR5xx, and FR6xx devices. For some MSP430 devices, special debug features are disabled in this mode; for example, setting breakpoints (hardware and software) while device is running in ULP mode. NOTE: NOTE: When debugging with EnergyTrace++ active, this mode must be used. Measured currents might be slightly higher than in stand-alone mode (EnergyTrace) due to the active debugger connection. For more details and information refer to the MSP430 Ultra-Low-Power LPMx.5 Mode section of the IDE user's guides for IAR EW430 (SLAU138) and CCS (SLAU157). 5.3 EnergyTrace™ Technology EnergyTrace Technology is an energy-based code analysis tool that measures and displays the application's energy profile, which helps to optimize it for ultra-low power consumption. MSP devices with built-in EnergyTrace+[CPU State]+[Peripheral States] (or in short EnergyTrace++) technology allow real-time monitoring of many internal device states while user program code executes. EnergyTrace++ technology is supported on selected MSP devices and debuggers (see Table 1). EnergyTrace mode (without the "++") is a fundamental part of EnergyTrace Technology and enables analog energy measurement to determine the energy consumption of an application but does not correlate it to internal device information. The EnergyTrace mode is available for all MSP devices with selected debuggers, including CCS (see Table 1). For more details about the EnergyTrace Technology, refer to http://www.ti.com/tool/energytrace. 5.4 Unlimited Software Breakpoints in Flash, FRAM, and RAM All MSP430 debug tools support the use of Software breakpoints in Flash, FRAM, and RAM. Software breakpoints enable the user to set an unlimited number of breakpoints during an active debug session. Without Software Breakpoints enabled, the number of breakpoints which can be set is limited to the number of hardware breakpoints available by the specific MSP device.. All MSP debug tools prefer the use of hardware breakpoints as much as possible. However, if the MSP breakpoint logic runs out of hardware breakpoints, software breakpoints are used automatically (if enabled in the IDE). NOTE: When the debug session is closed, all software breakpoints are erased and the original memory content is restored. For more details about the software breakpoints and their IDE-specific use, refer to the "Breakpoint Types" section in the IDE user's guides for IAR EW430 (SLAU138) and CCS (SLAU157). For a practical example of different breakpoint types, refer to the application report Advanced Debugging Using the Enhanced Emulation Module (EEM) With Code Composer Studio Version 6 (SLAA393). SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 13 Debug Probes Hardware and Software 5.5 www.ti.com JTAG Access Protection (Fuse Blow) Different MSP430 devices implement different methods to prevent JTAG debug access to the MSP430 target device. JTAG fuse: • Available on 1xx, 2xx, and 4xx families (except FRxx and I20xx devices). • Applying a high voltage to test the TEST pin of the MSP430 target device blows an actual physical polyfuse and disables the JTAG interface. JTAG lock without password (eFuse/"soft" fuse): • Available on 5xx, 6xx, and FRxx families. • A certain lock pattern is written into the MSP430 target memory to disable the JTAG interface. JTAG lock with password: • Available only FRxx families. • A user-defined password can disable JTAG access to the MSP430 target device. • Using CCS, EW430, or the MSP Flasher, applying the configured password to the MSP430 target restores JTAG access Memory protection by custom startup code (SUC): • Available on only the i20xx family (for example, the MSP430i2040 device). • Custom startup code can enable or disable JTAG access to the MSP430i20xx target device. NOTE: Only the MSP-FET and the MSP-FET430UIF support JTAG access protection to disable JTAG access. For more details how the JTAG access protection mechanism is implemented refer to the "JTAG Access Protection" section in MSP430 Programming Via the JTAG Interface (SLAU320). 5.6 MSP-FET Stand-Alone Debug Probe The MSP-FET is a powerful debug probe for application development supporting all MSP430 microcontrollers. The MSP-FET provides a USB interface to program and debug the MSP430 devices in-system through the JTAG interface or the pin-saving Spy-Bi-Wire (2-wire JTAG) protocol. Furthermore, the USB interface can be used for Backchannel UART and MSP target BSL communication. UART BSL and I2C BSL communication modes are supported. The MSP-FET development tool supports development with all MSP430 devices and is designed for use with PCBs that contain MSP430 devices; for example, the MSP430 target socket boards. Figure 10. MSP-FET Top View 14 MSP Debuggers Figure 11. MSP-FET Bottom View SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Debug Probes Hardware and Software www.ti.com 5.6.1 General Features The following features are provided by the MSP-FET debug probe. Features: • MSP-FET is supported since: – CCS v6.0.0 – IAR EW430 v5.60.7 and v6.10.1 • Operating systems: OS X, Linux, Windows • Software configurable supply voltage between 1.8 V and 3.6 V at 100 mA • External voltage detection • Supports JTAG security fuse blow to disable debugging • Supports all MSP430 boards with JTAG header • Supports both JTAG and Spy-Bi-Wire (2-wire JTAG) debug protocols • EnergyTrace and EnergyTrace++ support • Software breakpoints in Flash, FRAM, and RAM • MSPDS application backchannel UART included • Target BSL communication mode available • Flash and FRAM programming support • Debug probe firmware field update is supported (4) 5.6.2 Backchannel UART The MSP-FET supports the Backchannel UART functionality only when using an MSPDebugStack v3.4.1.0 or higher for the MSP-FET connection. The baud rates that are supported depend on the target configuration and the debug settings. Table 2 shows which baud rates are supported with certain configuration combinations. ✓ means that the corresponding baud rate is supported without any data loss with the specified combination of settings. ✗ means that the corresponding baud rate is not supported (data loss is expected) with the specified combination of settings. (4) Enable new device support by in field firmware updates Table 2. MSP-FET Backchannel UART Implementation Target MCLK Frequency: 1 MHz 8 MHz Debugger: Flow Control: 5.6.2.1 1 MHz 8 MHz Active Inactive No Yes No Yes No Yes No Yes 4800 baud ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ 9600 baud ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ 19200 baud ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ 28800 baud ✗ ✓ ✓ ✓ ✓ ✓ ✓ ✓ 38400 baud ✗ ✓ ✗ ✓ ✗ ✓ ✗ ✓ 57600 baud ✗ ✓ ✗ ✓ ✗ ✓ ✗ ✓ 115200 baud ✗ ✗ ✗ ✓ ✗ ✗ ✗ ✓ UART Backchannel Activation Commands The MSP-FET supports two different Backchannel UART modes, one with flow control and one without. The different modes can be selected by opening the corresponding COM port with a dedicated baud rate. See Table 3 for the specific baud rates for each command. SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 15 Debug Probes Hardware and Software www.ti.com NOTE: The baud rates used by these activation commands cannot be used for communication. NOTE: The Backchannel UART is disabled until the COM port is opened with a valid baud rate. If none of the specified commands are transferred before setting the communication baud rate, communication starts with the default settings: 3.3 V target VCC, no flow control mechanism. Table 3. MSP-FET Backchannel UART Activation Commands Baud Rate 5.6.3 Command 9620 Set all backchannel UART pins to high impedance – no current flow into target device 9621 Configure backchannel UART communication without handshake (default start behavior) 9622 Configure backchannel UART communication with handshake 9623 Voltage configuration command. When this command is received, target VCC is set to 3.3 V. After target VCC is configured, it is switched through to the target device. Target BSL Connection and BSL-Scripter Support The MSP-FET can be used for communication with the target device bootloader (BSL) through the I2C and UART protocols. The activation of the different protocols is equivalent to the MSP-FET backchannel UART. See Table 4 for command details. The BSL-Scripter software in the zip file that is included with MSP430™ Programming With the Bootloader (BSL) (SLAU319) implements support for these activation commands and performs the correct sequence according to the communication interface (UART, I2C) that is specified in the script. In MSP-FET BSL communication mode, flow control is not available, because this is not supported by the MSP target device BSL. UART BSL: The MSP-FET BSL UART mode supports the following baud rates: 9600, 14400, 19200, 28800, 38400, 56000, 57600, and 115200. For the BSL UART, 8 + 1 + even parity is used. I2C BSL: The MSP-FET is always the I2C master, and the target device BSL is always the I2C slave. 7-bit I2C addressing mode is used with a fixed I2C slave address of 0x48. NOTE: If the MSP-FET is configured to support BSL communication, debugger functionality is disabled. To switch to debugger mode, either perform a power cycle (unplug the USB cable) or configure the baud rate to 8001. The BSL mode is disabled until sending a BSL entry baud rate command. Maximum I2C clock rate; 55 kHz Table 4. MSP-FET MSP Target BSL Activation Commands Baud Rate Command 2 9620 Set all UART or I C pins to high impedance – no current flow into target device 9601 BSL entry sequence and power up 3.3 V (UART BSL) – debugger is disabled 100000 or 100001 BSL entry sequence and power up 3.3 V (I2C BSL) – debugger is disabled 400000 or 400001 BSL entry sequence and power up 3.3 V (I2C BSL) – debugger is disabled 9623 Power up 3.3 V 8001 Activate debugger NOTE: The MSP-FET I2C interface is a software I2C implementation, which always runs with a speed of approximately 55 kHz. The four different speed configurations are supported for compatibility purposes with BSL-Scripter and the BSL-Rocket. 16 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Debug Probes Hardware and Software www.ti.com 5.6.4 LED Signals The MSP-FET shows its operating states using two LEDs, one green and one red. Table 5 lists all available operation modes. An or icon indicates that the LED is off, an or icon indicates that the LED is on, and an or icon indicates that the LED flashes. Table 5. MSP-FET LED Signals Power LED Mode LED Function MSP-FET not connected to PC or MSP-FET not ready; for example, after a major firmware update. Connect or reconnect MSP-FET to PC. MSP-FET connected and ready MSP-FET waiting for data transfer Ongoing data transfer – during active debug session An error has occurred; for example, target VCC over current. Unplug MSP-FET from target, and cycle the power off and on. Check target connection, and reconnect MSP-FET. Firmware update in progress. Do not disconnect MSP-FET while both LEDs are blinking slowly. FPGA update in progress. Do not disconnect MSP-FET while both LEDs are blinking rapidly. 5.6.5 Hardware This section includes MSP-FET hardware descriptions like the JTAG connector, schematics, and powerup states of the MSP-FET JTAG pins. 5.6.5.1 JTAG Target Connector Figure 12 shows the pinout of the MSP-FET JTAG connector. Figure 12. MSP-FET 14-Pin JTAG Connector SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 17 Debug Probes Hardware and Software 5.6.5.2 www.ti.com MSP-FET Pin States After Power Up Table 6 describes the electrical state of every JTAG pin after debug probe power up. Table 6. MSP-FET Pin States Pin Name 1 TDO/TDI 2 VCC_TOOL 3 TDI/VPP 4 5 After Power up When JTAG Protocol is Active When Spy-Bi-Wire Protocol is Active Hi-Z, pulled up to 3.3 V In, TDO In and Out, SBWTDIO (RST pin) 3.3 V Target VCC Target VCC Hi-Z, pulled up to 3.3 V Out, TDI Hi-Z, pulled up to VCC VCC_TARGET In, external VCC sense In, external VCC sense In, external VCC sense TMS Hi-Z, pulled up to 3.3 V Out, TMS Hi-Z, pulled up to VCC 6 N/C N/C N/C N/C 7 TCK Hi-Z, pulled up to 3.3 V Out, TCK Out, SBWTCK 8 TEST/VPP Out, Ground Out, TEST Hi-Z, pulled up to VCC 9 GND Ground Ground Ground 10 UART_CTS/SPI_CLK/I2C_SCL 11 RST Hi-Z, pulled up to 3.3 V Out, Target UART Clear- Out, Target UART ClearTo-Send Handshake input To-Send Handshake input Out, VCC Out, RST Ground In, Target UART TXD output 12 UART_TXD/SPI_SOMI/I2C_SDA Hi-Z, pulled up to 3.3 V In, Target UART TXD output 13 UART_RTS Hi-Z, pulled up to 3.3 V In, Target UART Readyto-Send Handshake output In, Target UART Ready-to Send Handshake output 14 UART_RXD/SPI_SIMO Hi-Z, pulled up to 3.3 V Out, Target UART RXD input Out, Target UART RXD input NOTE: To enable the UART, I2C or SPI pins, the correct invalid baud rate activation command must be sent (see MSP-FET Backchannel UART Activation Commands and MSP-FET MSP Target BSL Activation Commands). After this the pins switch into the state described in the Table 6. NOTE: MSP430BSL-SPI support is currently not available using the MSP-FET. The pin names used in Table 6 are the same as the names that are printed on the back of the MSP-FET. 18 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Schematics 5.6.5.3 Debug Probes Hardware and Software www.ti.com 1 A J1 A C D7 B0530W-7-F 0R R17 100n C6 B VBUS bypass 27R 27R C31 10p 1 C33 10p 1 C70 4.7u, dnp GND1 R62 100R C 100n C71 GND1 USB BSL activation VBUS5 VBUS PUR PU.0/DP PU.1/DM 1 P6.4/CB4/A4 VUSB A_VCC_DT 2 P6.5/CB5/A5 J5 A_VCC_DT_BSR 1k4 R2 R61 1M 1 VCC_DT_SENSE 3 P6.6/CB6/A6/DAC0 4 P6.7/CB7/A7/DAC1 5 P7.4/CB8/A12 LED0 7 P7.6/CB10/A14/DAC0 DCDC_TEST 8 P7.7/CB11/A15/DAC1 6 P7.5/CB9/A13 VCC_DT_REF DCDC_RST VCC_DCDC_REF 9 P5.0/VREF+/VEREF+ MCU_P2.1 DCDC_PULSE MCU_DMAE0 21 20 P2.3/P2MAP3 19 P2.2/P2MAP2 18 P2.1/P2MAP1 17 P2.0/P2MAP0 16 P5.6/ADC12CLK/DMAE0 P2.5/P2MAP5 P2.6/P2MAP6/R03 P2.7/P2MAP7/LCDREF/ DVCC1 D 1 Host MCU HOST_TDO USB interface 1 R3 100n R45 1 2 C23 1 C5 VREF+ 10 P5.1/VREF-/VEREF11 AVCC1 MCU_P2.2 22 AVCC_POD FPGA_RESET 12 AVSS1 13 XIN 14 XOUT MCU_P2.3 23 15 AVSS2 MCU_P2.4 24 U1 3 2 P1 MSP430F6638IPZR 1 1 220n C8 1 1 E P9.3/S4 71 P9.4/S3 72 P9.5/S2 73 P9.6/S1 74 P9.7/S0 75 FPGA_TCK FPGA_TDI FPGA_TMS FPGA_TDO FPGA_TRST MCU_P9.5 VCC_DT2SUPPLY_CTRL PWM_SETVF F HOST_RST P9.2/S5 70 HOST_SDA of A 3/12/2014 4k7 R28 4k7 R30 Rev 1 5 F HOST_SCL VCC_POD33 Debug i/f 27k R76 1n C55 P9.1/S6 69 GND1 P9.0/S7 68 1 MSP-FET Rev 1.2 MCU_P4.1 MCU_P4.2 MCU_P4.3 MCU_P4.4 MCU_P4.5 MCU_P4.6 MCU_P4.7 VCC_DT2TRGT_CTRL MCU_P8.1 MCU_P8.2 MCU_P8.3 DCDC_IO0 VCC_POD33 VCC_SUPPLY2TRGT_CTRL P4.2/TB0.2/S21 52 P4.3/TB0.3/S20 53 P4.4/TB0.4/S19 54 P4.5/TB0.5/S18 55 P4.6/TB0.6/S17 56 P4.7/TB0OUTH/SVMOUT57 P8.0/TB0CLK/S15 58 P8.1/UCB1STE 59 P8.2/UCA1TXD 60 P8.3/UCA1RXD 61 P8.4/UCB1CLK/UCA1ST62 DVSS2 63 DVCC2 64 P8.5/UCB1SIMO 65 P8.6/UCB1SOMI 66 P8.7/S8 67 1 3/12/2014 Number P4.1/TB0.1/S22 51 Title C Size Date Sheet VCC_POD33 R85 VCC_POD33 MCU_P2.5 25 E 1 2 3 4 Copyright © 2015–2016, Texas Instruments Incorporated 4.7u, dnp 1 + R1 10uF/6.3V 0R R50 MCU_P2.6 P7.2/XT2IN 84 19 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback DCDC_IO1 P5.7/RTCCLK 88 C14 1 TPD4E004DRYR 3 33k R60 AVCC_POD AVCC_POD 0R MCU_P2.7 P2.4/P2MAP4 VCC_POD33 1 HOST_TMS IO4 5 U5 2 IO2 4 5 VCC_POD33 C7 100n 1 C9 100n 1 AVCC1 General power supply DVCC2 VCC_POD33 DVCC3 VCC_POD33 DVCC1 + LED1 D2 PJ.2/TMS 94 IO3 4 3 GND LED D1 MCU_P4.0 100n C18 1 P4.0/TB0.0/S23 VSSU 76 PU.0/DP PU.0/DP 77 PU.1/DM PU.1/DM 79 P3.5/TA2.0/S26 VBUS VBUS 80 VUSB V18 V18 82 P3.2/TA1.1/S29 PUR PUR 78 P3.7/TA2.2/S24 50 P3.6/TA2.1/S25 49 MCU_P3.7 48 MCU_P3.6 47 MCU_P3.5 AVSS3 83 P3.1/TA1.0/S30 VCC_POD33 DVCC3 89 P1.3/TA0.2/S36 81 VUSB P3.4/TA2CLK/SMCLK/S 46 P3.3/TA1.2/S28 MCU_P3.4 C12 C11 C17 1 D MCU_P1.7 45 MCU_P3.3 P7.3/XT2OUT 85 P1.7/TA0.2/S32 41 P3.0/TA1CLK/CBOUT/S VBAK VBAK 86 P1.6/TA0.1/S33 40 MCU_P1.6 HOST_TCK P5.4/COM2/S41 0R, dnp R46 470R 1 C MCU_P1.5 44 MCU_P3.2 VCC_POD33 87 VBAT P1.5/TA0.4/S34 39 P1.4/TA0.3/S35 38 MCU_P1.4 37 MCU_P1.3 43 MCU_P3.1 DVSS3 90 MCU_P1.1 42 MCU_P3.0 P1.2/TA0.1/S37 MCU_P1.2 36 TEST/SBWTCK 91 A_VCC_SUPPLY_HOST A_VBUS5 LCDCAP/R33 P6.0/CB0/A0 97 HOST_TDI PJ.1/TDI/TCLK P5.5/COM3/S40 A_VF P6.1/CB1/A1 98 HOST_TEST P1.1/TA0.0/S38 35 PJ.0/TDO 92 P1.0/TA0CLK/ACLK/S3 34 MCU_P1.0 93 TDIOFF_CTRL PJ.3/TCK 95 VF2TDI_CTRL 33 P5.3/COM1/S42 LED1 32 HOST_RST 31 RST/NMI/SBWTDIO 96 COM0 30 A_VCC_SENSE0_TRGT 99 P6.2/CB2/A2 P5.2/R23 29 10uF/6.3V 1 1 B R47 470R 100 P6.3/CB3/A3 VCORE(2) 26 DVSS1 27 VCORE 28 VF2TEST_CTRL VCC 6 1 IO1 LED0 1 C16 VBAK 470n 220n 4.7n V18 1 11 10 7 6 Additional supply C15 VCORE 2 3 4 68p A VREF+ Figure 13. MSP-FET USB Debugger, Schematic (1 of 5) B 10n C50 100n C51 10n C52 10n C38 100n C39 10n C40 100n C41 10n C42 10n C48 2 C19 1 C FPGA_IO_TCK FPGA_IO_TDI 1 GND 2 GAA2/IO51RSB1 3 IO52RSB1 4 GAB2/IO53RSB1 5 IO95RSB1 6 GAC2/IO94RSB1 7 IO93RSB1 GEB0/IO74RSB1 GEA1/IO73RSB1 GEA0/IO72RSB1 VMV1 GNDQ MCU_P2.6 1 U2 IO17RSB0 83 MCU_P1.5 GDC2/IO56RSB1 IO18RSB0 82 MCU_P1.6 D MCU_P1.1 A3PN125-VQG100 1 1 E MCU_P3.4 R5 1k Title C Size Date GNDQ 75 VMV0 74 GBA2/IO25RSB0 73 IO26RSB0 72 GBB2/IO27RSB0 71 GBC2/IO29RSB0 70 IO31RSB0 69 VCC 68 GND 67 VCCIB0 66 GCC1/IO35RSB0 65 GCC0/IO36RSB0 64 GCA1/IO39RSB0 63 GCA0/IO40RSB0 62 GCB2/IO42RSB0 61 GCC2/IO43RSB0 60 GDC1/IO45RSB0 59 GDC0/IO46RSB0 58 GND 51 VPUMP 52 NC 53 TDO 54 TRST 55 VJTAG 56 GDA1/IO49RSB0 57 Number 3/12/2014 VCC_POD33 MCU_P3.5 MCU_P3.6 MCU_P3.7 MCU_P4.0 MCU_P4.1 VCC_POD15 VCC_POD33 MCU_P4.2 MCU_P4.3 MCU_P4.4 MCU_P4.5 MCU_P4.6 MCU_P4.7 MCU_P8.1 MCU_P8.2 MCU_P8.3 VCC_POD33 27R VCC_POD33 R44 R4 1k 1 MSP-FET Rev 1.2 1 Sheet F FPGA_TRST of A 3/12/2014 FPGA_TDO Rev 2 5 F 1 2 3 4 Copyright © 2015–2016, Texas Instruments Incorporated FPGA_DIR_CTRL_TCK FPGA_IO_TMS FPGA_DIR_CTRL_TMS FPGA_DIR_CTRL_TDI 8 IO92RSB1 25 24 23 22 21 20 GEB1/IO75RSB1 19 GEC1/IO77RSB1 18 VCCIB1 17 VCC 16 GFA2/IO83RSB1 15 GFA1/IO84RSB1 14 VCCPLF 13 GFA0/IO85RSB1 12 VCOMPLF 11 GFB0/IO86RSB1 10 GFB1/IO87RSB1 9 GND FPGA_IO_TDO FPGA_DIR_CTRL_TDO MCU_P2.7 FPGA_DIR_CTRL_RST FPGA_IO_TEST VCC_POD33 VCC_POD15 FPGA_DIR_CTRL_TEST FPGA_IO_UART_TXD FPGA_IO_UART_RXD FPGA_DIR_CTRL_UART_TXD FPGA_DIR_CTRL_UART_RXD VCC_POD33 FPGA_IO_UART_CTS 93 A 100n C49 FPGA 10n C34 100n C37 100n C47 MCU_P3.3 VMV1 GBA1/IO24RSB0 76 E 1 1 1 1 2 L3 33n 100n C22 1 10n C21 VCC_POD15 + VCC_PLF 10uF/6.3V 100n C20 10n C36 1 100n C35 VCC_POD33 VCC_JTAG 10n C46 1 VCC_POD33 VCC_PUMP 100n C45 GBA0/IO23RSB0 77 VCC_POD33 MCU_P2.5 GAC1/IO07RSB0 D MCU_P3.2 TMS FPGA_TDI VCC_POD33 87 VCCIB0 VCCIB1 1 C MCU_P3.1 TDI GBB1/IO22RSB0 78 FPGA_TMS VCC_POD15 VCC_POD33 VCC_PLF 10n 1 C44 1 100n 1 C43 B GBB0/IO21RSB0 79 50 MCU_P3.0 TCK 49 MCU_P1.7 GDA2/IO54RSB1 GBC1/IO20RSB0 80 48 81 47 MCU_P1.4 IO57RSB1 IO60RSB1 40 GBC0/IO19RSB0 46 GND 88 GND 38 GDB2/IO55RSB1 FPGA_TCK SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback MSP Debuggers 20 3 4 A VCC_POD15 45 IO15RSB0 84 44 MCU_P1.3 IO58RSB1 43 MCU_P1.2 IO13RSB0 85 42 IO11RSB0 86 IO59RSB1 41 MCU_P1.0 IO10RSB0 90 IO61RSB1 MCU_DMAE0 100 IO00RSB0 VCC_POD15 VCC 89 VCC 37 MCU_P2.4 GAC0/IO06RSB0 94 IO64RSB1 FPGA_TP2 IO09RSB0 91 36 GAB1/IO05RSB0 95 IO65RSB1 FPGA_TP1 IO62RSB1 FPGA_RESET IO66RSB1 FPGA_TP0 IO08RSB0 92 35 MCU_P2.3 FPGA_IO_RST IO63RSB1 34 GAB0/IO04RSB0 96 33 IO67RSB1 32 MCU_P2.2 31 MCU_P2.1 IO68RSB1 GAA1/IO03RSB0 97 30 GAA0/IO02RSB0 98 29 1 1 1 MCU_P9.5 99 IO01RSB0 FF/GEB2/IO70RSB1 27 FPGA_IO_UART_RTS GEC2/IO69RSB1 28 FPGA_DIR_CTRL_UART_RTS GEA2/IO71RSB1 26 FPGA_DIR_CTRL_UART_CTS 39 VCC_POD33 www.ti.com Debug Probes Hardware and Software Figure 14. MSP-FET USB Debugger, Schematic (2 of 5) Debug Probes Hardware and Software www.ti.com 1 B C57 + 4.7u C56 100n C63 DCDCGND C 1 G Q3 D8 1 L4 2 GND1 D 4.7u C29 DCDCGND 100n C53 R57 0.2 GND1 R25 150k VCC_DT_SENSE VCC_SUPPLY GND1 GND1 2.2u C26 DT current measurement shunt DCDCGND DCDCGND OUT 5 INA21XDCK 6 OUT U10 INA214AIDCKT NR 4 2 E 2.2u 2.2u 3 NO2 2 COM1 1 NO1 IN4 12 IN1 13 V+ 14 U20 TS3A4751PWR DCDC calibration switch C72 R56 R64 C69 COM4 10 NO4 11 5 IN2 NO3 8 COM3 9 4 COM2 DCDC_CAL1 6 IN3 TS3A4751PWR 7 GND GND1 Number 3/12/2014 R63 C73 1 DCDC_CAL0 F Rev 3/12/2014 of A 3 5 F GND1 VCC_SUPPLY 2.2u Sheet MSP-FET Rev 1.2 DCDC_CAL2 GND1 VCC_DT_BSR VCC_DT VCC_DT_REF C Size Date VCC_DT A VBUS5 2.2u DCDC_CAL0 D4 C3 Q4 3 U7 TPS73401DDCT 1 IN 2 GND GND1 3 EN GND1 1 VCC_SUPPLY S/W controlled DCDC converter DCDC MCU U4 MSP430G2452PW DVSS 14 XIN/P2.6 13 1 DVCC 2 P1.0/TA0CLK DCDC_CAL2 DCDC_TEST DCDC_RST HOST_SDA B1 E 2 DCDCGND R20 0R Energy measurement method protected under U.S. Patent Application 13/329,073 VCC_POD33 A_VCC_SUPPLY XOUT/P2.7 12 NMI-RST 10 TEST/SBWTCK 11 P1.7/SDI 9 3 P1.1/TA0.0 5 P1.3/ADC10CLK 4 P1.2/TA0.1 6 P1.4/TA0.2 DCDC_CAL1 DCDC_IO0 HOST_SCL DCDCGND C62 10n GND1 GND1 DT level shifter supply VBUS C10 1u GND1 VCC_POD33 DT current sense 10R R49 5 IN4 IN+ E 1 2 3 4 Copyright © 2015–2016, Texas Instruments Incorporated 2 S D 3 C1,C2 3 and subsequent patent applications DCDC_PULSE DCDC_IO1 P1.6/TA0.1 8 MSP430G2452PW 33p A_VCC_SUPPLY_HOST 7 P1.5/TA0.0 C66 R6 220k R7 220k C1 VCC_DCDC_REF 1n GND1 A_VCC_SUPPLY VCC_SUPPLY DCDC MCU reference voltage C28 33p 1 3 21 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback R53 R19 2 VCC_DT GND1 C24 1n 1 A1 10R R54 D C54 1n 1 R55 VCC_DT_BSR C R23 180k R24 160k VCC_SUPPLY R65 220k R15 220k 1 DCDC_RST VCC_POD33 DCDC MCU debug i/f 27k, dnp R26 C13 1n, dnp GND1 B C67 10p 2 3 4 A GND V+ REF 2 A2 C65 100n C68 1n GND1 Figure 15. MSP-FET USB Debugger, Schematic (3 of 5) A L2 33u A C B D10 B0530W-7-F + C74 VF 100u/10V GND1 VF = +5V ... 6.5V GND1 D3 Q1 C30 C BC817-16LT1 330n B GND1 E dnp DDZ9692-7 GND1 47k R29 GND1 TC_TEST_BSR VF2TDI_CTRL 47k R58 VF VCC_DT VCC_DT_TRGT IN1 VDD U6 ADG821BRMZ-REEL7 S1 S2 D2 D1 IN2 GND U9 ADG821BRMZ-REEL7 IN1 VDD S2 D2 S1 GND IN2 D1 J6 VF VF_TDI VF C VF2TEST_CTRL 47k R22 47k R59 GND1 TC_TDI_FD TC_TDI_BSR GND1 D DIR 5 VCCB 6 B 4 1 VCCA 1 VCCA DIR 5 VCCB 6 B 4 DIR 5 VCCB 6 B 4 1 VCCA 1 VCCA DIR 5 VCCB 6 B 4 DIR 5 VCCB 6 U16 SN74LVC1T45DCKR 3 A 2 GND U15 SN74LVC1T45DCKR 3 A 2 GND U14 SN74LVC1T45DCKR 3 A 2 GND U13 SN74LVC1T45DCKR 3 A 2 GND U12 SN74LVC1T45DCKR DT level shifters VCC_POD33 FPGA_IO_TCK VCC_POD33 FPGA_IO_TMS VCC_POD33 FPGA_IO_TDI VCC_POD33 FPGA_IO_TDO VCC_POD33 1 VCCA B 4 2 GND 3 A E 100n C85 100n C82 F 100n C84 VCC_DT_TRGT 100n C83 C80 1 VCCA DIR 5 VCCB 6 B 4 2 GND 3 A DIR 5 VCCB 6 U22 SN74LVC1T45DCKR 1 VCCA B 4 2 GND 3 A DIR 5 VCCB 6 U26 SN74LVC1T45DCKR 1 VCCA B 4 2 GND 3 A DIR 5 VCCB 6 U27 SN74LVC1T45DCKR 1 VCCA B 4 2 GND 3 A DIR 5 VCCB 6 U28 SN74LVC1T45DCKR 1 VCCA GND1 47k R88 GND1 47k R93 GND1 47k R96 GND1 IO6 6 IO7 7 IO8 8 TC_UART_TXD_FD TC_RST_FD TC_UART_RXD_FD TC_UART_RTS_FD B 4 2 GND 3 A 1 IO1 IO5 5 1 47k R95 47k R94 47k R87 TC_UART_RTS_FD 3/12/2014 of VCC_DT_TRGT 4 A F 5 Rev FPGA_DIR_CTRL_UART_RTS VCC_DT_TRGT VCC_DT_TRGT TC_UART_CTS_FD FPGA_DIR_CTRL_UART_CTS VCC_DT_TRGT VCC_DT_TRGT TC_UART_RXD_FD FPGA_DIR_CTRL_UART_RXD VCC_DT_TRGT VCC_DT_TRGT TC_UART_TXD_FD FPGA_DIR_CTRL_UART_TXD VCC_DT_TRGT VCC_DT_TRGT 47k, dnp R84 TC_TEST_FD FPGA_DIR_CTRL_TEST VCC_DT_TRGT 100n 100n FPGA_IO_TEST VCC_POD33 FPGA_IO_UART_TXD VCC_POD33 FPGA_IO_UART_RXD VCC_POD33 FPGA_IO_UART_CTS VCC_POD33 FPGA_IO_UART_RTS 47k 47k R101 R102 2 IO2 GND1 3 IO3 U3 TPD8E003DQDR 4 IO4 TPD8E003DQD TC_UART_CTS_FD 1 Number 3/12/2014 Sheet MSP-FET Rev 1.2 VCC_JTAGLDO_TRGT C Size Date GND1 C79 TC_TCK_FD GND1 100n TC_TEST_BSR U17 SN74LVC1T45DCKR C78 IO8 8 TC_TMS_FD VCC_POD33 100n IO7 7 E 47k R86 C77 VCC_DT_TRGT FPGA_DIR_CTRL_TCK TC_TCK_FD VCC_DT_TRGT VCC_DT_TRGT FPGA_DIR_CTRL_TMS TC_TMS_FD VCC_DT_TRGT VCC_DT_TRGT FPGA_DIR_CTRL_TDI TC_TDI_FD VCC_DT_TRGT VCC_DT_TRGT FPGA_DIR_CTRL_TDO TC_TDO_FD VCC_DT_TRGT VCC_DT_TRGT FPGA_DIR_CTRL_RST TC_RST_FD 1 IO1 IO6 6 VCC_DT_TRGT 2 IO2 47k R100 47k R97 47k R92 47k R89 47k R27 VCC_POD33 47k R31 GND1 47k R90 GND1 47k R91 GND1 47k R98 GND1 47k R99 GND1 ESD protection 3 IO3 U21 TPD8E003DQDR VCC_SUPPLY_TRGT 4 IO4 TPD8E003DQD IO5 5 TC_TDO_FD 1 TC_TDI_BSR D VCC_SENSE0_TRGT FPGA_IO_RST 1 1 Fuse blow step-up converter VBUS PWM_SETVF C D6 DNP B0530W-7-F A VCC_POD33 47k R48 VF_TEST Fuse voltage multiplexer / VCC_DT to level shifters TC_TEST_FD R13 100R 1 TDIOFF_CTRL 1 2 3 4 5 6 7 8 9 10 11 12 13 14 C 1 2 3 4 Copyright © 2015–2016, Texas Instruments Incorporated 1 1 1 1 1 1 GND1 1 1 1 1 R14 D5 2k2 dnp MMSZ5232B-7-F 1 TC_TDO_FD R41 100R R40 100R R39 100R R38 100R R37 100R R34 100R R33 100R R32 100R R35 100R Target MCU connector VCC_SUPPLY_TRGT VF_TDI TC_TDI_BSR TC_TMS_FD VCC_SENSE0_TRGT VCC_JTAGLDO_TRGT TC_TCK_FD TC_TEST_BSR VF_TEST TC_RST_FD TC_UART_CTS_FD TC_UART_RTS_FD TC_UART_TXD_FD B VCC_DT2TRGT_CTRL R42 1k TC_UART_RXD_FD R43 100R 1 1 2 3 4 A 9 GND SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback MSP Debuggers 22 9 GND www.ti.com Debug Probes Hardware and Software Figure 16. MSP-FET USB Debugger, Schematic (4 of 5) Debug Probes Hardware and Software www.ti.com 1 2 3 4 VBUS A 10n C25 3 EN2 2 IN 1 EN1 GND 4 OUT2 5 OUT1 6 U19 TLV7111533D MSP-FET power supply 1u C3 33p B 1u C59 PWRGND U18 1u C61 PWRGND 1 GND1 47k R16 VCC_POD15 R36 150k R12 270k VF VCC_SUPPLY_TRGT A_VBUS5 GND1 VCC_DT VCC_POD33 GND 6 IN2 7 COM1 8 NO2 5 33p C27 TS5A21366RSE 4 COM2 3 IN1 2 V+ 1 NO1 TS5A21366RSER PWRGND VBUS5 R51 240k A_VCC_SENSE0_TRGT R52 150k 1 B 1 A_VF C R79 150k R78 150k VCC_DT VCC_DT2SUPPLY_CTRL C4 33p C 1 C32 33p R9 150k VCC_DT_BSR A_VCC_DT R18 150k 1 C2 33p D D TP9 TP3 TP2 TP1 TP0 DCDC_IO0 DCDC_PULSE GND1 VBUS VCC_SUPPLY Test points A_VCC_DT_BSR E E TP4 TP5 TP6 TP7 TP8 C Size Date FPGA_TP0 FPGA_TP1 FPGA_TP2 GND1 DCDC_IO1 J2 1 2 3 4 5 6 7 8 1 2 3 4 5 6 7 8 HEADER_1X8_50MIL_A J3 J4 HEADER_1X8_50MIL_A 1 2 3 4 5 6 7 8 HEADER_1X8_50MIL_A TP11 F VBUS HOST_TEST HOST_TDO HOST_TDI HOST_TMS HOST_TCK HOST_RST VCC_DT GND1 A_VCC_SUPPLY_HOST DCDC_RST DCDC_TEST VCC_POD33 VCC_POD15 of GND1 3/12/2014 A 5 5 F FPGA_TRST FPGA_TCK FPGA_TMS FPGA_TDI FPGA_TDO HOST_SCL HOST_SDA VBUS5 MSP-FET Rev 1.2 1 Rev Common debug and test i/f Number 3/12/2014 Sheet 1 2 3 4 Copyright © 2015–2016, Texas Instruments Incorporated 23 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback C58 PWRGND PWRGND VCC_SUPPLY_TRGT VBUS VCC_SUPPLY Target power switch VCC_SUPPLY2TRGT_CTRL 47k R21 GND1 1 Analog inputs to Host MCU R11 150k R10 150k VCC_SENSE0_TRGT A R80R Figure 17. MSP-FET USB Debugger, Schematic (5 of 5) Debug Probes Hardware and Software www.ti.com Figure 18. MSP-FET USB Debugger, PCB (Top) 24 MSP Debuggers Figure 19. MSP-FET USB Debugger, PCB (Bottom) SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Debug Probes Hardware and Software www.ti.com 5.7 MSP-FET430UIF Stand-Alone Debugger The MSP-FET430UIF is a powerful debug probe for application development on MSP430 microcontrollers. This is a legacy debugger being replaced by MSP-FET. The MSP-FET430UIF provides a USB interface to program and debug the MSP430 devices in-system through the JTAG interface or the pin-saving Spy-Bi-Wire (2-wire JTAG) protocol. The MSP-FET430UIF development tool supports development with all MSP430 devices and is designed for use with PCBs that contain MSP430 devices; for example, the MSP430 target socket boards. Two different version of the MSP-FET430UIF are available, version 1.3 and version 1.4a. There are limitations when using version 1.3. Refer to Section 5.7.1 for more details. Figure 20. MSP-FET430UIF Version 1.4a Top and Bottom Views 5.7.1 Figure 21. MSP-FET430UIF Version 1.3 Top and Bottom Views General Features The following features are provided by the MSP-FET430UIF debug probe. Features: • Operating systems: OS X, Linux, Windows NOTE: OS X El Capitan is not supported using the MSP-FET430UIF. • • • • • • • • Software configurable supply voltage between 1.8 V and 3.6 V at 100 mA External voltage detection Supports JTAG Security Fuse blow to protect code Supports all MSP430 boards with JTAG header Supports both JTAG and Spy-Bi-Wire (2-wire JTAG) debug protocols Software breakpoints in Flash, FRAM, and RAM support Flash and FRAM programming support Software field update is possible (enable new device support by in field firmware updates) NOTE: The MSP-FET430UIF version 1.3 does not support Spy-Bi-Wire connection for MSP430 devices with 1-µF capacitance on the reset line. SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 25 Debug Probes Hardware and Software 5.7.2 www.ti.com LED Signals The MSP-FET430UIF shows its operating states using two LEDs, one green and one red. Table 7 lists all available operation modes. An or icon indicates that the LED is off, an or icon indicates that the LED is on, and an or icon indicates that the LED flashes. Table 7. MSP-FET430UIF LED Signals Power LED Mode LED Function MSP-FET430UIF not connected to PC, or MSP-FET430UIF not ready; for example, after a major firmware update. Connect or reconnect MSP-FET430UIF to PC. MSP-FET430UIF connected and ready MSP-FET430UIF waiting for data transfer Ongoing data transfer – during active debug session An error has occurred; for example, target VCC over current. Unplug MSP-FET430UIF from target, and cycle the power off and on. Check target connection, and reconnect MSP-FET430UIF. Firmware update in progress. Do not disconnect MSP-FET430UIF while both LEDs are blinking. 5.7.3 Hardware This section includes MSP-FET430UIF hardware descriptions like the JTAG connector, schematic, and power up states of the JTAG pins. 5.7.3.1 JTAG Target Connector Figure 22 shows the pinout of the MSP-FET430UIF JTAG connector. Figure 22. MSP-FET430UIF 14-Pin JTAG Connector 26 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Debug Probes Hardware and Software www.ti.com 5.7.3.2 Pin States After Power Up Table 8 describes the electrical state of every JTAG pin after debug probe power up. Table 8. MSP-FET430UIF Pin States Pin Name After Power-Up When JTAG Protocol is Active When Spy-Bi-Wire Protocol is Active Hi-Z, pulled up to 3.3 V In, TDO In and Out, SBWTDIO 1 TDO/TDI 2 VCC_TOOL 3.3 V Target VCC Target VCC 3 TDI/VPP Hi-Z, pulled up to 3.3 V Out, TDI Hi-Z, pulled up to VCC 4 VCC_TARGET In, external VCC sense In, external VCC sense In, external VCC sense 5 TMS Hi-Z, pulled up to 3.3 V Out, TMS Hi-Z, pulled up to VCC 6 N/C N/C N/C N/C 7 TCK Hi-Z, pulled up to 3.3 V Out, TCK Out, SBWTCK 8 TEST/VPP Out, Ground Out, TEST Hi-Z, pulled up to VCC Ground 9 GND Ground Ground 10 N/C N/C N/C N/C 11 RST Out, VCC Out, RST Ground 12 N/C N/C N/C N/C 13 N/C N/C N/C N/C 14 N/C N/C N/C N/C SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 27 Debug Probes Hardware and Software 5.7.3.3 www.ti.com Schematics Figure 23. MSP-FET430UIF USB Interface, Schematic (1 of 4) 28 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Debug Probes Hardware and Software www.ti.com Figure 24. MSP-FET430UIF USB Interface, Schematic (2 of 4) SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 29 Debug Probes Hardware and Software www.ti.com Figure 25. MSP-FET430UIF USB Interface, Schematic (3 of 4) 30 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Debug Probes Hardware and Software www.ti.com Figure 26. MSP-FET430UIF USB Interface, Schematic (4 of 4) SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 31 Debug Probes Hardware and Software www.ti.com Figure 27. MSP-FET430UIF USB Interface, PCB 32 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Debug Probes Hardware and Software www.ti.com 5.8 eZ-FET and eZ-FET Lite Onboard Emulation The eZ-FET and eZ-FET Lite are powerful onboard flash emulation debug probes for application development on MSP430 microcontrollers (see Figure 28). The eZ-FET and eZ-FET Lite onboard emulation are the successors of the legacy eZ430. Both eZ-FETs provide a USB interface to program and debug the MSP430 devices in-system through the pin-saving Spy-Bi-Wire (2-wire JTAG) protocol. Furthermore, the USB interface can be used for backchannel UART communication. Both development tools support development with all MSP430 devices. They are designed as onboard emulation that is available on several LaunchPad kits. (Only MSP430 devices that implement the SBW2 protocol are supported.) Figure 28. eZ-FET and eZ-FET Lite (Top View) Figure 29 shows revision 1.3 of the eZ-FET. Figure 29. eZ-FET Rev1.3 (Top View) SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 33 Debug Probes Hardware and Software 5.8.1 www.ti.com General Features The following features are provided by the eZ-FET and eZ-FET Lite debug probes. Features: • eZ-FET and eZ-FET Lite supported since: – CCS v5.4.0 – IAR EW430 v5.52.1 and v5.51.6 • Operating systems: OS X, Linux, Windows • Fixed supply voltage between 3.3 or 3.6 V at 75 mA • Support Spy-Bi-Wire (2-wire JTAG) debug protocol • Software Breakpoint in Flash, FRAM, and RAM support • Flash and FRAM programming support • Backchannel UART • eZ-FET only – EnergyTrace and EnergyTrace++ support • Software field update is possible 5.8.2 Backchannel UART Supported baud rates depend on the target configuration and the debug settings. Table 9 shows which baud rates are supported with certain configuration combinations. ✓ means that the corresponding baud rate is supported without any data loss with the specified combination of settings. ✗ means that the corresponding baud rate is not supported (data loss is expected) with the specified combination of settings. Table 9. eZ-FET and eZ-FET Lite Backchannel UART Implementation Target MCLK Frequency: 1 MHz 8 MHz Debugger: 5.8.2.1 1 MHz 8 MHz Active Inactive Flow Control: No Yes No Yes No Yes No Yes 4800 baud ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ 9600 baud ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ 19200 baud ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ 28800 baud ✗ ✓ ✓ ✓ ✓ ✓ ✓ ✓ 38400 baud ✗ ✓ ✗ ✓ ✗ ✓ ✗ ✓ 57600 baud ✗ ✓ ✗ ✓ ✗ ✓ ✗ ✓ 115200 baud ✗ ✗ ✗ ✓ ✗ ✗ ✗ ✓ eZ-FET and eZ-FET Lite UART Backchannel Activation Commands The eZ-FET supports two different backchannel UART modes, one with flow control and one without. The different modes can be selected by opening the corresponding COM port with a dedicated baud rate. See Table 10 for the specific baud rates for each command. NOTE: The baud rates used by these commands cannot be used for communication. If none of the specified commands are transferred before setting the communication baud rate, communication starts with these default settings: VCC on, no flow control mechanism. 34 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Debug Probes Hardware and Software www.ti.com Table 10. eZ-FET and eZ-FET Lite Backchannel UART Activation Commands Baud Rate 5.8.3 Command 9620 Set all backchannel UART pins to high impedance – no current flow into target device 9621 Configure backchannel UART communication without handshake (default start behavior) 9622 Configure backchannel UART communication with handshake NOTE: Available on Rev. 1.2 only. 9623 Voltage configuration command. When this command is received, target VCC switched on. LED Signals eZ-FET emulators show their operating states using two LEDs, one green and one red. Table 11 lists all available operation modes. An or icon indicates that the LED is off, an or icon indicates that the LED is on, and an or icon indicates that the LED flashes. Table 11. eZ-FET LED Signals Power LED Mode LED Function eZ-FET not connected to PC, or eZ-FET not ready; for example, after a major firmware update. Connect or reconnect eZ-FET to PC. eZ-FET connected and ready eZ-FET waiting for data transfer Ongoing data transfer – during active debug session An error has occurred; for example, target VCC over current. Unplug eZ-FET from target, and cycle the power off and on. Check target connection, and reconnect eZ-FET. Firmware update in progress. Do not disconnect eZ-FET while both LEDs are blinking. 5.8.4 Hardware This section describes the pinout of the eZ-FET and eZ-FET Lite debug connector. It includes a list of all debugger pin states after power up and the eZ-FET and eZ-FET Lite schematics. 5.8.4.1 JTAG Target Connector Figure 30 shows the pinout of the eZ-FET debug connector. Figure 30. eZ-FET or eZ-FET Lite Debug Connector SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 35 Debug Probes Hardware and Software 5.8.4.2 www.ti.com Connecting MSP-FET to LaunchPad Figure 31 and Figure 32 show how to connect an MSP-FET to the target MSP430 device that is solders onto the LaunchPad, using an F5529 LaunchPad as an example. Figure 31. MSP-FET to LaunchPad Pin Assignments 5.8.4.3 Figure 32. MSP-FET to LaunchPad Wiring Diagram Pin States After Power Up Table 12 describes the electrical state of every JTAG pin after debug probe power up. Table 12. eZ-FET and eZ-FET Lite Pin States 36 Signal Name After Power-Up When Spy-Bi-Wire Protocol is Active SBWTDIO Hi-Z, pulled up to 3.3 V In and Out, SBWTDIO SBWTCK Hi-Z, pulled up to 3.3 V Out, SBWTCK TXD Hi-Z, pulled up to 3.3 V In, Target UART TXD output RXD Hi-Z, pulled up to 3.3 V Out, Target UART RXD input CTS Hi-Z, pulled up to 3.3 V Out, Target UART Clear-To- Send Handshake input RTS Hi-Z, pulled up to 3.3 V In, Target UART Ready-to Send Handshake output 3V3 Target VCC Target VCC 5V USB VCC USB VCC GND Ground Ground MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Debug Probes Hardware and Software www.ti.com 5.8.4.4 Schematics Figure 33. eZ-FET Schematic (USB Connection) SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 37 Debug Probes Hardware and Software www.ti.com Figure 34. eZ-FET Schematic (Emulation MCU) 38 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Debug Probes Hardware and Software www.ti.com Figure 35. eZ-FET Schematic DCDC (No eZ-FET Lite) SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 39 Debug Probes Hardware and Software 5.9 www.ti.com eZ430 Onboard Emulation The eZ430 onboard emulation is the legacy onboard flash emulation for application development on MSP430 microcontrollers. The eZ-FET and eZ-FET Lite onboard emulation are the successors of the legacy eZ430. The eZ430 provides a USB interface to program and debug the MSP430 devices in-system through the pin-saving Spy-Bi-Wire (2-wire JTAG) protocol. Furthermore, the USB interface can be used for Backchannel UART communication. NOTE: The eZ430 does not support all MSP430 device families. Refer to Table 1 for more details about device support. Figure 36. eZ430 Emulation 5.9.1 General Features USB debug interface to connect a MSP430 MCU to a PC for real-time in-system programming and debugging. Features: • Operating systems: Windows • Fixed supply voltage between 3.6 V at 75 mA • Support Spy-Bi-Wire (2-wire JTAG) debug protocol • Software Breakpoint in Flash, FRAM, and RAM support • Flash and FRAM programming support • Backchannel UART • Software field update is not possible (refer to Table 1 for device support details) • Limited device support 40 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Debug Probes Hardware and Software www.ti.com 5.9.2 Backchannel UART The baud rates that are supported depend on the target configuration and the debug settings. Table 13 shows which baud rates are supported with certain configuration combinations. ✓ means that the corresponding baud rate is supported without any data loss with the specified combination of settings. ✗ means that the corresponding baud rate is not supported (data loss is expected) with the specified combination of settings. Table 13. eZ430 Backchannel UART Implementation 5.9.3 Target MCLK Frequency: 1 MHz 8 MHz Debugger: Active Active 4800 baud ✓ ✓ 9600 baud ✓ ✓ 19200 baud ✗ ✗ 28800 baud ✗ ✗ 38400 baud ✗ ✗ 57200 baud ✗ ✗ 115200 baud ✗ ✗ Hardware This section describes the pinout of the eZ430 debug connector. It includes a list of all debugger pin states after power up and the ez430 schematics. 5.9.3.1 JTAG Target Connector Figure 37 shows the pinout of the eZ430 debug connector. Figure 37. eZ430 Debug Connector on MSP-EXP430G2 LaunchPad 5.9.3.2 Pin States After Power Up Table 14 describes the electrical state of every JTAG pin after debug probe power up. Table 14. eZ430 Pin States Signal Name After Power-Up When Spy-Bi-Wire Protocol is Active VCC Target VCC Target VCC RST In and Out, SBWTDIO In and Out, SBWTDIO TST Out, SBWTCK Out, SBWTCK TXD In, Target UART TXD output In, Target UART TXD output RXD Out, Target UART RXD input Out, Target UART RXD input SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 41 Debug Probes Hardware and Software 5.9.3.3 www.ti.com Schematics Figure 38. eZ430 Schematic (Emulation MCU) 42 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Debug Probes Hardware and Software www.ti.com Figure 39. eZ430 Schematic (USB Connection) SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 43 Debug Probes Hardware and Software www.ti.com 5.10 MSP-FET430PIF The MSP-FET430PIF is a parallel port interface that is used to program and debug MSP430 boards through the JTAG interface. This interface uses a parallel PC port to communicate with the IDE (CCS, EW430, or the MSP Flasher) running on the PC. The interface uses the standard 14-pin JTAG header to communicate with the MSP430 device using the standard JTAG protocol. The flash memory can be erased and programmed in seconds with only a few keystrokes, and because the MSP430 flash is extremely low power, no external power supply is required. The tool has an integrated software environment and connects directly to the PC which greatly simplifies the setup and use of the tool. Figure 40. MSP-FET430PIF 5.10.1 • • • • • General Features Operating systems: Windows XP Fixed supply voltage between 3.3 V at 25 mA Software Breakpoint in Flash, FRAM, and RAM support Flash and FRAM programming support Supports JTAG protocol only (1) NOTE: (1) 44 The MSP-FET430PIF is for legacy device support only. This emulation tool does not support any devices released after 2011. Spy-Bi-Wire (2-wire JTAG) is supported MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Debug Probes Hardware and Software www.ti.com 5.10.2 Schematics Figure 41. MSP-FET430PIF FET Interface Module, Schematic SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated MSP Debuggers 45 Debug Probes Hardware and Software www.ti.com Figure 42. MSP-FET430PIF FET Interface Module, PCB 46 MSP Debuggers SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Revision History www.ti.com Revision History Changes from November 3, 2015 to February 17, 2016 ................................................................................................. Page • • • • • • • • • Added row "Supports MSP432Pxx" in Table 1, Debug Probes Features and Device Compatibility ........................... 4 Removed versions numbers from Ubuntu and OS X in Section 4.4, Hardware Installation Using the MSP Flasher ........ 9 Added list item "MSP-FET is supported since" in Section 5.6.1, General Features ............................................ 15 Changed "57200 baud" to "57600 baud" in Table 2, MSP-FET Backchannel UART Implementation ....................... 15 Added note "OS X El Capitan is not supported using the MSP-FET430UIF" in Section 5.7.1, General Features ......... 25 Added Figure 29, eZ-FET Rev1.3 (Top View) ....................................................................................... 33 Added list item "eZ-FET and eZ-FET Lite supported since" in Section 5.8.1, General Features ............................. 34 Changed "57200 baud" to "57600 baud" in Table 9, eZ-FET and eZ-FET Lite Backchannel UART Implementation ...... 34 Added note to Baud Rate 9622 in Table 10, eZ-FET and eZ-FET Lite Backchannel UART Activation Commands ....... 35 NOTE: Page numbers for previous revisions may differ from page numbers in the current version. SLAU647C – July 2015 – Revised February 2016 Submit Documentation Feedback Copyright © 2015–2016, Texas Instruments Incorporated Revision History 47 IMPORTANT NOTICE Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as “components”) are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI’s terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed. TI assumes no liability for applications assistance or the design of Buyers’ products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers’ products and applications, Buyers should provide adequate design and operating safeguards. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI. Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions. Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications. In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI’s goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms. No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use. Only those TI components which TI has specifically designated as military grade or “enhanced plastic” are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have not been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949. Products Applications Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Amplifiers amplifier.ti.com Communications and Telecom www.ti.com/communications Data Converters dataconverter.ti.com Computers and Peripherals www.ti.com/computers DLP® Products www.dlp.com Consumer Electronics www.ti.com/consumer-apps DSP dsp.ti.com Energy and Lighting www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical Logic logic.ti.com Security www.ti.com/security Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video RFID www.ti-rfid.com OMAP Applications Processors www.ti.com/omap TI E2E Community e2e.ti.com Wireless Connectivity www.ti.com/wirelessconnectivity Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated