DAC -888 - Analog Devices

advertisement

DAC - 888

[PMI)

precision

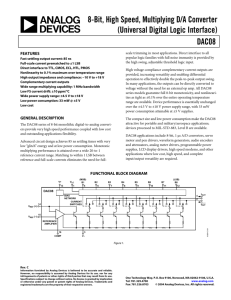

BYTEDACJo)X-BIT HIGH-SPEED "MICROPROCESSOR COMPATIBLE"

MULTI PLYING OJA CONVERTER

Monolithics

Inc.

FEATURES

latches may also be operated

.

.

8-BIt

holding both control pins low.Additionally,the DAC-888 has

a data hold time requirement of zero nanoseconds.

The Analogsection consists of a "Field-Proven" DAC-0801A

.

CE and WR Inputs

.

.

.

.

.

LevelTriggered Latch

8-BIt J-LPCompatible

Easily Interfaced to All 8-BIt Processors

TTL Logic Compatible

High Output Impedance and Compliance

Proven DAC-O8Analog Flexibility and Reliability

Nonlinearity to :!:O.1%Max

. Low Power Dissipation .....................

Available In Die Form

.

OBS

DAC-888 applications include graphic display drivers, highspeed modems, AID converters, programmable waveform

generators and power supplies, analog meter drivers, audio

encoders and programmable attenuators; and other applications where low cost, high speed and buffered flexibility are

required.

134mW

PACKAGE

.

t

For devices

number.

Burn-in

CerDIP,

1990/91

OLE

INDUSTRIAL

TEMPERATURE

PIN CONNECTIONS

DAC888EX

DAC888FX

0.1

0.19

processed

in total compliance

to MIL-STD-883,

TE

add /883 after part

Consult factory for 883 data sheet.

is available on commercial and industrial temperature range parts in

plastic DIP, and TO-can packages. For ordering information, see

Data Book, Section 2.

GENERAL

DESCRIPTION

mode by

Converter. Monotonic multiplying performance is attained

over a wide 20 to 1 reference current range. Matching to

within 1 LSB between reference and full-scale currents

eliminates full-scale adjustment in most applications.

ORDERINGINFORMATION t

NL

%F5

in a transparent

The BYTEDAC@ DAC-888 is a buffered 8-bit digital-toanalog converter designed specifically for 8-bit bus oriented

systems. The data inputs are connected to level-triggered

latches. Two active-low control pins are provided for ease of

interface to virtually all available microprocessors. The

18-PIN HERMETIC

DUAL-IN-LiNE

PACKAGE

(X-Suffix)

FUNCTIONAL DIAGRAM

DB]

MSB 0

CE

DB6

0

DBS DB4

0

0

DBJ

0

DB2

0

DB1

0

DBO

0 LSB

I

Cf'J

~

u.J

r~

u.J

>

Z

0

u

C)

0

,J

<:(

Z

<:(

I

0

r-I

,J

17

CONTROL

LOGIC

a-BIT

LATCH

16

WR

14

10

'OUT

VREF(+)

a-BIT

VREF(-I

MULTIPL YING DAC

11

13

'OUT

12

V-

COMP

ilanufactured

under

one or more

of the following

patents

-

4.055.773.

-

-

- -

4,056,740.

-

GND

~C)

0

V+

4.092.639

..1...1.,..iO,1

-

--'..1.0.00

~

- - ---""'-- -

IPM!)

DAC-888 BYTEDAC'" 8-BIT HIGH-SPEED "MICROPROCESSOR COMPATIBLE" MUL TIPL YING D/A CONVERTER

ABSOLUTE MAXIMUM RATINGS

OperatingTemperatureRange

-25°C to +85°C

Junction Temperature (TJ)

Storage Temperature

Lead Temperature (Soldering, 60 sec)

V+ Supply to V- Supply

Logic Inputs

Analog Current Outputs

Reference Inputs (V10 to V11)

-65°C to + 150°C

-65°C to + 150°C

300°C

18.1V

OV to 5.5V

-5mA

V- to V+

Reference Input Differential Voltage

(V10to V11)

Reference Input Current

PACKAGE TYPE

:t15V

5mA

elA (Note 2)

79

18.Pin Hermetic DIP (X)

UNITS

elC

11

°CIW

NOTES:

1. Absolute ratings apply to both DICE and packaged parts. unless otherwise

noted.

2. aA is specified for worst case mounting conditions, i.e., a'A is specified for

dkvice in socketforCerDIPpackage.

J

ELECTRICAL CHARACTERISTICS at V+ = +5V, V- = -12V, IREF= 2mA, unless otherwise noted. TA= +25°C to +85°C apply for

DAC-888E/F. Output characteristics refer to both lOUTand lour

OBS

SYMBOL

PARAMETER

MIN

CONDITIONS

Resolution

-------

Monotonlclty

NL

Nonlinearity

Full.Scale

Tempco

-------,See note.

TCIFS

Output Voltage

Compliance

VOG

Output Impedance

ROUT

Full Range Current

'FA

Current

Change"-

1/2 LSB

Rl1'

R1O~

Full Range

Symmetry

Zero-Scale

IFRS

Current

8

'FSR

Reference

Current

'B

Bias

Supply

Sensitivity

-

:!:0.1

2.10

:!.50

5

1.94

-

1.99

204

:!:8

0.2

'REF

2.1

= 3mA

PSSI FR'

V-+ ~ 4.5V to 5.5V

PSSIFR

V-

= -1O.8V

to --13.2V

2

2.9

UNITS

Bits

%FS

:!.019

. 80

5

+5

>20

MAX

Bits

.-------------,10

.---------.------

-

:!.1

IFR13

-

8

8

IzS

Output Current

Range

Power

'FRI4

8

---

5.000k!!

TA~25°C

TYP

MIN

OLE

Full-Scale

VREF o. 10.000V

DAC-888F

DAC-888E

TYP

MAX

ppmr

,5

--

C

V

-------------

TE

>20

_n-

1.94

MH

1.99

2.04

mA

:':1

:c8

p.A

2

p.A

---

0.2

2.1

2.9

- 1

-1

-3

-

:!.0.0003

:!.001

-

-

:!.0.0002

:!:0.01

-

mA

-3

p.A

2. 0.0003

:c0.01

%':;IFS/%':;V+

:!:0.0002

:!:001

%':;1FS/%':;V-

'REF ~ 1mA

Power Supply

Current

1+

1--

'REF = 2mA

Power Dissipation

Pd

'REF

Input Levels

Logic Input "a"

= 2mA

12

6

16

9

134

190

----

12

6

16

134

190

.-------.----------

9

mA

mW

Logic

Logic

Input

"1"

08

0.8

V'L

___n,--u

V'H ""

n_--

--

2

n--

n

2

----------.---------------..--------

V

Logic Input Current

Logic

Input

"a"

',L

Logic

Input

'1

"H

NOTE: Guaranteed

- ------

V,N

OV

V,N

5.25V

2

01

10

1

2

01

10

1

p.A

by design.

11-102

7/89,

Rev. B

[pMI)

DAC-888 BYTEDAC'" 8-BIT HIGH-SPEED "MICROPROCESSOR

ELECTRICAL

CHARACTERISTICS

-

A.C. PARAMETERS

Vs

COMPATIBLE" MUl TIPl YING D/A CONVERTER

= +5V, -12V, IREF= 2mA, TA= 25°C.

DAC-888E

MIN

TYP

MAX

300

400

MIN

DAC-888F

TYP MAX

UNITS

PARAMETER

SYMBOL

CONDITIONS

Settling Time

ts

From CE & WR Negative Level

to :!:1/2LSB, All Bits Switched

ON or OFF, ISee notel

Reference Input

Slew Rate

dl/dt

(See Note)

4

Data Input Setup Time

tDS

ISee note)

150

-150

ns

Data Input Hold Time

tDH

ISee note)

10

(See note)

- 10

250

ns

250

Chip Enable/Write Pulse Width

tENW

300

8

4

400

ns

8

mAIlls

ns

NOTE: Guaranteed by design.

OBS

DAC-888

PIN DESCRIPTION

SYMBOL

DESCRIPTION

DBa - DB7

DATA BIT -

CE

PINS 1-8

OLE

Bits 0-7 are digital, active-high inputs. DB7 is assigned as the MSB.

PIN 17

CHIP ENABLE - An active low input control which is the device enable input terminal.

WR

'OUT

.~

VREF+'

VREF-

COMP

PIN 16

WRITE CONTROL - An active low control which enables the microprocessor to write data to the DAC.

CURRENT

VOLTAGE

OUTPUT

-

Complementary

REFERENCE

COMPENSATION

-

-

current

Differential

The reference

inputs

amplifier

outputs,

that accept

frequency

which

when added,

a negative,

equal

positive,

compensating

'FS'

or bipolar

input

TE

'DB7

DB6 DB5 DB4+ DBJ

terminal.

DATA

INPUT

DB2 DB1 DBa'

PINS 10-11

and are used to set IFS'

FUNCTIONAL DIAGRAM AND TIMING DIAGRAM FOR 8-BIT OPERATION

TO B.BIT DATA BUS

PINS 13-14

/w~

PIN 12

DATA VALID~

tDH:J

17

I

WR. CE

CE

CONTROL

16

'ENW

& LATCHES

WR

-=

+5.000V

2.500kH

10

VREF+

'OUT

14

lOUT

DAC

11

2.5kH

VREFCOMP

V-

GND

lOUT

V+

'/~~

lOUT

-=

12

15

O.Ol"F

-=

~

'S

lOUT

9

1B

NOTE: IF INPUT DATA CHANGES

HIGH -IDSI,IOUT/IOUT

CEO)LOW AND BEFORE

THE LAST DATA BEFORE

i(WR'

(WR'

CE)

CEO)HIGH

- 'DS! WILL BE LATCHED PROVIDED DATAVALIDIS HELD FOR (IDS (MIN)

-=

-12V

AFTER (WR.

WILL CHANGE.

tDH

(MIN))'

+5V

I

en

~

~

~

~

>

Z

0

u

c.J

0

-J

~

Z

~

OPERATION TABLE

CE

WR

I

X

NO CHANGE

I

-J

~

NO CHANGE

0

0

0

f-<

OUTPUT

0

f>--<

UPDATE lATCHES----.---ITRANSPARENT)

--~

~

0

11-103

7/89,

Rev. B

IPMI)

DAC-888 BYTEDAC~ 8-BIT HIGH-SPEED "MICROPROCESSOR COMPATIBLE" MULTIPLYING D/A CONVERTER

DICE CHARACTERISTICS

1.

2.

3.

4.

5.

6.

7.

8.

9.

DB7 (MSB)

DB6

DB5

DB4

DB3

DB2

DB1

DBO (LSB)

GROUND

10.

11.

12.

13.

14.

15.

16.

17.

18.

VREF (+)

VREFt-)

COMP

lOUT

lOUT

VWR

CE

V+

For additional DICE ordering information,

refer to 1990/91 Data Book, Section

DIE SIZE 0.141 X 0.127 inch, 17,907 sq. mils

(3.58 X 3.23 mm, 11.56 sq. mm)

OBS

2.

WAFER TEST LIMITS at Vs = +5, -12V, 'REF= 2mA, TA= 25° C, unless otherwise noted. Output characteristics refer to both

lOUTand lOUT

SYMBOL

PARAMETER

Resolution

Monotonicity

Nonlinearity

Full-Scale

Output

Voltage

Change

VOG

Compliance

DAC-888N

DAC-888G

LIMIT

CONDITIONS

LIMIT

OLE

8

Current

+5

5

Typ.

VREF= 10.000V

Current

IFR14

Full Range

Symmetry

I FRS

Zero-Scale

Current

Izs

Output

Current

Reference

Power

Range

Supply

V-=-10.8Vto~132V,

1-

Current

Dissipation

Logic

V+ = 4.5V to 5.5V

PSSI FR

Input

IREF= 1mA

Pd

VMAX

-5

V MIN

204

mA MAX

mA MIN

}J.A MAX

2

}J.A MAX

2.1

mA MIN

3

3

}J.A MAX

:!::0.01

:!::0.01

%.J.I Fs/%.J. V + MAX

:to.01

--

,,:0.01

%.J./FS/%.J.V-' MAX

21

PSSI FR,

TE

+5

:!::8

2

IREF = 3mA

Bits MIN

%FS MAX

:to.19

1.94

:!::8

1+

Supply

Power

1.94

16

Sensitivity

Power

204

IFR14-IFR13

I FSR

Bias Current

R 11' R 10= 5.000k!!

TA = 25°C

Bits MIN

8

:to.1

ROUT> 20M!!

Full Range

8

8

< 1/2 LSB

UNITS

16

16

IREF = 2mA

9

9

I REF= 2mA

190

190

mW MAX

mA MAX

Levels

Logic

Input

"0"

V,L

0.8

0.8

V MAX

Logic

Input

"1"

V'H

2

2

V MIN

- 10

10

Logic

Input

Current

I'L

V,N = OV

I'H

V'N = 5.25V

1

}J.AMAX

1

----...-

NOTE:

Electrical

tests

guaranteed

are performed

for standard

at wafer

product

dice.

probe

Consult

to the limits

factory

shown.

Due to variations

to negotiate

TYPICAL ELECTRICAL CHARACTERISTICS

specifications

in assembly

methods

and normal

based on dice lot qualification

V+ = +5V, -12V,

yield

through

loss, yield

sample

after

lot assembly

'REF = 2mA, TA = 25°C, unless otherwise

packaging

is not

and testing.

noted.

DAC-888

SYMBOL

PARAMETER

Reference

Settling

Input

CONDITIONS

dlldt

Slew Rate

From CE Negative

Time

IS

All bits Switched

-Data

------

Input

Setup

Time

Data

Input ---------------------Hold Time

Chip

Enable

Write

~

TYPICAL

Edge to :t 1/2 LSB,

ON or OFF

tos

-------------

toH

.

-

mA/}J.s

300

ns

100

ns

0

ns

200

tENW

Pulse Width

~-

- -~

UNITS

8.0

ns

-....--.-.-------------------.------------------

11-104

--~

7/89, Rev. B

!>

DAC-888 BYTEDAC~ 8-BIT HIGH-SPEED "MICROPROCESSOR COMPATIBLE" MULTIPLYING D/A CONVERTER

or may vary from nearly 0 to +4.0mA. The full range output

currrent is a linear function of the reference current and is

ilTAllNFORMATION

BYTEOAClI" OAC-888 is a monolithic microprocessor

Ipatible Of A converter

consisting

of an 8-bit level

Jered latch, control circuitry and one 8-bit multiplying

converter housed in an 18-pin dual in line package (01 P I.

given by:

255

IFR = 256 X IREF where IREF = 110

OAC-888 accepts 8-bit binary bytes at the data inputs.

il access is accomplished

when WR and CE are low.

ing the low state of CE and WR, the latches are transmt, therefore, data should be valid from 100ns prior to WR

CE low until CE or WR high. When CE or WR goes high,

data stored in the latches will hold the selected output

!finitely.

In positive reference applications,

an external positive reference voltage current flows through R1Qinto the VREF(+I terminal of the reference amplifier.

Alternatively,

a negative

reference may be applied to VREFI-j; reference current flows

from ground through R1Qinto VREF(+) as in the positive reference case. This negative

reference

connection

has the

advantage of a very high impedance presented at pin 11. The

voltage at pin 10 is equal to and tracks the voltage at pin 11

AlOG INFORMATION

due to the high gain of the internal reference amplifier. R11

(nominally equal to R1Q) is usedto cancel biascurrent errors;

OBS

;IC POSITIVE REFERENCE OPERATION

R" may be eliminated

MSB

LSB

DB] DB6 DB5 DB4 DBJ DB2 DBl DBO

1]

CE

CONTROL

16

& LATCHES

WR

RREF

5.000Vo-vvv

REF

Rl0

14-

10

VREF+

lOUT

IREF11

VREFCaMP

GND

V15

12

R11

1J~

lOUT

V+

'OUT

18

0.1"F

1

OLE

Tn

OPERATION

16

+VREF

TYPICAL

IFR

=

RREF

CONTROL

& LATCHES

WR

RREF

255

14

x 256

lOUT

IVREF+

DAC

-

R11 11

. -VREF

x 255

-VREF

AMPLIFIER

'V\I\,

R10 101

.L

lOUT + lOUr = 'FR

FOR ALL LOGIC STATES

IREF = 2.5000k

111' RREF

FERENCE

TE

MSB

LSB

DB] DB6 DB5 DB4 DBJ DB2 DB1 DBO

-=-

DR FIXED REFERENCE.

IALUES ARE:

in error.

BASIC NEGATIVE REFERENCE OPERATION

4=t

~

O.Ol"F 0.1~

-=-

increase

For most applications

the tight relationship

between IREFand

IFR will eliminate

the need for trimming

IREF. If required,

full-scale

trimming

may be accomplished

by adjusting

the

value of R 1Qor by using a potentiometer

for R1Q.An improved

method

of full-scale

trimming

which eliminates

potentio-

'OUT

DAC

with only a minor

SET-UP

'FR

DAC-888 is a multiplying D/A converter in which the

put current is the product of a digital number and the

!

1J

-

'OUT

RREF

256

NOTE: RREF SETS IFS: R11 IS FOR BIAS CURRENT CANCELLATION

AND IS EQUAL TO RREF'

.rJ'J

~

~

ut reference current. The reference current may be fixed

SIC UNIPOLAR

NEGATIVE

OPERATION

MSB

DB] DB6 DB5 DB4 DBJ

LSB

DB2 DB1 DBo

~

~

>

Z

0u

lamA

Eo

Eo

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1.992

1.984

0.000

0.008

-4.980

-4.960

0.000

-0.020

1

1

0

0

0

1

0

0

1

0

0

1

0

0

1

0

0

1

0

0

1

1

0

1

1008

1.000

0.992

0.984

0.992

1.000

-2.520

-2500

-2.480

-2.460

-2.480

-2.500

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0.008

0000

1.984

1.992

-0.020

-0.000

-4.960

-4980

DB7 DB6 DBS DB4 DB3 DB2 DB1 DBO lamA

FULL-SCALE

FULL-SCALE

EOUT

HALF-SCALE

HALF-SCALE

HALF-SCALE

ZERO-SCALE

ZERO-SCALE

-1 LSB

+ 1 LSB

-1 LSB

+1 LSB

v0

J

<r::

Z

<r::

0r-

IJ

~

.......

::2

0

11-105

--

--

---

7/89, Rev. 8

IPM!)

DAC-888 BYTEDAC<1I8-BIT HIGH-SPEED "MICROPROCESSOR COMPATIBLE" MULTIPLYING D/A CONVERTER

RECOMMENDED

FULL-SCALE

ADJUSTMENT

TABLE 1. REFERENCE AMPLIFIER COMPENSATION

CIRCUIT

REF. INPUT RESISTANCE

SUGGESTED Cc

1k!l

2.5k!l

5k!l

15pF

37pF

75pF

MSB

Lsn

DB7 DBn DBS DB4 DB3 DB2 DB1 DBa

NOTE: A 001 pF capacitor

17

IS

suggested

for fixed references.

CE

CONTROL

16

For fastest response to a pulse, low values of RlO' enabling

small Cc values, should be used. If pin 10 is driven by a high

current source, none of the above values will suffice and the

amplifier must be heavily compensated

which will decrease

overall bandwidth and slew rate. For R 10 = 1k!l and Cc =

15pF, the reference amplifier slews at 4mA//-ls, enabling a

transition from IREF= 0 to IREF= 2mA in 500ns (see Figure,

pulsed reference operation I.

& LATCHES

WR

Rl0

LOW T.C.

'REF'

~

<S.OOOV

REF

lmA

-

4.Sk

. .

10

VREF'

.14

lOUT'

DAC

VREFCaMP

~ IV 11

SOk

POT

V-

GND

'OUT

V'

I

113

OBS

APPROX

Sk

Bipolar references may be accommodated

by offsetting VREF

or pin 11, as shown in Figure below. The negative common-

-=

mode

range

of the reference

amplifier

is given

plus (IREF X 1k!l) plus 2.5V. The positive

range is V+ less 1.5V.

OLE

meter TC effects is shown in the Recommended

Adjustment Circuit.

Full Scale

by VCM = V-

common-mode

When a DC reference is used, a reference bypass capacitor is

recommended.

A 5.0V TTL Logic supply is not recommended as a reference. If a regulated power supply is used as

a reference, RlO should be split into two resistors with the

junction bypassed to ground with a 0.1 /-IFcapacitor.

Using lower values of reference current reduces negative

power supply current and increases reference amplifier negative common mode range. The recommended

range for

operation with a DC reference current is +0.2mA to +4.0mA.

TE

ANALOG OUTPUT CURRENTS

The reference amplifier must be compensated

by using a

capacitor from pin 12 to V-. For fixed reference operation a

0.01 /-IF capacitor

is recommended.

For variable reference

applications,

see "Reference

Amplifier Compensation

for

Multiplying Applications" section.

Both true and complemented

vided,

where

10 + ro

=

output sink currents

IFR. Current

appears

are pro-

at the

"true"

output when a "1" is applied to each logic input. As the binary

count increases, the sink current at pin 14 increases proportionally in the fashion of a "positive logic" D/A converter.

When a "0" is applied to any input bit, that current is turned

off at pin 1~and turned on at pin 13. A decreasing logic count

increases 10 as in a negative or inverted logic 0/ A converter.

Both outputs may be used simultaneously.

If one of the

outputs is not required it must still be connected to ground or

to a point capable of sourcing IFS; do not leave an unused

output pin open.

REFERENCE AMPLIFIER COMPENSATION FOR

MULTIPLYING APPLICATIONS

AC reference applications

will require the reference amplifier to be compensated

using a capacitor from pin 12 to V-.

The value of this capacitor depends on the impedance presented to pin 10 (see Table 1).

ACCOMMODATING BIPOLAR REFERENCES

MSB

DB7 DB6 DBS DB4 DB3 DBl

DBI

LSB

DBa

MSB

DB7 DB6 DBS DB4 DB3 DBl

DB,

LSB

DBa

8

17

17

CE

+VREF

RREF

IIN

VIN~

16

CONTROL & LATCHES

rREF

10

;p;

16

We

VREF'

R'N

lOUT'

14

-0

'OUT

13

'VREF

14

VREF'

'OUT

DAC

11

VREF-

DAC

Rl1 11

D-----'VV'v--'IOPTIONAL!

VIN

11

'HEF .0 NEGATIVE

RREF 10

CONTROL & LA TCHES

We

15

9

18

HIGH

INPUT

IMPEDANCE

nHEF~HI1

SWING OF IIN

'VHEF

VREF-

CaMP

'2

1

V-

GND

l

-

IS

'OUT

V.

13

18

MUST BE ABOVE PEAK POSITIVE SWING OF V,N

J

11-106

7/89, Rev. B

lD

DAC-888

BYTEDACQlla-BIT

HIGH-SPEED

"MICROPROCESSOR

COMPATIBLE"

MULTIPLYING

D/A CONVERTER

JO INTERFACE

DATA

81

BUS

0220

-

14

10

IREF

DAC-OOO

13

--

"2

lOUT

0000

pP

x=

"

ADDRESS

- lOUT

WR

MEMW

/

><=

~

DATA

V-

cr'\.

V+

ADDRESS

BUS

ADDRESS

DECODER

lOUT

OBS

)0,6801,6809

INTERFACE

DATA

BUS

-

14

10

IREF

--

DAC-OOO

WR CE

60XX

pP

x

lOUT

13

"

/

x

DATA

CE

IJ2

VMA

x

""-J

lOUT

ADDRESS

DECODER

TE

/

'\.

R/Vi

VMA

ADORESS

BUS

X

X

ADDRESS

lOUT

- lOUT

r;GVi7

RNi

OLE

"2

X

lOUT

~5 INTERFACE

DATA

CLK

BUS

10

-

14

'REF

DAC-OOO

WRCE

0005

pP

13

--

ADDRESS

"

=><

'OUT

WR

- 'OUT

DATA

16'( 17

WR

I/O/MEM

I/O/MrM

-

I/O

MAPPED

ADDRESS

BUS

ADDRESS

DECODER

CE

lOUT

{

lOUT

T1

/

'\.

T2

"

"

/

TJ

/

"-

>C

>C

J

~

x

(j)

~

~

/

x

.

'r

!2

~

>

Z

0

u

0

0

-J

-<

Z

-<

0

t-

...J

~

..0

is

11-107

7/89, Rev. B

jpMJ)

DAC-888 BYTEDACQ';8-BIT HIGH.SPEED "MICROPROCESSOR COMPATIBLE" MUL TIPL YING D/A CONVERTER

PULSED REFERENCE OPERATION

MSB

LSB

OB7 OB6 OB5 OB4 DBJ DB2 OBI OBO

17

IT

+VREF

CONTROL & LATCHES

9

16

I

OPTIONAL

~

RESISTOR

,...,

OV-"

R'N

~

I-

'L.S

~~

FOR OFFSET INPUTS

I

.

10

'OUT

VREF+

REO>

2001/

*

TYPICAL VALUES,

5k

RIN

+VIN'

10V

WR

0-<

Rp

DAC

11

-=-

-=-

OBS

-=-

LS

18

NO CAP

.UNBALANCEO INPUTSWILL CAUSESLIGHTDEGRADATIONOF

'FS ACCURACYDUE TO 'OS OF REFERENCEAMPLIFIER

OLE

POSITIVE LOW IMPEDANCE OUTPUT OPERATION

MSB

LSB

DBl DB6 OB5 OB4 DBJ DB2 OBI DBO

t1:

CONTROL

~

VREF+

11

VREF-

10

& LATCHES

RL

.14-

'OUT'

EOUT

DAC

'OUT

OTO+IFsxRL

...L

12

15

TE

9

-.l

I

.

I

I

'REF

-=FOR COMPLEMENTARY

OUTPUT

CONNECT

GROUND.

INPUT OF OP AMP TO lOUT.

INVERTING

(OPERATION

AS NEGATIVE

LOGIC DAC).

CONNECT

'OUT

TO

NEGATIVE LOW IMPEDANCE OUTPUT OPERATION

Mm

~B

DBl DB6 DB5 DB4 DBJ DB2 OBI DBO

17

F

VREF+

11

VREF-'

CONTROL

16

& LATCHES

WR

10

EOUT

.14-

'OUT'

DAC

COMP

V-

12-- 1'5

GND

19

'OUT

/

t

18

1,0-

<'RL

I

-=-

...L

0 TO -IFS

x RL

'FR = ;~~

'REF

-=FOR COMPLEMENT ARY OUTPUT (OPERA TlON AS NEGATIVE

LOGIC OAC.' CONNEcr NONINVERTING

INPur OF OP AMP

TO 'our.

CONNECT 'our

TO GROUND.

11-106

I

i

I

'FR = ;~~

18

I

7/89, Rev. B

~Mi)

DAG-888 BYTEDACQI)8-BIT HIGH-SPEED "MICROPROCESSOR

COMPATIBLE" MULTIPLYING D/A CONVERTER

JASIC BIPOLAR OUTPUT OPERATION

MY

~B

DB] DB6 DBS DB4 DBJ DB2 DBI DBO

,s.ooov

r

17

161

-

'REF'

2.000mA

CONTROL& LATCHES

1WR

I

I

f S.OOOkH

lS.000kH

10

VREF'

lOUT

114

EOUT

In

EOUT

DAC

111

'OUT

IVREF-

OBS

12

IS

9

18

/

DB7

DB6

DBS

DB4

DB3

DB2

DB1

DBO

POSITIVE FULL-SCALE

POSITIVE FULL-SCALE -1 LSB

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

-4.960

-4.920

5.000

4.960

ZERO-SCALE

ZERO-SCALE

ZERO-SCALE

1

1

0

0

0

1

0

0

1

0

0

1

0

0

1

0

0

1

0

0

1

1

0

1

-0.040

0.000

0.040

0.080

0.040

0.000

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

4.900

5.000

+ 1LSB

-1 LSB

NEGATIVE FULL-SCALE +1 LSB

NEGATIVE FULL-SCALE

EO

EO

OLE

OFFSET BINARY OPERATION

MY

~B

DB] DBG DBS DB4 DBJ DB2 DBI DBO

'S.OOOV

SkI!

-4.920

-4.960

TE

SkH

I

.1SV

14

EOUT

r..n

~

J:.r.1

~

-lSV

>

J:.r.1

Z

0

u

DB7

DB6

DBS

DB4

DB3

DB2

DB1

DBO

EO

POSITIVE FULL-SCALE

POSITIVE FULL-SCALE -1LSB

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

4.960

4.920

ZERO-SCALE

1

0

0

0

0

0

0

0

0.000

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

-4.960

-5.000

NEGATIVE ZERO-SCALE

NEGATIVE FULL-SCALE

+ 1LSB

C.J

0

J

~

Z

~

0

r--<

,

J

~

......

C.J

5

11-109

7/89, Rev. B

IPMI)

DAC-888 BYTEDAC<7I8-BIT HIGH-SPEED "MICROPROCESSOR COMPATIBLE" MUL TIPL YING orA CONVERTER

BASIC BIPOLAR

OUTPUT

OPERATION

Both outputs have an extremely wide voltage compliance,

enabling fast direct current-to-voltage

conversion through a

resistor tied to ground or other voltage source. Positive

compliance

is 18V above V- and is independent

of the

positive supply. Negative compliance

is given by V- plus

(IREF X 1kH) plus 2.5V.

The DAC-888operates over a wide range of power supply

voltages from a total supply of 9V to 15V.When operating at

supplies of :t5V or less, IREF~ 1mA is recommended. Low

reference current operation decreases power consumption

and increases negative compliance, reference amplifier negative common-mode range, negative logic input range, and

negative logic threshold range; consult the various figures

OBS

For example,

operation

at -4.5V with 'REF =

2mA is not recommended because negative output compliance would be reduced to near zero. Operation from lower

Z-80 INTERFACE

DATA BUS

Symmetrical

supplies are not required, as the DAC-888

quite insensitive to variations in supply voltage.

is

Power consumption

may be calculated

as follows:

Pd = (1+) (V+) + (1-1 (V-).

14

DAC-888

WR GE

13

and drift essentially

The temperature

should

and

track

compared

that

CLOCK

--

to 1/2 LSB.

of the reference

of

the

output

resistor

R1O

resistor

for

of the DAC-

minimum overall full-scale drift. Settling times

888 decrease approximately

10% at -550 C; at + 1250 C an

increase of about 15% is typical.

ADDRESS

'OUT

MREO

::x

"

~

- lOUT

DATA

ADDRESS

BUS

CE

==><

TE

x

/

/

x

/

-----.....

x

'OUT

ADDRESS

DECODER

MFmi

match

negligible

coefficient

WR

""7"i6917

WR

The nonlinearity and monotonicity specifications of the

DAC-888 are guaranteed to apply over the entire rated

operating temperature range. Full-scale output current drift

is tight, typically:t 10ppm;o C, with zero scale output current

OLE

=::0

10

IREF

Z80

"p

to

TEMPERATURE PERFORMANCE

POWER SUPPLIES

for guidance.

supplies is possible. However, at least 8V must be applied

insure turn-on of the internal bias network.

lOUT

6502 INTERFACE

DATA BUS

10

-

14

IREF

DAC-888

6502

"p

WAGE

13

--

82

lOUT

ADDRESS

- lOUT

R/i'J

16'1' 17

R/Vi

DATA

IT

ADDRESS

BUS

82

'OUT

ADDRESS

DECODER

'OUT

11.110

x

"x

X

/

X

"--/

><

7/89, Rev. B

ID

DAC-868 BYTEDAC~ 8-BIT HIGH-SPEED "MICROPROCESSOR COMPATIBLE" MUL TIPLYING orA CONVERTER

48 INTERFACE

'REF

'OUT

DATA BUS

"p

'OUT

1-

WR

--'-

\

ALE~

IREF

BUS

-L

FLOATING

lOUT

OAC-888

DATA BUS

WR CE

'OUT

\

CE

IWR

OBS

"p

-

110 PORn

\

WR

IREF

CE

WR

'OUT

"p

WR

lOUT

x:xx:I..

'OUT

NOTE,

OAC OUTPUT MAY CHANGE

UNTIL DATA VALID.

TE

OFTWARE SAR' AID CONVERTER (WITH 8048 MICROPROCESSOR)

07

06

05

~

OLE

'OUT

OAC-888

/

04

03

02

01

DO WR CEW

WR'TE

STROBE

~

I

+15V

5.1MH

5.0kH

+15V

+15V

2.4kfJ

VOUTI6

+5V

(j)

~

~

10'VREF+

VOUT

REF-O2

~

~

>

Z

0

U

lJ

0

-J

-<

Z

-<

0

1-<

...J

O.Ol"F

39kH

-12V

-15V

+5V

-15V

10kH

V'N

-=-

1.. ANALOG

-=- GROUND

I DIGITAL

\1 GROUND

2kH

~

......

lJ

a

+15V

11-111

---

7/89,

Rev.

B

1

IPM!)

DAC-888

BYTEDAC'" 8-BIT HIGH-SPEED

"MICROPROCESSOR

COMPATIBLE'"

MUl TIPl YING D/A CONVERTER

SUCCESSIVE APPROXIMATION ANALOG- TO-DIGITAL CONVERSION PROGRAM

LISTING USING DAC-888 AND SYM 1 PCB WITH 6502/-lP WITH FLOW CHART

DATA

MNEMONIC

COMMENTS

500

502

504

506

506

A9oo

A208

9500

A980

A8

LOA #00

LOX #08

STA,X

LOA #80

TAY

Clear

509

50C

50F

511

513

800010

AD 00 1C

2901

FO01

98

STA 1000 (Cont.)

LOA 1COO

AND A, #01

BEO"+1

TYA

Output

Read Compo

Mask it

Branch if CMP = 0

Get Trial Bit

514

515

18

7500

CLC

ADC.X

517

519

51A

9500

98

4A

STA.X

TYA

LSR

Clear Carry

Result Summed With

Previous Test

Save it

Get Trial Value

Next Bit

51B

51C

51E

520

A8

1500

90 E9

4C 00 05

TAY

ORA.X

BCC "-23

JMP 500

LOCATION

Set Index Register

Clear Memory at 08H

Trial Bit

TOY

OBS

OLE

NOTE: 32 Bytes 260/,s

Save it

Next Data

Continue For 8 Trials

Do Over

TE

BURN-IN CIRCUIT

1B

4

-12V

OAC-BBB

+5V

13

0.1~F.50V

12

-11

10

-=-

-=

10kD

- -

11-112

-

--

7/89, Rev. B