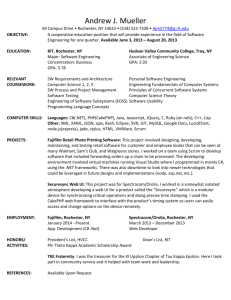

Raj Parihar - Department of Electrical and Computer Engineering

advertisement

Raj Parihar ∗ 212 Conant Rd Apt C, Rochester, NY 14623 ∗ (585) 752-1706 ∗ parihar@ece.rochester.edu ∗ ∗ www.ece.rochester.edu/∼parihar ∗ OBJECTIVE To obtain an internship/co-op position in computer architecture and related fields INTERESTS Processor microarchitecture ∗ Look-ahead architecture and helper threading ∗ Cache coherence and memory subsystem ∗ Parallel programming ∗ Binary analysis and optimization ∗ Crypto hardware and architecture ∗ Evolvable hardware and architecture ∗ Low power VLSI design ∗ Compiler design and optimiation EDUCATION Ph.D. (ECE) University of Rochester, Rochester, NY Advisor: Prof. Michael C. Huang Exp Dec 2013 M.S. (ECE) University of Rochester, Rochester, NY GPA: 3.9/4.0 May 2010 B.E.(Hons.) (EEE) Birla Institute of Tech. & Science, Pilani Advisor: Prof. Anu Gupta CGPA: 8.5/10.0 June 2006 AWARDS AND ACHIEVEMENTS • Recipient of full financial aid for whole duration of study at University of Rochester. • Recipient of student travel grant to attend conferences [MICRO’09] and [PACT’11]. • Only student to pass PhD qualification exam from computer architecture stream at ECE, UofR in year-2008. • Recipient of institute-merit scholarship at BITS - Pilani for 4 years during undergraduate study. • Among top 10 students of Electrical & Electronics group at BITS - Pilani in second semester of batch-2006. • State board topper in higher secondary (10+2) school exam in 2002 among more than 300,000 students. PROFESSIONAL EXPERIENCE Summer Intern, Content Protection Group, IBM Research - Almaden May 2012 - Aug 2012 • AES-128 module design feasibility using FPGA and GPU platforms for high speed encryption engine. • Conducted surveys on high speed encryption mechanisms and solutions. Proposed hardware based encryption building blocks for future IBM products. Research Assistant, Dept. of Electrical & Computer Eng., Univ. of Rochester Aug 2008 - Present • Working on improving single thread performance by virtually emulating the effect of large instruction window which enables flexible and efficient scheduling and overlapping of instructions using deep look-ahead. Also exploring evolvable look-ahead with the help of genetic algorithms and other evolutionary algorithms such as simulated annealing. • Working on Explicitly Decoupled Architecture (EDDA), aggressive look-ahead and dynamic helper thread based assisted execution. Also explored speculative parallelization in such look-ahead agents. • Designed, simulated and synthesized transceiver module for 3-D processor chip with intra-chip optical interconnect. This module is expected to receive/send and process data packets at 10 Gbps. Design was simulated using Modelsim and synthesis was done using RTL compiler from Cadence. • Worked on SimpleScaler framework to implement various cache designs i.e. victim cache, decoupled-cache (DC) architecture. In particular, DC architecture employs few smaller size of look-up tables per node, as oppose to full blown sharing bit-vectors, to identify the sharing patterns of particular data/page. This work is motivated by the fact that relatively larger regions (as high as 16 KB) of data are often shared among same set of processors. • Studied inductive noise avoidance techniques in high-speed low power chips. We are exploring various solutions – ranging from software (compilers) to circuit techniques – which can help in detecting and avoiding the voltage emergencies. • Worked on power characterization of frame buffer accumulator for CMOS based image sensors. We proposed to design an improved frame buffer which pre-processes the raw data (i.e. converts raw data to DCT format) at sensor end thus requires much less bandwidth. Technical Marketing Engineer, Cypress Semiconductors, Chennai, India Feb 2008 - Jul 2008 • Devised a new technique called Multi-Byte PrISM which can be used to dim LEDs and exhibits reduced electromagnetic interference (EMI) compare to Pulse Width Modulation (PWM). Work is published in application note–AN47372 and available on Cypress’ website. • One of the several modulation techniques which can be used to dim LEDs in color mixing applications is n-bit Delta Sigma Modulation (DSM). We implemented a variation of delta sigma modulation which is known as variable DSM (vDSM). Work was published in application note–AN47778 and available on Cypress’ website. • Conducted PSoC workshops at Indian Institute of Technology, Chennai and Anna University. Applications Engineer, Microchip Technology, Bangalore, India Jun 2006 - Feb 2008 • Validated EUSART and USB module of PIC18F445x. Responsible for silicon validation of device PIC18F4450 rev A4, high-performance USB micro-controller with nanowatt technology. • Designed enhanced multimedia keyboard using Microchip’s USB stack and PICmicro controllers. This firmware incorporated QWERTY keyboard, multimedia volume control and system power management along with application launch capabilities. • Designed wireless USB keyboard and mouse devices with MiWi wireless protocol and PICmicro controllers. USB and proprietary MiWi firmware stack were integrated into one stack in this work. • Silicon validation, application and library development for Streaming Parallel Port (SPP) module. Research Intern, Microsoft Research India, Bangalore, India Jul 2005 - Dec 2005 • Worked on design and prototyping of featherweight computing based devices i.e. Electronic book for rural education. Electronic book provides audio responses to a touche on the text. Prototype was implemented using ATMEGA microcontrollers and SD-MMC memory card. We also conducted few sessions of user study to improve the interface and subsequent version of same device. • Translated over 3000 names of places, streets and landmarks into Devanagari script from English for Virtual India map project. Summer Intern, Central Electronics Eng. Research Institute, Pilani, India May 2004 - Jul 2004 • Simulated and synthesized digital basic building blocks i.e. muxes, decoders, adders, D-flip flops using VHDL. • Implemented Booth radix-2 multiplier which reduces switching activities thus reduces overall power consumption. TEACHING ASSISTANTSHIPS • ECE404: Multiprocessor Design, ECE, Univ. of Rochester (Spring 2013) • ECE404: High-Performance Microprocessor Design, ECE, Univ. of Rochester (Fall 2011) • ECE401: Advanced Computer Architecture, ECE, Univ. of Rochester (Fall 2009) • ECE200: Computer Organization & Design, ECE, Univ. of Rochester (Spring 2009) • ECE221: Electronic Devices & Circuits, ECE, Univ. of Rochester • EEEC443: Analog & Digital VLSI Design, EEE, BITS- Pilani • VLSI CAD Lab, EEE, BITS - Pilani (Fall 2008) (Spring 2006) (Fall 2005) PROFICIENCY • Modeling and simulation of architectural structures using C, C++ • Program binary analysis, profiling and optimization using link time tools i.e. ALTO • High level object-oriented programming using C++ and Ruby • Parallel programming using POSIX threads, MPI, OpenMP, OpenCL and GPGPU (CUDA) • RTL design, verification, and synthesis using Verilog, VHDL, ModelSim, Cadence tools, Xilinx ISE • Analog circuit design, simulation and layout using SPICE, Spectre and Virtuoso • Embedded system prototyping and development using Microchip’s MPLAB and Cypress’ PSoC Designer • In-depth knowledge of USB device stack and IEEE 802.15.4 based Zigbee stack architecture • Data analysis using Perl, Ruby, MATLAB, Spreadsheet, shell scripting • Operating Systems: Linux, Mac, Windows, Sun Solaris, Unix, DOS PUBLICATIONS PACT’11 A. Garg, R. Parihar, M. Huang, “Speculative Parallelization in Decoupled Look-ahead”, in the proceedings of 20th Parallel Architectures and Compilation Techniques, Oct 2011. (Accept 36 out of 221) IP DEVELOPMENTS • R. Parihar, “PrISM Technology for LED Dimming”, application note at Cypress Semiconductors, http://www.cypress.com/?id=1003&rtID=5&rID=39712, Apr 2008. • R. Parihar, A. Gulati, “Sigma Delta Modulation using Cypress’ High-Brightness LED Controllers”, application note at Cypress Semiconductors, http://www.cypress.com/?id=1003&rtID=5&rID=39759, Jun 2008. PROJECTS AND REPORTS B.E. Thesis R. Parihar, C. Shekhar, and A. Gupta, “Design and Implementation of 16-bit RISC Processor using Verilog,” Electrical Engineering Department, BITS - Pilani, May 2006. Term Projects ¬ Two-stage Op-Amp design for high speed applications. ­ Parallelization of Gaussian Elimination using P-Threads and MPI. ® Parallel program generation support in URCC compiler. GRADUATE LEVEL COURSES ¬ Advanced Computer Architecture ­ High Performance Microprocessor-Based Systems ® Advance Programming Systems (Compiler Design) ¯ Parallel & Distributed Systems ° Advanced Digital VLSI Design ± HighSpeed Integrated Electronics ² VLSI Architectures ³ Performance Issues in VLSI/IC Design & Analysis ´ Seminar in Pervasive Parallelism TALKS • Lunch talk on our research Exploring decoupled lookahead to improve single thread performance hosted by Healthcare group at IBM Research - Almaden, USA, July 2012. • Conference talk on Speculative Parallelization in Decoupled Look-ahead at (PACT’11) 20th International conference on Parallel Architectures and Compilation Techniques, Galveston Island, Texas, Oct 2011. • Guest lecture on Emerging Research Areas in ECE at Vindya Institute of Technology & Science, Satna, India, Jan 2010. • Co-presented USB classes and assisted in hands-on-session of Microchip US MASTER Conference, Phoenix, USA, Aug 2007. • Represented Microchip and demonstrated TCP/IP based demos in Embedded System Conference, Bangalore, India, Sept 2007. • Assisted participants during hands-on-session in National Workshop of VLSI Design and Embedded System at BITS - Pilani, India, Mar 2006. PROFESSIONAL SERVICE • Student member: IEEE, ACM • Reviewer: INTERACT-15, INTERACT-16 (Held in conjunction with HPCA’11, HPCA’12) • Department representative of Graduate Organizing Group (GOG) at University of Rochester • Campus placement volunteer at Birla Institute of Technology & Science - Pilani • Mentor of VLSI student group for 2 years at Birla Institute of Technology & Science - Pilani REFERENCES Prof. Michael C. Huang Dept. of Electrical & Computer Engineering, University of Rochester, NY Email: michael.huang@rochester.edu, Phone: (585) 275-2111 Dr. Dulce Ponceleon Content Protection Group, IBM Research - Almaden, San Jose, CA Email: dulce.ponceleon@us.ibm.com, Phone: (408) 927-1927 Prof. Hanan Dery Dept. of Electrical & Computer Engineering, University of Rochester, NY Email: hdery@rochester.edu, Phone: (585) 275-3870 Prof. Anu Gupta Electrical & Electronics Engineering, BITS - Pilani, Rajasthan, India Email: anug@bits-pilani.ac.in, Phone: +91(1596)-245073 Ext: 463, 233 ∗More references available upon request