Digital Circuits CS437- August 27 2008 - Bethune

advertisement

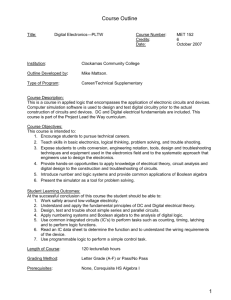

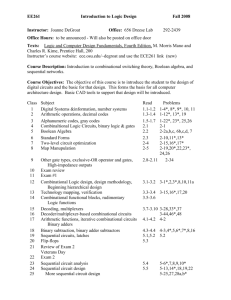

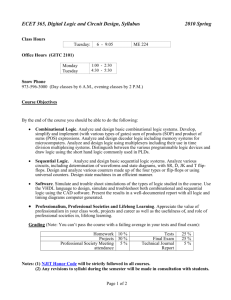

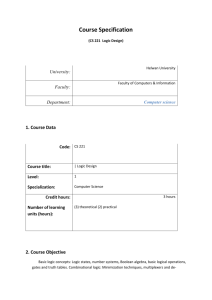

DIGITAL LOGIC CIRCUITS CS437A, Fall Semester 2008 Instructor: Mr. Mubarak Banisakher Office Phone: (386) 481-2675 Office: Science Hall 202 Email: banisakm@cookman.edu Webpage: www4.cookman.edu/faculty/Banisakher Office Hours: M: 9:00- 11:30AM, , TR: 11:15- 12:00 PM Pre-Requisite Courses: CS332, PH252 Course Description: This course covers the introduction to digital electronics, digital circuits, logic circuits, analog to digital converters, digital to analog converters, as well their applications. It includes the study of logic gates, logic families, logic function implementation, flip-flops, control circuits, codes, registers, encoders & decoders, multiplexers, counters, memory and converters. Practical experimentation and a project support the content theory. Goals This course is intended to provide a comprehensive, balanced and up-to-date coverage of digital circuits; it is intended to teach design and synthesis of two-level/multilevel combinational logic as well as finite state machine design, optimization, and synthesis. Material reinforced with the use of contemporary EDA tools. Introduces the use of a hardware-description language (VHDL). Additional goals are: 1) Do two-level logic minimization using Boolean algebra, Karnaugh maps, the Quine McCluskey method, and the Espresso software; 2) Do multi-level logic simplification using factoring and the MIS software; 3) Develop and use advanced technology mapping algorithms; 4) Develop advanced two-level minimization heuristics; 5) Design using a variety of implementation technologies, e.g., PLAs, multiplexors, CMOS transistors, and field-programmable gate arrays; 5) Draw and interpret timing diagrams; 6) Identify and accelerate a circuit's critical timing path; 7) Design static and dynamic hazard free logic; 8) Do efficient FSM state minimization, assignment, and splitting; 9) Design various arithmetic, logic, and memory components, e.g., ALUs, shifters, decoders, multiplexers, RAMs, and ROMs; 10) Design combinational and sequential circuits using VHDL; 11) Use a research-quality EDA software to perform two-level combinational logic minimization, multilevel combinational synthesis, state minimization, and state assignment of sequential logic; and 12) Use industrial EDA tools for schematic capture, gate-level logic simulation as well as HDL simulation and synthesis . Textbook: "Introduction to Logic and Computer Design” ISBN-13 978007352949-3. McGraw-Hill Book Co., New York, N.Y. Laboratory Manual There is no text for this course, but for lab work a lab manual will be provided to the students, that carry the detail of the experiments and related instructions to perform the experiments. Course Requirements: The following are minimal requirements to be met by each student: I. Lecture 8:00 – 9:00 a.m. MWF , S102 1. Regular attendance - The policy on class attendance as stated in the current University Catalog will be strictly adhered to. 2. Read all assigned material. 3. Take all exams and complete all assignments. There will be no make-up examinations except in cases of extreme circumstances such as accidents or death in the family. A student missing examinations will be given a grade of zero (0). 4. Promptness. Frequent tardiness is discouraged. The teacher has the authority to admit or refuse admission when a student is more than 15 minutes late. II. Laboratory 9:10 - 10:10 p.m. WF S203B 1. Attendance and participation are required. 2. Each experiment is to be carried out per the instructions given and written in the fashion supplied by the instructor. Evaluation: Each student’s final grade will be computed as follows: -Lecture exams - There will be approximately six lecture exams - Chapters review questions and other assignments -Midterm exam - There will be one exam -Final Exam There will be one exam - Attendance and class participation 30 % 25 15% 25% 5% Lab Evaluation There will be about 15 Lab experiment upon completion. Tests Midterm Final Exam 50% 10% 15% 25% Grading Scale: 90 - 100 = A 80 - 89 = B 70 - 79 = C 60 - 69 = D Less than 60 = F Methods of Instruction: A mixture of lectures and demonstrations combine with group work, PowerPoint presentation slides will be used in the class room and posted on the class webpage. We'll cover the course's primary topics in these sessions, with reading and homework assignments that provide opportunities to gain a deeper understanding of the underlying issues and techniques of digital circuits, this Include examples of out-of-class assignments, required reading and writing assignments, and methods for teaching critical thinking skills.) a. Lectures b. Handouts c. Homework assignments from the textbook e. Computer based training activities f. Lab activities, Practical/Experimentation g. Discussion Use of Technology: Students use the workstations in Room203B lab. Students learn to use industrial EDA tools from the instructor. Use of the internet for student-instructor communication, completion of assignments is required. Navigating the Internet and Email is part of this course. As a result, you must follow all turn-in instructions carefully and save your assignments as a soft copy. Overhead projector will be used in the classroom to run the class presentation. Impact on BCU Mission and Institutional Student Learning Outcomes (ISLOs): Through the attainment of the course student learning objectives (CSLOs), students will acquire knowledge, skills and competencies outlined in the Institutional Student Learning Outcomes, School Student Learning Outcomes (SSLOs) and Program Student Learning Outcomes (PSLOs) . The Course Student Learning Objectives fully support the University Mission and Core Values as stated in the Strategic Plan; as well as, the School Goals. Program Student Learning Outcomes (PSLOs) addressed in Course Learning Objectives. PSLO1. An ability to apply knowledge of computing and mathematics appropriate to the discipline PSLO2. An ability to analyze a problem, and identify and define the computing requirements appropriate to its solution PSLO3 .An ability to design, implements, and evaluate a computer-based system, process, component, or program to meet desired needs PSLO4. An ability to function effectively on teams to accomplish a common goal PSLO5. An understanding of professional, ethical, legal, security and social issues and responsibilities PSLO6. An ability to communicate effectively with a range of audiences PSLO7. An ability to analyze the local and global impact of computing on individuals, organizations, and society PSLO8. Recognition of the need for and an ability to engage in continuing professional development PSLO9. An ability to use current techniques, skills, and tools necessary for computing practice. PSLO10. An ability to apply mathematical foundations, algorithmic principles, and computer science theory in the modeling and design of computer-based systems in a way that demonstrates comprehension of the tradeoffs involved in design choices. PSLO11. An ability to apply design and development principles in the construction of software systems of varying complexity Course Student Learning Objectives and Measurements: 1: Introduction to Logic Circuits: Students will demonstrate knowledge of the following: (PSLO, 2, 3, 4,11) 1. Understand the principles of Boolean algebra (especially DeMorgan’s theorem) and the techniques for transforming and simplifying Boolean expressions, including standard forms for Boolean expressions. 2. Be able to analyze a schematic of a combinational logic circuit and write its logic function. 3. Given a functional description of a combinational circuit, write its logic function and design a corresponding combinational logic circuit 2. Implementation Technology : Students will demonstrate knowledge of the following : (PSLO 1, 2, 3, 4,10) 1. Understand the architecture of NMOS and CMOS logic gates, using switch models for the transistors. 2. Understand the overall architecture of PLD’s; specifically PLA, PAL, CPLD, and FPGA families. 3. Be able to calculate some electrical properties of NMOS and CMOS circuits, including noise margins, allowable fan-in/out, and power dissipation. 4. Be able to map simple functions onto PLD’s manually. 5. Given a fusemap and/or LUT contents, determine what logic function is being computed. 3. Optimized Implementation of Logic Functions : Students will demonstrate knowledge of the following : (PSLO, 2, 3, 4,9) 1. Find minimal sum-of-products (SOP) and product-of-sums (POS) expressions using Karnaugh maps, and create a corresponding circuit from AND, OR, NAND, and NOR gates. 2. Know how to minimize logic functions where some of the input combinations will never occur (“don’t care” inputs). 4. Number Representation and Arithmetic : Students will demonstrate knowledge of the following : (PSLO, 2, 3, 6) 1. Know how to represent and convert numbers between different positional number systems, including decimal, binary (unsigned, signed-magnitude, and two’s complement), hex, and octal. 2. Do negation and addition in the two’s complement number system, and detect overflow. 3. Understand the architecture of adder circuits, and how to implement them in VHDL. 5. Combinational Circuit Building Blocks: Students will demonstrate knowledge of the following: (PSLO, 2, 3, 4,6) 1. Understand the functionality of common digital building blocks including multiplexers, decoders, encoders, and comparators. Know how to use them to implement logic functions. 2. Be able to calculate the propagation delays through a circuit and draw a timing diagram. 6. Sequential Circuit Elements: Students will demonstrate knowledge of the following : (PSLO 1, 2, 3, 4,5,7,11) 1. Predict the behavior of latches (S-R and D) and edge-triggered flip-flops (D, J-K, and T) in response to time-varying inputs. 2. Understand the overall architecture of counters and shift registers, draw timing diagrams, and be able to connect these devices together to realize larger or customized functions. Examples include: cascaded counters, non-binary counters, self-correcting counters. 3. Given a logic diagram of a circuit incorporating a counter (or a PLD program), determine the counting sequence. 7. State Machines: Students will demonstrate knowledge of the following : (PSLO 1, 2, 3, 4,8) 1. Understand the overall architecture of clocked synchronous state machines, and the difference between Moore and Mealy machines. 2. Given a logic diagram of a clocked synchronous state machine (using D, J-K or T flip-flops), analyze it to determine state and timing diagrams. 3. Be able to take a functional description of a clocked synchronous state machine, and design it out of D flip-flops (or your choice of another kind) and combinational logic. 8. VHDL, CAD Tools, and PLD’s : Students will demonstrate knowledge of the following : (PSLO, 2, 3, 4,9,10) 1. Be able to read, modify, and write simple VHDL programs to implement: (a) logic and arithmetic functions, (b) flip-flops, (c) registers and counters, (d) other state machines. 2. Be able to use the Altera Quartus software application to draw schematics and run simulations. Student Learning Outcomes Matrix (SLOM) Alignment of Course Assessments with SSEM Goals, Program Student Learning Outcomes, Course Learning Objectives, Institutional Student Learning Outcomes and University Strategic Goals Course Assessments CS437 Course Learning Objectives Introduction to Logic Circuits Exams, writtenassignments 1,2,3 Implementatio n Technology Exams, written assignments, lab 1,2,3,4,5 Optimized Implementatio n of Logic Functions Exams, written assignments, lab reports Number Representation and Arithmetic 1,2 Student Learning Outcomes Matrix Program Student Learning School Institutional Outcomes Student Student Learning Learning Outcomes Outcomes The Student will: 1. Demonstrate the principles knowledge of Boolean algebra (especially DeMorgan’s theorem) and the techniques for transforming and simplifying Boolean expressions, including standard forms for Boolean expressions. 2. Demonstrate how to be able to analyze a schematic of a combinational logic circuit and write its logic function. The Student will: 1,2,3 1. Demonstrate knowledge of the architecture of NMOS and CMOS logic gates, using switch models for the transistors. 2. Demonstrate knowledge overall architecture of PLD’s; specifically PLA, PAL, CPLD, and FPGA families The Student will: 1,2,3 2. Demonstrate knowledge of how to find minimal sum-of-products (SOP) and product-of-sums (POS) expressions using Karnaugh maps, and create a corresponding circuit from AND, OR, NAND, and NOR gates. 3. Demonstrate how to minimize logic functions where some of the input combinations will never occur (“don’t care” inputs). 1,2,3 The Student will: 1,2,3,4 SSEM Goals University Strategic Goals 1,2,3,4,5 1,3 1,2,3,4,5 1,2,3,4 1,2,3,4,5 1,3, 1,2,3,4,5 1,2,3,4 1,2,3,4,5 1,2,3,4,5 1,3, Exams, written assignments, lab reports 1,2,3 Combinational Circuit Building Blocks 5 Exams, written assignments, lab reports 1,2 Sequential Circuit Elements 6 Exams, written assignments, lab reports 1,2,3 State Machines 7 1,2,3 Exams, written assignments, lab reports 2. Demonstrate knowledge of knowing how to represent and convert numbers between different positional number systems, including decimal, binary (unsigned, signedmagnitude, and two’s complement), hex, and octal. 4. Demonstrate knowledge of do negation and addition in the two’s complement number system, and detect overflow. 1,2,3 1,2,3,4 1,2,3,4,5 1,3, 1. Demonstrate knowledge of the functionality of common digital building blocks including multiplexers, decoders, encoders, and comparators. Know how to use them to implement logic functions. 2. Demonstrate knowledge of being able to calculate the propagation delays through a circuit and draw a timing diagram. 1,2,3 1,2,3,4 1,2,3,4,5 1,3, 1. Demonstrate knowledge of predicting the behavior of latches (S-R and D) and edge-triggered flip-flops (D, J-K, and T) in response to time-varying inputs. 2. Demonstrate knowledge of understanding the overall architecture of counters and shift registers, draw timing diagrams, and be able to connect these devices together to realize larger or customized functions. Examples include: cascaded counters, non-binary counters, selfcorrecting counters. 1,2,3 1,2,3,4 1,2,3,4,5 1,3, 1. Demonstrate knowledge of the overall architecture of clocked synchronous state machines, and the difference 1,2,3 1,2,3,4 1,2,3,4,5 1,3, between Moore and Mealy machines. 2. Demonstrate knowledge of a logic diagram of a clocked synchronous state machine (using D, J-K or T flip-flops), analyze it to determine state and timing diagrams. 3. Demonstrate. knowledge of being able to take a functional description of a clocked synchronous state machine, and design it out of D flip-flops (or your choice of another kind) and combinational logic. VHDL, CAD Tools, and PLD’s 8 Exams, written assignments, lab reports 1,2 1. Demonstrate. knowledge of being able to read, modify, and write simple VHDL programs to implement: (a) logic and arithmetic functions, (b) flip-flops, (c) registers and counters, (d) other state machines. 1,2,3 1,2,3,4 1,2,3,4,5 1,3, Topical Outline and Lecture Schedule Week 1 1) Introduction Topic 2 2) Combinational Systems Review of Number systems. The Design Process for Combinational Systems. Introduction to Don’t Care Conditions. ( The Development of Truth Tables. Switching Algebra. Manipulation of Algebraic Functions. Implementation of Functions with Gates. From Truth Table to Algebraic Expressions. Introduction to Karnaugh Map. ( 3 3) The Karnaugh Map Complement and Product of Sums. NAND, NOR, XOR Gates. Simplification of Algebraic Expressions. NAND Gate Implementation. General Boolean Algebra. Assignment du HomeWork #1)Exercises (1,2,3,4,5 HomeWork #2, Exercises (1,2,3,4,5 LAB #1) Exam1 (HomeWork #3, Exercises (1,2,3,4, LAB #2) Exam2 4 4) Designing Combinational Systems Minimum Sum of Product Expressions Using Karnaugh Map. Minimum Cost Gate Implementations. 5 5) Analysis of Sequential Systems 6 6) The Design of Sequential Systems Function Minimization Algorithms. Delay in Combinational Logic Circuits. Arithmetic Circuits. Decoders. Encoders. Mulitplexers. 7 (HomeWork #4, Exercises (1,2,3,4, LAB #3) (HomeWork #5, Exercises (1,2,3,4, LAB #4) Exam 3 (HomeWork #6, Exercises (1,2,3,4, LAB #5) MID-SEMESTER EXAM 8 7) Solving Larger Sequential Problems Three-State Gates. Gate Arrays. Larger Combinational Systems. (HomeWork #7, Exercises (1,2,3,4, LAB #6) Exam4 9 8) Computer Organization (HomeWork #8, Exercises (1,2,3,4, LAB #7) Latches and Flip Flops. Analysis of Sequential Systems. 10 9) Computer Design Fundamentals Flip Flop Design. Synchronous Counters. Asynchronous Counters. (HomeWork #9, Exercises (1,2,3,4, LAB #8) Exam5 11 10) The Design of a Central Processing Unit (HomeWork #10, Exercises (1,2,3,4 LAB #9) Shift Registers. Counters. PLDs. 12 11) Beyond the Central Processing Unit 13 Simplification of Sequential Circuits. 14-15 Hardware Design Languages. Simplification of Sequential Circuits. (HomeWork #11, Exercises (1,2,3,4 LAB #10) Exam6 (HomeWork #12, Exercises (1,2,3,4 LAB #11) FINAL EXAM