Content for Nancy-main buttons

advertisement

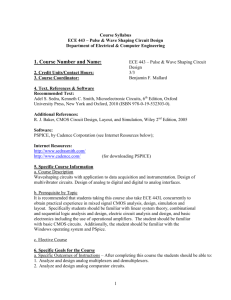

New buttons for Research Themes Information behind each button is public No icons on the buttons. It would be optimal if they could be arranged as shown here: Emerging Circuits & Applications Analog Circuits & Interfaces Digital Circuits & Systems MicroArchitecture Design Leads: Meng, Wong Stanford Lead: Sodini MIT Lead: Shepard Columbia Lead: Horowitz Stanford Silicon Infrastructure Lead: Pileggi, CMU Behind the Buttons: Emerging Circuits & Applications Emerging Circuits & Applications Analog Circuits & Interfaces Digital Circuits & Systems MicroArchitecture Design Lead: Sodini MIT Lead: Shepard Columbia Lead: Horowitz Stanford Theme Leads: Teresa Meng H.-S. Philip Wong Stanford Stanford Silicon Infrastructure Lead: Pileggi, CMU Vision The area of emerging circuits and applications, by its very nature, is necessarily broad and varied. We aim at exploring the device and circuit innovations required to extend mainstream applications to new fields such as the integration of CMOS with biological systems. It is of course impossible to explore each and every possible application one can imagine. Therefore, we focus on a few key applications that have the potential to fundamentally change the landscape of information processing and a major impact on future semi-conductor industry. The examples we have chosen are embedded implant technology, portable speech recognition and bio-molecular sensing. We also aim at the use of new materials and new devices such as organics, nanotubes and NEMS devices that may open up completely new application areas. The goal of these explorations is to develop key tools and reference circuit designs that will form the foundation for a new class of circuits using the new technologies. For emerging new materials and new devices, our goal is to focus on key circuit-level demonstrations which highlight the unique aspects of these new materials and new devices. This is distinct from device level demonstrations carried out in the MARCO FENA and MARCO MSD Centers. Many of these new devices have promising performance metrics at the device level. It is, however, not clear how device-level performance will translate into circuit level performance. It is our goal to firmly establish this circuit-level performance benchmark and identify potentially useful new devices. Principal Investigators and Research Projects Principal Investigator Tayo Akinwande Vladimir Bulovic Charles Sodini Jim Bain Gary Fedder Larry Pileggi T.E. Schlesinger Donhee Ham Tsu-Jae King Borivoje Nikolic H.-S. Philip Wong Mark Horowitz Teresa Meng Rob Rutenbar Ken Shepard School MIT Project Title Organic Integrated Circuit Design for Optoelectronics Carnegie Mellon Reconfigurable Circuits for Memory-Intensive Self-Configuring IC’s (MISC-IC’s) Harvard Circuit Demonstration of Kinetic Inductance of Metallic Carbon Nanotubes Hybrid CMOS/MIM Circuits for Ultra-Low-Power Digital ICs Emerging Si and non-Si Device Power Performance Estimation Silicon-Based Wireless Power Transfer Circuits Power-Constrained seech Recognition in Silicon CMOS++: Hybrid CNFET/CMOS Circuits and Active CMOS Biochips Berkeley Stanford Stanford Carnegie Mellon Columbia Objectives Pioneer next-generation solutions for bio-related applications and demonstrate orders of magnitude performance improvements through exploration of advanced device and circuit technologies. Demonstrate novel CMOS+NEMS technologies, that aim to drastically reduce power consumption and provide entirely new forms of on-chip reconfigurability in future IC design. Demonstrate novel CMOS+nano “hybrid” circuits that extend and augment the CMOS platform with post-Si devices. This includes targets ranging from novel organic IC technology for optoelectonics, to carbon nanotube circuits for both digital and analog applications. We will develop both the missing characterization tools and device models, and new circuits applications themselves. Build circuit-level demonstrations using these novel devices and materials. Analog Circuits & Interfaces Emerging Circuits & Applications Analog Circuits & Interfaces Leads: Meng, Wong Stanford Digital Circuits & Systems MicroArchitecture Design Lead: Shepard Columbia Lead: Horowitz Stanford Theme Lead Charles Sodini MIT Silicon Infrastructure Lead: Pileggi, CMU Vision The Analog Circuits and Interfaces Theme has the ambitious challenge of connecting massive digital processing capability with real world signals. The researchers in this thrust are committed to drive aggressively scaled silicon circuit design by: 1) expanding the transmission and detection of signals to frequencies beyond 100 GHz, 2) exploiting digital circuits to assist poorly performing analog devices to execute with demanding analog functions, and, 3) ensuring energy efficient data conversion between the analog and digital domains, across a wide range of resolution and bandwidth. Principal Investigators and Research Projects Principal Investigator School Charles Sodini H.-S. Harry Lee Gregory Wornell MIT Joel Dawson MIT Azita Emami-Neyestanak Columbia Boris Murmann Stanford Ada Poon Illinois Robert Brodersen Berkeley Rick Carley Carnegie Mellon William Eisenstadt Florida H.-S. Harry Lee Teresa Meng MIT Stanford Project Title Millimeter Wave Active Imaging Array An Analog/Digital Hybrid Architecture for RF Transceivers in Deep-Submicron CMOS Fully Digital Clock and Data Recovery Techniques for High Speed Electrical IOs Leveraging the Strengths of End-of-Roadmap Technology for a New Generation of Low Power, High Performance Data Converters CMOS-based High Resolution Analog Beamformer Enhancing dynamic Range in a Cognitive Radio Design of High-Performance Analog/Digital Interfaces in Deep Sub-100nm CMOS On-Chip/Probe 77 GHz CMOS S-Parameter and Noise Detection Systems Ultra High-Speed Analog to Digital Converters Front-End Analog Circuit Design for Neuro- Mike Perrott MIT Ken Yang UCLA C. Patrick Yue California-Santa Barbara Electro Interface Digital Phase Locked Loops and their Applications Multi-G Samples/sec Data Converters for Wireline Applications In-scribe-line Wireless Test Circuitries for OnWafer Process Variation Monitoring Objectives The following list enumerates the essential outcomes that we expect from our research in this theme. More detailed outcomes can be found in the corresponding statements of work. Design millimeter wave circuits that drive circuit design beyond 100 GHz to improve imaging spatial resolution while maintaining the advantages of low-cost energy-efficient silicon technology. Employ spatial filtering using multiple antennas to enhance RF front-end sensitivity across dynamically chosen frequencies. Investigate energy-efficient data conversion (≤ 0.1 pJ/bit) across a broad range of speed and accuracy by demonstrating novel architectures, such as comparator based switch capacitor circuits and adaptive resolution conversion. Demonstrate circuits that use the capabilities of massive digital processing, with scaled technology, to assist analog performance across a range of applications, including clock and data recovery, RF wireless, and data conversion circuits. Develop test strategies that incorporate “in-scribe-line” phase lock loops for wireless testing, as well as on-chip probing circuits capable of characterizing wireless circuits in the 100 GHz range. Digital Circuits & Systems Emerging Circuits & Applications Analog Circuits & Interfaces Leads: Meng, Wong Stanford Lead: Sodini MIT Digital Circuits & Systems MicroArchitecture Design Lead: Horowitz Stanford Theme Lead Kenneth Shepard Columbia Silicon Infrastructure Lead: Pileggi, CMU Vision Digital integrated circuits continue to be “workhorse” of modern integrated circuits, buoyed by the robustness of operating margins, well-developed synchronous models of computation, and automated design methodologies. Because of these characteristics, digital circuits are traditionally in the best position to immediately exploit leading-edge CMOS processes. The grand challenges affecting digital circuits are those that “upset” this balance. Increasing process variations are producing major challenges for robust digital circuits (particularly SRAMs) in sub90-nm technology nodes. Subwavelength lithography and stress-related proximity effects produce large systematic variations, combined with the random variability of line-edge roughness and random dopant fluctuations. The energy expended to perform a calculation directly trades off against the achievable performance and appropriately optimizing this across device options, circuit families, clocking paradigms, and interconnection fabrics creates unique challenges to traditional design abstractions and the design automation and productivity tools on which they are based. Robust digital circuit design increasingly relies on circuits that measure and adjust, to statically move to appropriate optima in the presence of variability and to dynamically adjust to time-dependent device wear-out mechanisms and hostile interconnect and power supply environments. Digital circuits must be able to incorporate the “bleeding-edge” CMOS-compatible device structures and take full advantage of the additional degrees of freedom that these device structures may provide. Principal Investigators and Research Projects Principal Investigator Robert Brodersen Anantha Chandrakasan School Berkeley MIT Mark Horowitz Ken Mai Ben Calhoun Rajit Manohar Dejan Markovic Stanford Carnegie Mellon Univ. Virginia Cornell UCLA Subhasish Mitra Bora Nikolic Bora Nikolic Tsu-Jae King Kaushik Roy Stanford Berkeley Berkeley Ken Shepard Columbia Purdue Project Title Cognitive Radio Design Energy-Efficient, Variation-Aware Radio in Nanometer Scale CMOS On-Chip environmental Monitoring and Control SRAM Circuit Design and Optimization at 45 nm and Below Reconfigurable Asynchronous Systems Optimization and Rapid Prototyping of PowerLimited Digital Systems: A Methodology for Power-Area-Speed Optimization On-Line Circuit Failure Prediction and Correction Principles of Robust Digital Design Robust SRAM Design in Deeply Scaled Technologies Technology-Circuit Co-Design for CMOS Logic/Memories using Multiple-Gate FETs Crosstalk-Aware Equalization for TransmissionLine, On-Chip Busses Objectives Our objectives are focused on four principle sub-themes: Power. We seek a broad understanding of how to maximize the performance of digital integrated circuits under energy constraints: device and circuits choices; VDD, frequency, and VT optimization; parallelism; synchronous and asynchronous designs; and clocking and interconnect approaches. In collaboration with the Silicon Infrastructure Theme, we also seek to render this in an automated CAD flow that respects traditional design abstractions and simple sequential design methodologies. Variability. Building on the measurement, modeling, and characterization work of the Silicon Infrastructure Theme, we seek circuit structures (both logic and memory) that are less sensitive to circuit variability, both in energy and delay. The “Scaled SRAM” driver will be important vehicle for this subtheme. Dynamically robust circuit architectures. We seek digital circuits that measure and dynamically adapt to remaining variability sensitivity (in energy and delay) and timedependent phenomena, such as circuit aging (e. g. NBTI) and hostile voltage and temperature environments. This includes circuits to both monitor device characteristics and electrical environments and “knobs” to reconfigure and adjust circuit operation. We also recognize the continuing strength of digital circuit structures over traditional analog and RF circuits in the nanometer CMOS world; as such, we continue to explore ways in which traditional analog functions can be performed digitally (which also constitutes an important aspect of the “Mostly Digital Analog Systems” crosscut). End-of-CMOS device challenges. We seek to fully incorporate (through predictive models and early test vehicles) new end-of-roadmap CMOS devices including FinFETs and double-gate (DG) FETs both in logic and memory. Microarchitecture Design Emerging Circuits & Applications Analog Circuits & Interfaces Digital Circuits & Systems Leads: Meng, Wong Stanford Lead: Sodini MIT Lead: Shepard Columbia MicroArchitecture Design Theme Lead Mark Horowitz Stanford Silicon Infrastructure Lead: Pileggi, CMU Vision For microarchitects, Bob Dylan’s phrase, “the times they are a changing” has never been truer. For at least the past two decades microprocessor performance doubled every 1.5 to 2 years. In some ways, the principle role of microarchitects during this period was to figure out way to convert increasing chip complexity into increased performance to continue this trend. Sometime in the early part of 2000 the exponential scaling of microprocessor performance finally slowed, and the industry is now off trying to integrate multiple cores on a chip to increase performance rather than scaling single core performance. One of the contributing factors to this change is the growing power problem, especially in an era where Vdd will scale slowly if at all. Creating the highest performance machine is no longer interesting, since it will exceed the applications power budget. Finally the issue of increasing transistor variability has become critically important. In particular, future chip designs not only will need to deal some manufacturing defects, but also with time varying transistor characteristics, and even outright circuit failures during their operation. While these issues are a serious challenge to today’s processors suppliers, it creates a tremendous opportunity for innovative research, since there is a true need for radical thinking. The changes facing microarchitecture are so large that it will be one area where incremental, safe research can not dominant the field – there is no way that incremental research will address the issues this field currently faces. Fundamentally research in this theme needs to address two large issues. The first is how to enable the creation of more parallel applications to run on all the multi-core processors being generated today. The second is how to construct systems that are yield well, and are robust in the field, in the face of the large transistor variations, and device changes during operation. Of course the resulting systems need to accomplish these goals using efficient implementations, so the resulting power and die costs are minimized. Thus this research falls into one of three broad areas – expressing and exploiting parallelism, robust computing systems, and improved processor implementations. Principal Investigators and Research Projects Principal Investigator David August Babak Falsafi James Hoe Mark Horowitz Stephen Boyd Christos Kozyrakis Gabriel Lee Sung Kyu Lim Hsien Shen Loh Margaret Martonosi Teresa Meng Sanjay Patel School Princeton Carnegie Mellon Stanford Georgia Tech Project Title Threading the CMP Needle with Fibers and Frays Robust and Complexity-Effective Chip Multiprocessors for Gigascale Circuits Large-Scale and distributed Optimization/PowerOptimized Processors Practical Parallel Programming with Transactions High-Performance 3D Microarchitecture Design Princeton Stanford Illinois High-Performance 3D Microarchitecture Design Merge Architecture and Programming Model Applications-Oriented Architecture Stanford Objectives We have three basic areas of work, and so group our objective into three broad categories. Expressing and Exploiting Parallelism. The objective here is to make parallelism pervasive – everyone should be creating and running parallel applications. Since it is not clear how to accomplish this task, we are working on two approaches: Create new software analysis tools to extract parallelism from existing applications. Create new programming models that greatly simplify the task of creating parallel applications, and create the hardware that executes these programming models effectively Robust Computing Systems. The objective here is to create a computing system that will complete an application without error, even in the face of transient failures like soft errors and noise, and long time transistor degradation. To approach this goal requires solving two separate problems: Detecting when an error occurs, and starting some corrective action Maintaining enough application state, so when an error is detected, one can roll back to a known good execution point and restart the execution. The amount of state storage required depends on the time granularity of the checking Improved Processor Implementations. We need to explore new technology and tools to create more efficient computing structures. In this area we are going to explore three approaches Exploit future manufacturing technologies like 3-D integration Leverage recent work in design optimization tools to explore the performance energy trade-off space of processors, Explore how limiting the application domain changing the performance energy tradeoff space. Silicon Infrastructure Emerging Circuits & Applications Analog Circuits & Interfaces Digital Circuits & Systems MicroArchitecture Design Leads: Meng, Wong Stanford Lead: Sodini MIT Lead: Shepard Columbia Lead: Horowitz Stanford Theme Lead: Larry Pileggi CMU Silicon Infrastructure Vision The Silicon Infrastructure Theme addresses the daunting task of providing a foundation on which robust digital, analog/RF and mixed-signal integrated systems can be implemented in a predictable manner. The researchers in this theme propose to collaboratively investigate circuits and methods to characterize, capture and correct the silicon realities and imperfections which are expected to undermine our ability to design and manufacture reliable, high-yield silicon systems in a timely and cost-effective manner. Principal Investigators and Research Projects Principal Investigator Shawn Blanton School Carnegie Mellon Project Title Test for Yield and Reliability Enhancement Duane boning Anantha chandrakasan Robert Brodersen Yu (Kevin) Cao MIT Peng Li Texas A&M Ali Niknejad Berkeley Michael Orshansky Univ. Texas-Austin Larry Pileggi Carnegie Mellon Larry Pileggi Ken Mai Larry Pileggi Rob Rutenbar Carnegie Mellon Ken Shepard Columbia Vladimir Stojanovik Joel Dawson Andrzej Strojwas Wociech Maly MIT Berkeley Arizona State Carnegie Mellon Carnegie Mellon Carnegie Mellon Process Variation in Advanced Technologies and Circuits BEE2 Design Framework Predictive Technology Modeling for Early circuit Design with End-of-the-Roadmap and PostSilicon Technology Large-Scale Parametric Variation Analysis for Design & Test of Analog Systems RF and Analog Models for Nanoscale CMOS Technology Circuit synthesis under Uncertainty Using DesignTimeOptimization and Post-Fabrication Adaptivity Regular Fabric Logic circuits and Design Methodology Memory Design for Regular Fabrics Robust Design of Analog/RF Regular Fabrics From Finance to Flip-Flops: Nontraditional Statistical Analysis and Optimization for Scaled Circuits On-Chip Test and Measurement Circuits for Device and Interconnect Variability Monitoring Optimization with Uncertainty for Analog/MixedSignal Regular Circuit Fabrics Design for Manufacturability of Extremely Regular Fabrics Objectives The following list enumerates the essential outcomes that we expect from our research in this theme. More detailed outcomes can be found in the corresponding statements of work. Design, modeling and measurement of basic patterning structures to characterize silicon realities in a manner that facilitates predictable construction of regular fabrics. Abstractions and models of regular-fabric silicon realities which facilitate optimization and topology exploration of digital, analog/RF and mixed-signal circuits. Design of circuits and corresponding regular fabrics which minimize parametric variability. Development of testing and design methodologies which support silicon recovery.