2. Proposed sensor node architecture

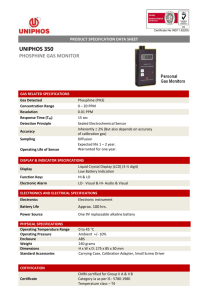

advertisement

Low Power Sensor Node for a Wireless Sensor Network Akapeti Sravan, Sujan Kundu and Ajit Pal Computer Science and Engineering Department, IIT Kharagpur, India sujank, apal@cse.iitkgp.ernet.in Abstract Electronic devices like sensor nodes which are also called as motes are getting smaller, but their battery charge density is not getting increased in the same ratio. Since the life of a sensor network depends on the life of the sensor nodes, the lifetime of the sensor nodes have to be maximized. This can happen if the battery lasts long. In this paper, we introduce a power aware sensor node architecture and a battery-aware task scheduling algorithm that uses both Dynamic Voltage Scaling (DVS) and Reverse Body Biasing (RBB) to maximize the battery life time. 1. Introduction Wireless sensor networks are gaining immense importance in today’s world with respect to the innumerous number of applications in which they can be used. These applications range from military surveillance, environment monitoring, inventory management, habitat monitoring, health monitoring etc. Almost all these applications need the sensor network to be alive for months even for years. So, the main objective when the sensor nodes are deployed is that the life of the sensor network has to be maximized, so that it can last the duration the application demands. The lifetime of the sensor network depends on the lifetime of the constituent sensor nodes. Given that the sensor nodes are battery powered and cannot be recharged or replaced upon its complete discharge, the sensor node lasts only till its battery lasts. So, in order to improve the sensor network lifetime, the battery lifetime of the individual motes has to be maximized. Some of the approaches in improving the sensor node lifetime are by using energy efficient sensor node architecture, power-aware sensor network architectures and power-aware protocols. The power dissipation in sensor networks can be broadly divided into two parts. They are the communication power and the computation power. It has been observed that the amount of energy consumed in the communication process is much higher than the amount consumed in the computation process. So, by using power-aware protocols in the protocol stack, the amount of energy consumed can be minimized. A lot of the research has been done in the fields of power-aware routing protocols and power-aware MAC layer protocols in [2] and [3]. Some of the power-aware routing protocols [1] are directed diffusion, EAR (Eavesdrop and Register) and LEACH [11] (Low Energy Adaptive Clustering Hierarchy). Some of the MAC layer protocols are SMAC [2] and CSMA/CA [12]. A lot of research in recent years has been done in the field of battery driven system design for embedded systems [6]-[10]. The research in this field can be divided into battery modeling, power profiling, task scheduling and battery scheduling. A sensor network architecture is one of the most important design criteria for sensor networks. Some of the design features in sensor network architecture are localization, clustering, synchronization etc. The other design issues in sensor network architecture are whether the communication is single hop or multi hop and single path or multiple paths. The goal of a sensor network designer is to develop power-aware protocols for the chosen architecture. The energy consumed in the sensor node can be reduced by minimizing the amount of time the hardware units are switched ON. The processor can be put in various power states whenever it is idle. Since most of the energy consumed is due to idle listening of the receiver, the receiver has to be switched ON only when there is some data packet for that node. So, energy-efficient node architecture has to be designed. We propose a node architecture that minimizes the energy consumed by the receiver. In most of the sensor nodes the power consumed by the processor is reduced by using dynamic voltage scaling. Dynamic voltage scaling mainly reduces the dynamic power. In the coming years, with the feature size getting smaller, leakage power will start to dominate. So, the leakage power also has to be reduced. Since the battery life has to be maximized, we propose a battery aware task scheduler algorithm that maximizes the battery life by scheduling the tasks accordingly and also assigning the voltages such that dynamic power as well as leakage power is reduced. Our proposed battery aware task scheduling is an extension of [9] where the slack is utilized by scaling the voltage, where as we try to utilize the slack, by not only scaling the supply voltage Vdd but also the body bias voltage Vbs. We not only concentrate on reducing the dynamic power but also the leakage power, at the same time improving the battery lifetime. The rest of this paper is organized as follows. In the next section we describe our proposed sensor node architecture and also introduce our battery aware task scheduler. In Section 3, we present the implementation and results. The paper is concluded in Section 4. 2. Proposed sensor node architecture The primary goal of the system architecture is to design an architecture that is power-aware in every aspect of the sensor application. The device should capture the event driven nature of the sensor network applications. The architecture of a sensor node can be visualized as having three layers, application layer, operating system (OS) layer and physical layer. 2.1. Application layer & OS layer The application layer consists of the implementation of the application. All network specific and hardware specific details are abstracted to the application. The OS layer provides the libraries and functions through which the nodes can communicate with one another and the hardware can be accessed. The OS layer itself can be further divided into two layers. They are: 1) Protocol layer and 2) Kernel level modules. The protocol layer consists of the protocols for infrastructure maintenance of the sensor network and for communication between the nodes. When the nodes are deployed, the infrastructure has to be built by communicating among the nodes. The protocols for building the infrastructure are Localization protocol, Clustering protocol, Synchronization protocol, etc. Apart from the infrastructure maintenance protocols, the network protocols like CSMA/CA with RTS/CTS for MAC layer and Directed Diffusion for the network layer are implemented as communication protocol. The kernel level modules are the operating system components that directly access hardware. Since the sensor node is very application specific, it should be very compact and less complex. The sensor application is characterized by its event driven nature. The task scheduler is used to schedule the tasks in the system. We propose our battery-aware task scheduler later in this section. The dynamic power management unit puts the processor in one of the multiple power states (Normal, Auto Halt, Quick Start and Deep Sleep) as specified by the ACPI [4] and this maximizes the power savings for the processor. When the processor is in the idle state, there is no dynamic power consumption, but there is leakage power consumption. So, reverse body biasing has to be performed so that leakage power is reduced. 2.2. Physical layer The physical layer consists of sensors, processor, memory, power supply units, the transceiver and the components like clock generator, DC-DC converter, ADC etc. For our power-aware approach the processor needs to operate at various voltages and so it needs a DC-DC converter that changes the supply voltage of the processor as and when required. The task scheduler assigns the optimal values of operating frequency, supply voltage (Vdd) and the body bias voltage (Vbs) that give the least power consumption. The power consumed by the transceiver can be reduced by switching the radio from the ‘on’ state to the ‘off’ state judiciously. The transmitter is switched ‘on’ only when there is some packet to be transmitted. But the receiver monitors for external events i.e. messages from other nodes always. But keeping the receiver always ‘on’ hoping to receive some message, consumes a lot of power. We propose to use an extra circuit called a wake-up circuit that monitors for a special packet called a wake-up packet transmitted at a special frequency. This wake-up circuit is a very simple circuit containing mainly an antenna. After receiving a wake-up packet, the wake-up circuit triggers an interrupt with an output voltage. The interrupt service routine for this interrupt will switch on the receiver. For implementing this design, a slight modification has to be made in the MAC protocol. Before sending the RTS, each node has to send the wake-up packet indicating that a packet will come. The wake-up packet is a small packet and thus is not an overhead compared to the energy savings obtained by avoiding idle listening of the receiver. The RTS/CTS communication exchange can help further in reducing the power consumption using a duration of communication field in the message headers (see [12]). 2.3.Our proposed battery aware task scheduler 2.3.1 Battery Model. A rechargeable battery is characterized by a maximum voltage and a cutoff voltage. The battery is said to be fully discharged if its voltage falls below its cutoff voltage. The available capacity of the battery is the difference between its maximum voltage and its cutoff voltage. This available capacity is dependent on two phenomena [6] called rate capacity effect (higher rate of discharge leads to lower available capacity) and recovery effect (the battery voltage recovers in the idle periods). The battery model presented is a high level analytical model [9]. It gives an analytical relationship between the current load, discharge time and the corresponding charge slack at that discharge time. Under the time-varying discharge i(t), the battery model is given by the following equation i ( )d 2 i ( )e L 0 m 1 L 2 m 2 ( L ) 0 d (1) Where, L is the lifetime of the battery, is a constant that represents the total capacity of the battery and 2 is the diffusion rate within the battery. For a constant discharge current (i(t) = I), equation (1) becomes as follows: 1 e m L I L 2 (2) 2 m 2 m 1 A small value of represents that the load has to 2 2 be decreased for the battery to recover and a high value of imply that the battery acts almost like an ideal power source. 2.3.2. The Task Scheduler. We follow the task scheduler model presented in [9]. A task is considered to be a 4 tuple with the parameters being the current load Ik, the execution time Δk, the start time tk and the deadline dk. Since our scheduler is a battery aware scheduler, the objective of the scheduler should be to minimize the battery discharge without violating the deadlines of the tasks. Let T be the length of the task profile, i.e. T = tn-1 + Δn-1. Then the charge consumed till time T is given by the following equation. n 1 I k F (T , t k , t k k , ) (3) k 0 where, e m (T t k k ) e m ( T t k ) F (T , t k , t k k , ) k 2 (4) 2m2 m1 2 2 2 2 Here, is the charge discharged from the battery in time T. So Q = - represents the amount of charge left after time T. We need to maximize Q by minimizing the . A negative Q at the end of a task profile represents that the battery has failed at some point with in the profile. In [9], the task scheduler used dynamic voltage scaling (DVS) to reduce the energy consumption and to maximize the battery life. By applying DVS alone, the dynamic power is being reduced, but the leakage power does not reduce much. We tend to minimize the battery discharge and energy consumption by applying the combination of DVS and reverse body biasing (RBB). The combination of DVS and RBB to minimize the energy consumption is presented in [5]. We follow the models in [5], to get the optimal pair of the supply voltage and body bias voltage. This optimal pair is generated by our task scheduler and is assigned when that task runs. 2.3.3. Key Properties. Our battery-aware task scheduling algorithm follows the three properties of the battery discharge model as given in [9]. Property 1: For a fixed voltage assignment, sequencing tasks in the non-increasing order of their currents is optimal when the task loads are constant during the execution of the task. Property 2: If a battery fails during some task k, it is always cheaper to repair k by down scaling its voltage than by inserting on idle period before k. Property 3: Given a pair of two identical tasks in the profile and a delay slack to be utilized by voltage downscaling, it is better to use the slack on the later task than on the earlier task. 2.3.4. The algorithm. Our algorithm works in two phases. The first phase generates a feasible schedule such that the tasks do not miss their deadlines. In the second phase, available slack is utilized to minimize energy requirement by down scaling both supply voltage Vdd and body bias Vbs in an optimal manner. Phase I: Generating a Feasible Schedule The input to this phase is a set of task graphs. From these task graphs, a feasible schedule is obtained. First, using the Earliest Deadline First algorithm a schedule is formed such that the task dependencies do not violate. Next using this schedule and the Property 1 an another approach is used to reschedule the tasks so that a non-increasing order of their current loads is obtained, if possible, and ensures that they do not miss their deadlines and violate the dependencies. Now, starting from the first task, each task has to be checked whether it completes its execution or the battery fails, using the equation (4). If the battery fails, then failure recovery is done by downscaling the supply voltage for the task to a minimum level until the battery doesn’t fail. Now the completion time of the task and its successors have to be checked. If it crosses the deadline, then its previous task has to be downscaled and the same procedure is continued until the failing task doesn’t cause the battery to fully discharge. If this procedure goes all the way to the first task without repairing the battery failure of the failing task, then the schedule is not possible. The reason why, the tasks are downscaled as little as possible is because it allows greater amount of slack to be used by the latter tasks so that they can downscale to a larger extent, thus causing minimum energy consumption. This is according to property 3. Phase II: Slack Distribution The input to this phase is a task schedule obtained in Phase I, which survives the battery capacity. In this phase slack is distributed among the tasks. Starting from the last task, slack time, which is the difference between the task completion time and the deadline is calculated. This task is downscaled to the least possible extent beyond which either the task deadlines are missed or it is not possible to downscale further. While downscaling, both supply voltage Vdd and body bias voltage Vbs are considered. The optimal combination of the Vdd and Vbs which causes the minimum energy to be consumed is selected. Now if there is any further slack then the remaining slack is distributed among this task’s predecessors in the similar way. This procedure is continued until no slack is available or none of the tasks can be downscaled further. 3. Implementation and Results The proposed battery aware task scheduler has been implemented in C language. This uses the CMOS power models given in [5] and the analytical battery model given in the previous section. The proposed battery aware task scheduler uses a combination of DVS and RBB. The scheduler has been simulated using the Transmeta Crusoe 5600 processor in both the 0.18µ and 0.07µ technologies. The battery capacity and the nonlinearity constant are taken to be 36220 mA-min and 0.637 min-1/2, respectively for all the simulations. The results of our scheduler have been compared to the results of the battery aware task scheduler which uses only DVS [9]. The simulations have been carried out using these power models on many task profiles. One of the task profiles is given below in table 1 for analyzing the results of the simulation. Table 1. Task profile with 4 independent tasks Task T1 T2 T3 T4 Execution time (Sec) 3 4 3 4.5 Deadline (Sec) 10 20 20 30 Current load (mA) 120 50 100 40 Table 2. Comparison of energy consumed by various scheduling algorithms on task profile in table 1 in 0.18 micron technology Procedure Without DVS and RBB With DVS alone With DVS and RBB Energy consumed Percentage reduction in energy 177.07 J - 26.62 J 84.96% 12.76 J 92.79% In the task profileof table 1, we have assumed that all the tasks arrive at the same time and they are independent of one another. The result of the simulation of this task profile is given in table 2. The above result emphasizes the gain obtained by using a battery aware scheduler. When the scheduler uses DVS alone, it gets a gain of nearly 85% and gets a gain of nearly 93% while using a combination of DVS and RBB. Our algorithm actually gives a gain of nearly 52% over the former algorithm when only these two are compared. The gain obtained can be viewed from the angle of average duty cycle of the tasks. The average duty cycle of the tasks is the average of the duty cycle of the individual tasks. This metric is of more importance as the low-duty cycle applications can leverage these batter aware algorithms to get a higher gain. In Table 3 and Table 4 the results of the simulation of the task profile for different duty cycle given in Table 1 for 0.18 technology and 0.07 technology, respectively. From Fig.1, it can be seen that the combination of DVS and RBB gives more gain when the duty cycle is less and starts to give lesser gain as the duty cycle increases and when the utilization is above 75%, the gain using DVS alone is almost equal to that obtained using DVS + RBB algorithm. The analysis can be made by dividing the graph into three zones. Table 3. The simulation of the task profile in table 1 varying the duty cycle in 0.18 micron technology Avg. Duty Cycle Without DVS and RBB With DVS alone With DVS and RBB 10 % 15 % 20 % 25 % 30 % 35 % 40 % 177.07 J 177.07 J 177.07 J 177.07 J 177.07 J 177.07 J 177.07 J 19.92 J 21.46 J 26.62 J 36.33 J 91.69 J 119.1 J 175.4 J 3.91 J 5.74 J 12.76 J 21.62 J 57.67 J 107.1 J 175.4 J The first zone ranges from the 10% - 25% duty cycle. In this zone, as the duty cycle is less, in both the DVS and DVS + RBB algorithms, the supply voltages are Table 4. The simulation of the task profile in table 1 varying the duty cycle in 0.07 micron technology Avg. Duty Cycle Without DVS and RBB With DVS alone With DVS and RBB 10 % 15 % 20 % 25 % 30 % 35 % 40 % 43247 J 43247 J 43247 J 43247 J 43247 J 43247 J 43247 J 4530 J 4531 J 4536 J 5798 J 20557 J 27550 J 43245 J 80 J 81 J 127 J 187 J 9125 J 24952 J 43245 J assigned less values, since there is a large amount of slack. Additionally, in DVS + RBB, some more left over slack is utilized by reducing the body bias voltage. So the energy due to subthreshold leakage current is also reduced. The second zone ranges from 25% - 35% duty cycles. Here there is a sudden increase in the energy consumption. Since the duty cycles are higher here, the available slack is less and so the supply voltages are higher. Since power is proportional to the square of the supply voltage, the energy consumed is increased drastically. Applying the body bias voltages reduces the energy consumed as shown by the DVS + RBB algorithm. The third zone ranges from 35% - 40% duty cycle. Here, the utilization of the processor is above 75%. So the available slack is very less. Both the DVS and DVS + RBB algorithms apply high supply voltages so that the deadlines are not missed. Also applying body bias voltages cause the deadlines to miss, so applying them is not useful at high utilization. So both the DVS and DVS + RBB algorithms give almost the same gain at higher duty cycles. The figure 2 depicts the results in the table 4. Since the simulations here are carried in 0.07µ technology, the energy consumed is very high. But the pattern of the energy consumed by DVS and DVS + RBB is the same. The explanation is the same as the one given for the simulations in 0.18µ technology. There is one significant point that can be noticed from the figure 2. When the average duty cycle is above 30%, the gain obtained using DVS + RBB over DVS alone is almost the same in Fig. 2 i.e. at 0.07µ technology, as the one obtained in Fig. 1 i.e. at 0.18µ technology. But in the duty cycles that are less than 25%, the gain is very significant. The reason for this is that at lower process technologies, like 0.07µ technology, the subthreshold leakage current increases drastically which causes the leakage power to increase. In DVS + RBB algorithm, by applying the body bias voltages, the subthreshold leakage current is controlled. So the gain perceived in this duty cycle range in Fig.2 is higher than that in Fig.1 where a higher process technology (0.18µ technology) is used. On running 100 task profiles with task graphs of varying number of tasks and averaging the amount of improvement of DVS + RBB algorithm over DVS and neither DVS nor RBB algorithms on both 0.18µ technology and 0.07µ technology, we get the graphs in figure 3 and 4 respectively. So, it can be concluded that DVS + RBB can be applied to the processor for low duty cycle applications. Though it can never result in higher energy consumption than the DVS alone algorithm, it is not advisable to apply this at very high duty cycles. This is because there is an additional hardware circuitry that is used to apply the body bias voltage. This consumes some extra energy. So, at high duty cycles, considering this additional circuitry, the total energy expended by the processor can be higher than the amount expended by the DVS alone algorithm. Figure 1. The graph for table 3 Figure 3. Improvement of DVS + RBB algorithm over DVS and neither DVS nor RBB on 0.18u technology Figure 2. The graph for table 4 Paradigm for Sensor Networks”, Mobicom’00, Boston 2000, pp. 56-67 [4] www.acpi.info [5] Steven M.Martin, Krisztian Flautner, Trevor Mudge, and David Blaauw. “Combined Dynamic Voltage Scaling and Adaptive Body Biasing for Lower Power Microprocessors under Dynamic workloads”. [6] K. Lahiri, A. Raghunathan, S. Dey, and D. Panigrahi, “Battery driven system design: a new frontier in low power design,” Proc. of the 15th International Conference on VLSI Design (VLSID’02), Jan.2002, pp. 261-267 Figure 4. Improvement of DVS + RBB algorithm over DVS and neither DVS nor RBB on 0.18u technology 4. Conclusion In this paper we have proposed a power-aware sensor node architecture and a battery –aware task scheduling algorithm using both DVS and RBB to maximize the battery lifetime. It has been observed that for low duty cycle applications, our battery aware scheduling algorithm can give very significant energy savings. Using 0.18μ technology, we can see that for a duty cycle of 25%, we can get an improvement of above 40% over the algorithm that uses DVS alone. As the duty cycle further decreases the improvement increases. For 0.07μ technology, the improvement is very high owing to the high amount of leakage power our algorithm reduces compared to the DVS alone algorithm. With downscaling of the size of the CMOS circuits being the present trend, the leakage power reduction becomes very necessary. So, our algorithm gains more importance in the future. So, a combination of the power aware protocols and the dynamic power management schemes ensures that power consumption is reduced and at the same time the battery lifetime is increased, thereby increasing the network lifetime. 5. References [1] L.F. Akyildiz, Weilian. Su, Y. Sankarasubramaniam, E. Cayirci, "A Survey on Sensor Networks", IEEE Communications Magazine, August 2002, pp. 102-114 [2] Wei ye, John Heidemann, and Deborah Estrin, “An Energy-Efficient MAC Protocol for Wireless Sensor Networks”, Twenty-First Annual Joint Conference of the IEEE Computer and Communications Societies (INFOCOM), volume 3, June 2002, pp. 1567-1576. [3] C. Intagagonwiwat, R. Govindan, and D. Estrin, “Directed Diffusion: A Scalable and Robust Communication [7] Rakhmatov, S. Vrudhula and C. Chakrabarti, “BatteryConscious Task Sequencing for Portable Devices Including Voltage/Clock Scaling” Proc. of the 39th conference on Design automation (DAC 2002), June 10-14, 2002, pp. 189194 [8] R. Rao, S. Vrudhula and D. Rakhmatov, “Battery modeling for energy aware system design” IEEE Computer, Special Issue on Power Aware and Temperature-Aware Computing, December 2003, pp. 77-87 [9]. P. Chowdhury and C. Chakrabarti, “Static taskscheduling algorithms for battery-powered DVS systems”, IEEE transactions on very large scale integration (VLSI) systems, Vol.13, No 2, February 2005 [10] J. Luo and N.K. Jha, “Battery-aware static scheduling for distributed real-time embedded systems” Proc. of the 38th Design Automation Conference, Jun. 2001, pp. 444-449 [11] Wendi B. Heinzelman, Anantha P. Chandrakasan and Hari Balakrishnan,” An application-specific protocol architecture for wireless microsensor networks”, IEEE transactions on Wireless Communication, Vol 1, No. 4, October 2002, pp. 660- 670 [12] Pablo Brenner, “A technical tutorial on the IEEE 802.11 protocol”