Heriot-Watt University

advertisement

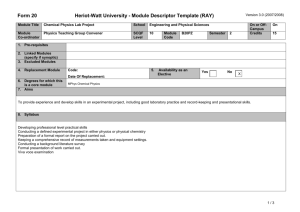

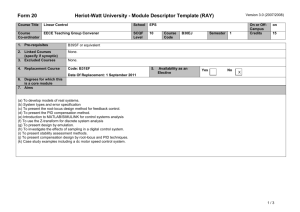

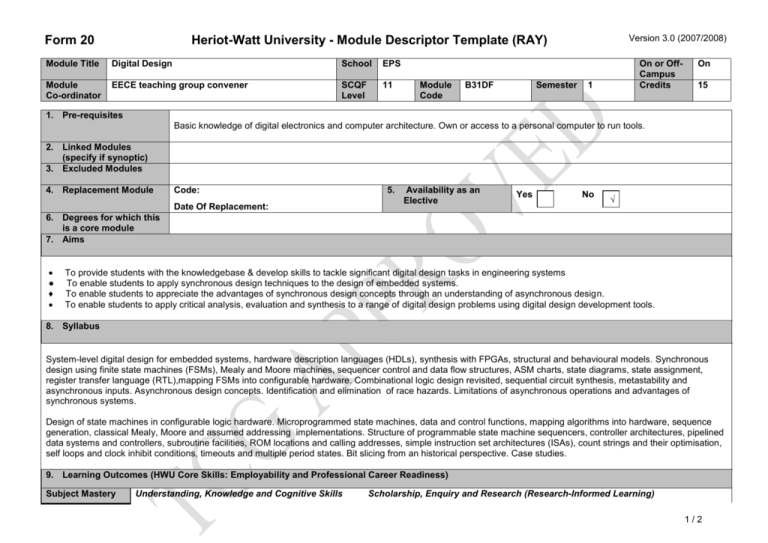

Form 20 Version 3.0 (2007/2008) Heriot-Watt University - Module Descriptor Template (RAY) Module Title Digital Design School EPS Module Co-ordinator EECE teaching group convener SCQF Level 11 Module Code B31DF Semester On or OffCampus Credits 1 On 15 1. Pre-requisites Basic knowledge of digital electronics and computer architecture. Own or access to a personal computer to run tools. 2. Linked Modules (specify if synoptic) 3. Excluded Modules 4. Replacement Module Code: Date Of Replacement: 5. Availability as an Elective Yes No √ 6. Degrees for which this is a core module 7. Aims ● ♦ To provide students with the knowledgebase & develop skills to tackle significant digital design tasks in engineering systems To enable students to apply synchronous design techniques to the design of embedded systems. To enable students to appreciate the advantages of synchronous design concepts through an understanding of asynchronous design. To enable students to apply critical analysis, evaluation and synthesis to a range of digital design problems using digital design development tools. 8. Syllabus System-level digital design for embedded systems, hardware description languages (HDLs), synthesis with FPGAs, structural and behavioural models. Synchronous design using finite state machines (FSMs), Mealy and Moore machines, sequencer control and data flow structures, ASM charts, state diagrams, state assignment, register transfer language (RTL),mapping FSMs into configurable hardware. Combinational logic design revisited, sequential circuit synthesis, metastability and asynchronous inputs. Asynchronous design concepts. Identification and elimination of race hazards. Limitations of asynchronous operations and advantages of synchronous systems. Design of state machines in configurable logic hardware. Microprogrammed state machines, data and control functions, mapping algorithms into hardware, sequence generation, classical Mealy, Moore and assumed addressing implementations. Structure of programmable state machine sequencers, controller architectures, pipelined data systems and controllers, subroutine facilities, ROM locations and calling addresses, simple instruction set architectures (ISAs), count strings and their optimisation, self loops and clock inhibit conditions, timeouts and multiple period states. Bit slicing from an historical perspective. Case studies. 9. Learning Outcomes (HWU Core Skills: Employability and Professional Career Readiness) Subject Mastery Understanding, Knowledge and Cognitive Skills Scholarship, Enquiry and Research (Research-Informed Learning) 1/2 Form 20 Version 3.0 (2007/2008) Heriot-Watt University - Module Descriptor Template (RAY) Module Title Digital Design School EPS Module Co-ordinator EECE teaching group convener SCQF Level 11 ♦ Personal Abilities B31DF Semester 1 On 15 A critical understanding of synchronous digital system design concepts using embedded state machine controllers. Use structured design techniques to produce original designs based on problem specifications.. Use a hardware description language (HDL) for digital design in a typical configurable logic design environment. To be able to analyse and evaluate an advanced asynchronous digital system design. Industrial, Commercial & Professional Practice Module Code On or OffCampus Credits Autonomy, Accountability & Working with Others Communication, Numeracy & ICT Use of tools such as a configurable logic design environment and a microarchitecture simulator. Ability to direct & take responsibility for own work. Undertake critical evaluations of various case study designs. 10. Assessment Methods Method 11. Re-assessment Methods Duration of Exam Weighting (%) Synoptic modules? Method Duration of Exam (if applicable) Coursework Examination 2 (if applicable) 25% 75% Examination 2 12. Date and Version Date of Proposal 30 November 2007 Date of Approval by School Committee Date of Implementation Version Number 1.0 2/2