4-timers

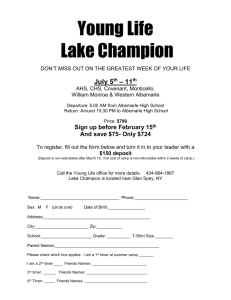

advertisement

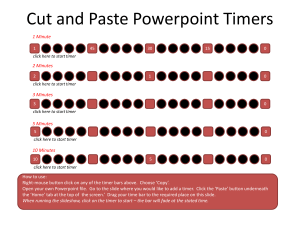

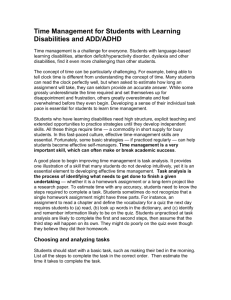

Timers PLC timers are used to activate or de-activate a device after a preset interval of time. Timers have many advantages: I. Settings are easily altered II. Number utilized in circuit easily increased or decreased III. Extremely accurate due to solid-state construction (mechanical devices are relatively accurate) Timers in General The following is a typical depiction of a timer within a ladder diagram. Within the timer block there are three pieces of information: Timer, Preset, and Accumulate. Figure 42. Ladder logic representation of a timer. The timer is identified as Timer T1 and its information is stored in the first available block of the PLC memory. Preset 15 is the value the timer must reach. In this case after the timer is active for 15 seconds the timer has reached the end of its timing period. The maximum value a preset field may hold varies depending on the PLC. For example, a MicroLogix preset field may be limited to a maximum value of 32767 whereas the ControlLogix may have a maximum value of 1,240,000. Accum 0 or the accumulate field increments as the timer cycles through the timing period. The zero value of the accumulate field is its initial value. The accumulate value stops incrementing when it equals the preset value (ie. when the timing period reaches its end). Therefore, when viewing the timer block in the previous figure it can be read as timer T1, when activated, will begin counting from 0 up to 15 seconds in increments of 1 second. The time base of a PLC is the amount the timer increments for each unit of one placed in the Accum field. For instance, our example displays a start time of 0 seconds and an ending time of 15 seconds to 34 the casual observer. However, using the above settings for a timer in the ControlLogix architecture will result in a grand total timing sequence of 15 hundredths of a second. ControlLogix timers, by default, increment timers in 1 millisecond increments. So if a timer must time for 15 seconds then the Preset field should be set for 15,000. (Note that the timing base for timers is not standardized so do not assume every timer will time the same.) Types of Timers There are 3 different types of timers: on-delay timer (TON), off-delay timer (TOF), and retentive timer on (RTO). The most common is the TON which begins counting when the timer input is activated. TON turns on its output once the accumulated and preset values are equal (time delay fuse for dynamite). TOF keeps the output energized for a time period after the timer input is deactivated (garage opener light). RTO operates in the same manner as TON but instead of resetting accumulate to 0, when the input goes low, the RTO will retain its value. If and when the input goes high again the RTO resumes timing. TON The on-delay timer operates such that the timeout period begins when the timer input is true. At the end of the timeout period, the timer outputs a high signal. Since the timer output becomes true sometime after the timer is activated it is referred to as an on-delay timer. Timers utilize three bits for status. The Enable bit (EN) is true while the timer input rung is true and false when the rung is false (matches the input value). The Timer-timing bit (TT) is true whenever the timer accumulate field is changing (ie the timer is timing). If the accumulate field is not changing TT is false. The Done bit (DN) changes state when the accumulate and preset fields are equal for a TON. The exact state DN changes to is dependent on the timer. The following figure shows an on-delay timer that is activated by closing switch A. When activated the timer begins incrementing the accumulated field by the time base setting of 1 second. The timing period continues until accumulated equals the preset field. This triggers the DN bit change from false to true and the TT bit from true to false. 35 If switch A opens during or after the timing period the timer control bits and the accumulated value resets to false (low). Since the accumulated value resets to 0 the timer is referred to as nonretentive. Figure 43. TON timer activating various outputs through its status bits. 4s Figure 44. TON timing diagram demonstrating a 4 and 10 second timing interval. Example applications: snooze button on an alarm clock, alarm system timeout (during disarm procedure) 36 TOF The off-delay timer operates such that as soon as the input is true the DN bit turns true (on) activating any device controlled by the timer. The timeout period begins when the input transitions from true to false. During the timeout period the DN bit continues to output a high signal keeping any device controlled by the timer active. At the conclusion of the timing period the DN bit transitions to false deactivating any connected devices. Since the DN bit activates a device for the timeout period and then turns the device off after the timing period the timer is referred to as an off-delay timer. Figure 45. Timing diagram demonstrating the status of status bits and field values during the activation, timing and reset of a TOF timer. Figure 45 is the timing diagram of a 10 second TOF timer activated by Input transitioning from false to true. This results in EN and DN bits transitioning from false to true. When Input transitions from true to false the TT bit transitions from false to true signifying activation of the timing period. EN, mirroring the state of Input transitions from true to false. DN continues to remain true. Completion of the timing cycle results in the following transitions for TT, DN, EN: true to false, true to false, and remains false, respectively. Note how the accumulate field retains its values after the timing cycle completes and 37 until the Input transitions from false to true. Whenever the Input transitions from false to true the result is a reset of a TOF timer causing the accumulate field to reset to 0. Since it resets to 0 the TOF timer is referred to as non-retentive. Figure 46. Ladder diagram demonstrating TOF timers in parallel configuration. Figure 46 provides an example of activating multiple TOF timers simultaneously. The timing cycle of each timer increases by 5 seconds so that T1, T2, and T3 have timing cycles of 5, 10 and 15 seconds, respectively. This parallel timer design can be used to control a lighting system. Switch SW is triggered by an individual walking past a sensor. This activates all three timers thereby turning on the lights for 3 hallways. The lights in hallway 1 are on for 5 seconds as this is the closest hallway. T2 is the next hallway with T3 being the last hallway to traverse. So as the individual passes through the lights are on but then are automatically turned off in sequence. Example Applications: alarm siren activation, timeout, and reset, garage door opener light 38 Figure 46a. Ladder TON/TOF demonstration ladder. RTO RTO is the acronym for a retentive on-delay timer. An RTO operates in the same manner as a TON except for three differences. Recall that the accumulated field in a TON resets to zero each time the timer input turns false. Compare this to an RTO which stops the timing cycle also when the timer input goes false but the accumulated field retains its current value instead of resetting to zero. When the RTO input is activated again the timing period picks up where it last stopped. If an RTO is activated for 4 seconds and then deactivated, the accumulated field will retain a value of 4. When reactivated the timer continues the timing period from 4 until it reaches the preset value or the timer is again deactivated. An RTO requires a separate command to reset the accumulated field to its initial value. A reset is carried out by applying a true (high) input to the RTR bit of a RTO. The RES bit is the only automatic means of resetting the accumulated value of a retentive timer. Finally an RTO is retentive so if the power fails and is then restored the timer will retain all values present prior to the power failure. 39 Figure 47. Ladder diagram demonstrating the timing and reset operations of an RTO timer. Figure 48. Timing diagram for and RTO timer. Can you spot the errors? 40 Cascading Timers If an event requires a longer time-delay than a timer is capable of providing then multiple timers may be cascaded. That is, one timer completes a timing cycle and then activates another timer. What bit from timer 1 should be used to activate timer 2? 41